本文主要是介绍Marin说PCB之电源完整性PDN(1)--电容位置,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

由于近期乌克兰战事告急,小编的SI同事不得不离开上海回到了自己的家乡去奋斗在战争一线上了,在写这篇文章之前小编我对的这个SI同事表示非常的感谢,因为子曾经曰:三人行必有我师焉, 择其善者而从之,其不善者而改之。不是这个老男人的点拨我也可能对SI那么感兴趣的。

好了,我们言归正传,这期小编我主要想和大家分析的是电源完整行之PDN的设计,当然了这个是一个很大的章节,小编我也不可能用一遍文章就给大家讲明白的。今天我主要讲的是与PDN息息相关的去耦电容位置的一些问题。

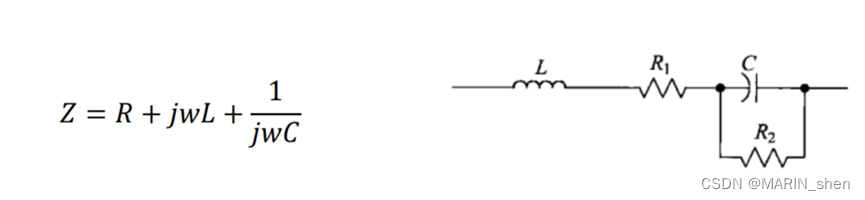

首先大家明白一个概念就是我们的去耦电容的模型并不是理想的,因为从电容的本身来看,实际上我们板子上的电容器不只是纯粹的电容,也有电阻和电感,L是等效串联电感(ESL),来自引线,R2是并联泄漏电阻(或者可以叫做介质损耗电阻),是电介质材料电阻率的函数,R1是等效串联电阻(ESR),是电容器耗散因数的函数; C是本身的电容。所以,电容的阻抗可以表示为:

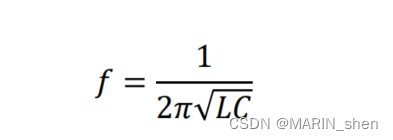

电容的谐振频率可以表示为:

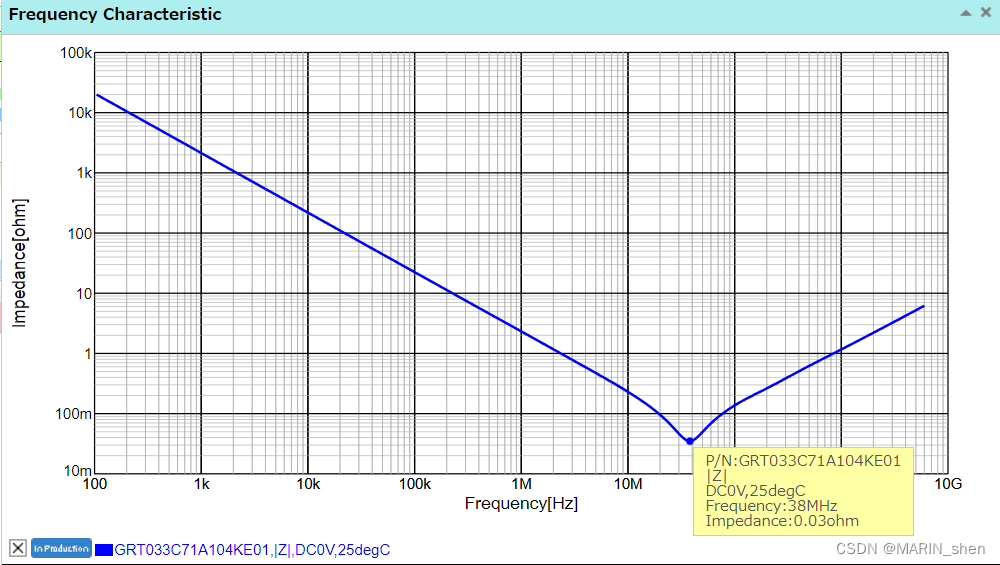

而在谐振时,容抗和感抗相抵为0,此时电容的总阻抗最小,复阻抗相位为0,表现为纯电阻特性,这个点就是电容的自谐振频率。我们随便在MuRaTa官网上下载一颗GRT033C71A104KE01D的0201封装的电容,

如下图所示:在谐振频率左边,电容主要呈容性,在谐振频率右边,电容主要呈感性。我们知道下图所示的整个阻抗曲线呈大V型,只有在谐振频率点附近的阻抗才比较低。所以,实际的去耦电容都有一定的工作频率范围,只有在谐振频率附近,电容才有很好的去耦作用。

以上给大家分析了去耦电容的一些基本常识,接下来我们就要带入实际的项目中去实践了。

小编最近刚刚好也是做一个改版,其实就是改一些SOC芯片上的GPIO信号,其中主要的电源,高速线都是不做改动的,当然这点改动对于我来说确实是小菜一碟的。我投板后在整理文档的时候又好奇的看了一下之前的电源仿真报告,这个不看不知道,一看就吓一跳啊。

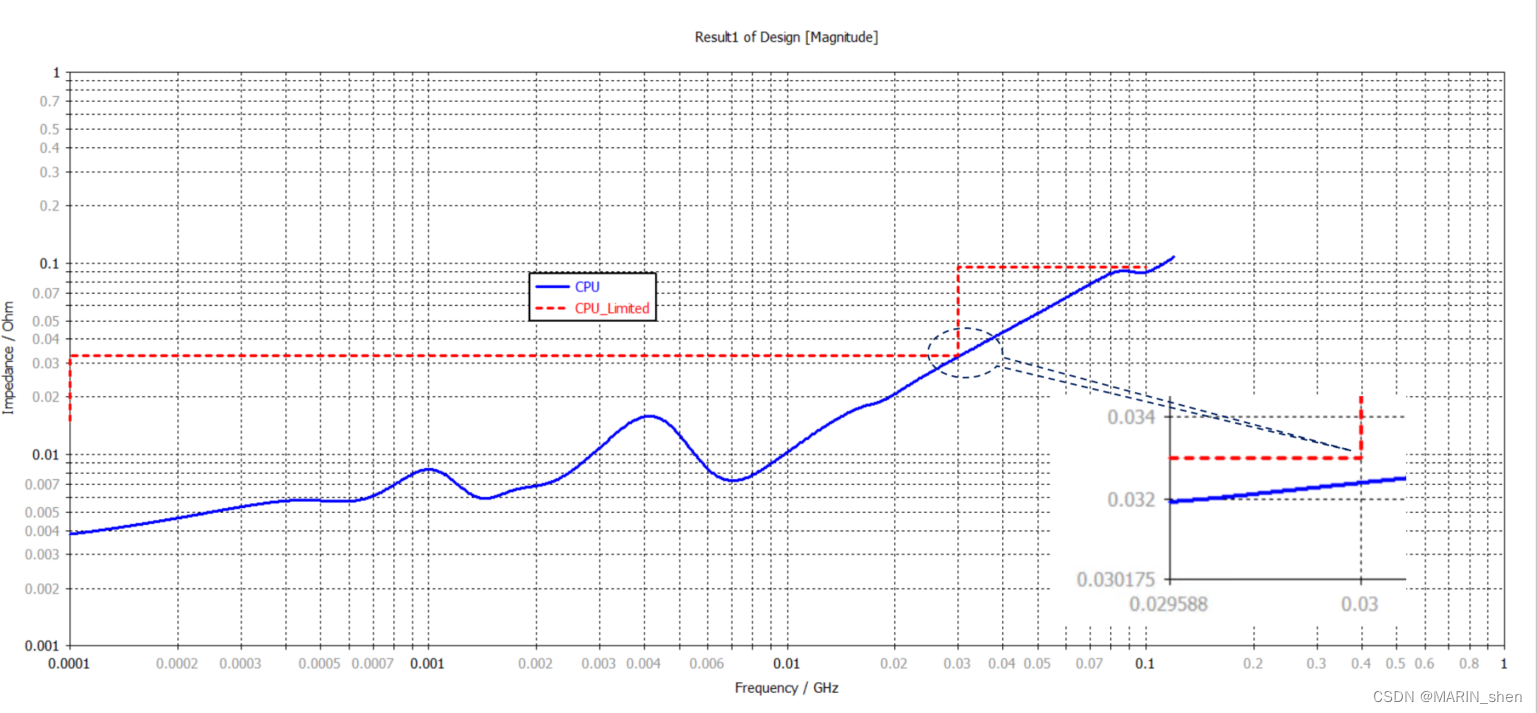

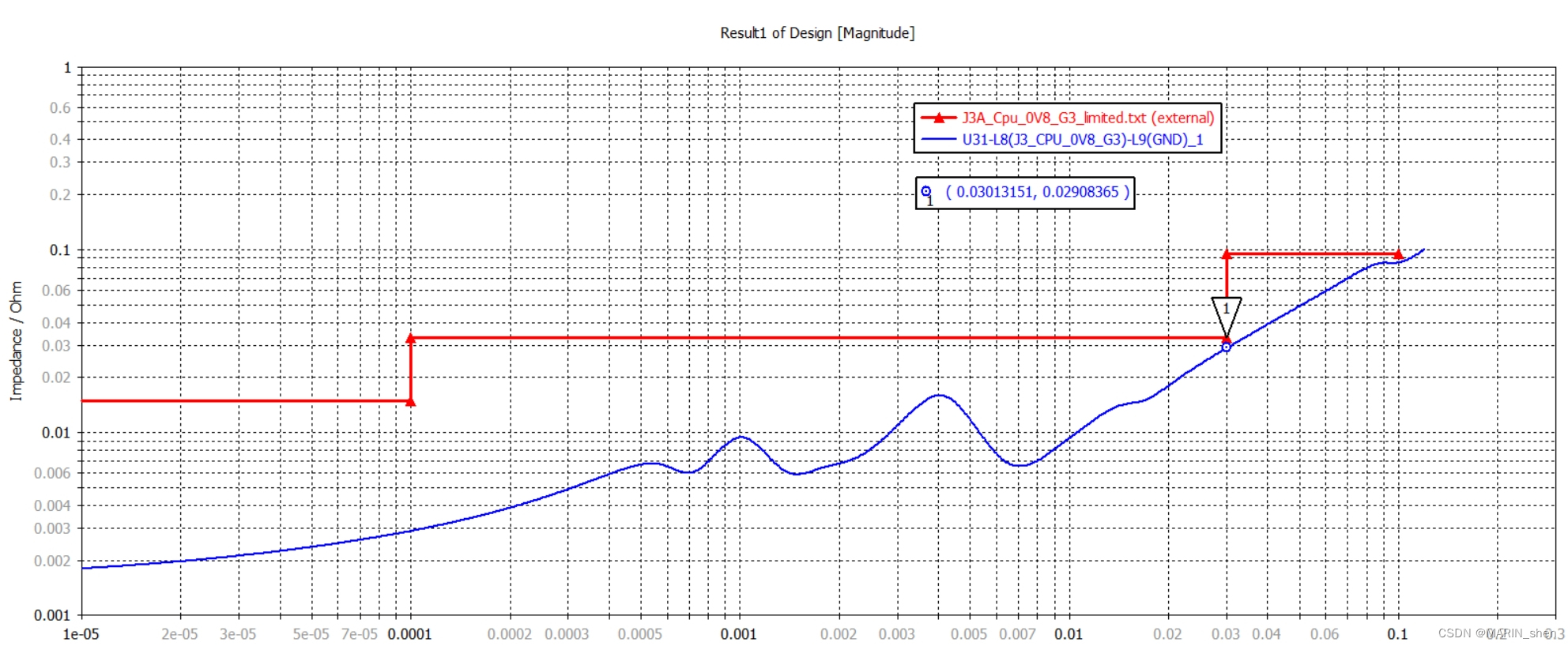

CPU_0V8的这个电源网络的PDN曲线几乎是压着limited曲线了,大概在30Mhz的时候,是很接近限制值33毫欧的,差值大概是1毫欧都不到,几乎是没有裕量了。这个对电源完整性能是有一定风险的。

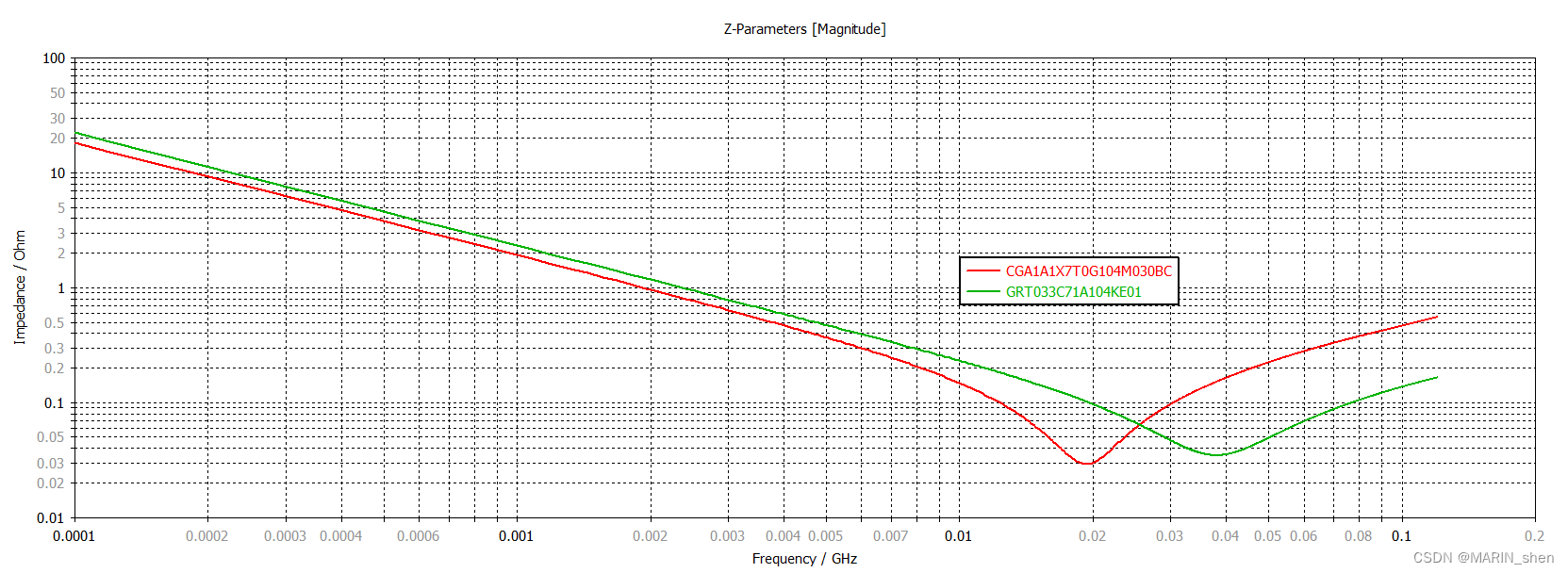

我又立刻查看了这个电容的物料,通过原理图上的查看发现0201封装100nF用的都是TDK的物料。之前我的那个乌克兰同事回国之前就给我讲过相同封装和容值的电容村田(MuRaTa)的比TDK的相对来说效果会更好一些,主要是因为TDK的电容其频谐振点太低,ESL太高,这些因素会导致Layout的优化空间受限,相比而言,GRT033C71A104或其它相等性能的型号是更好的选择。(但是由于这颗电容是呆滞料,在能够满足信号完整性能的前提下还是优选TDK的物料)这个也不是说就不能用TDK家的电容器了,价格和性能有的时候是二者不可兼得的。

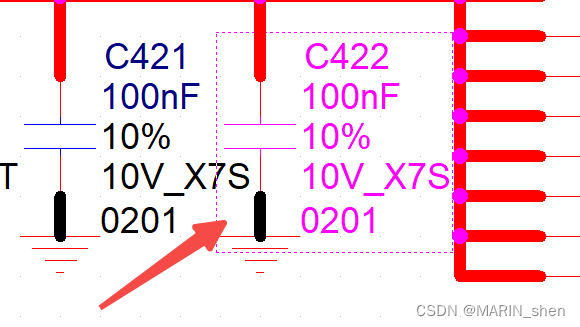

小编我就抱着试试看的态度看下能不能在BGA上的电源管脚附近的背面加一些0201封装的,容值是100nF的电容。(这个时候0201封装电容物料还是TDK的)

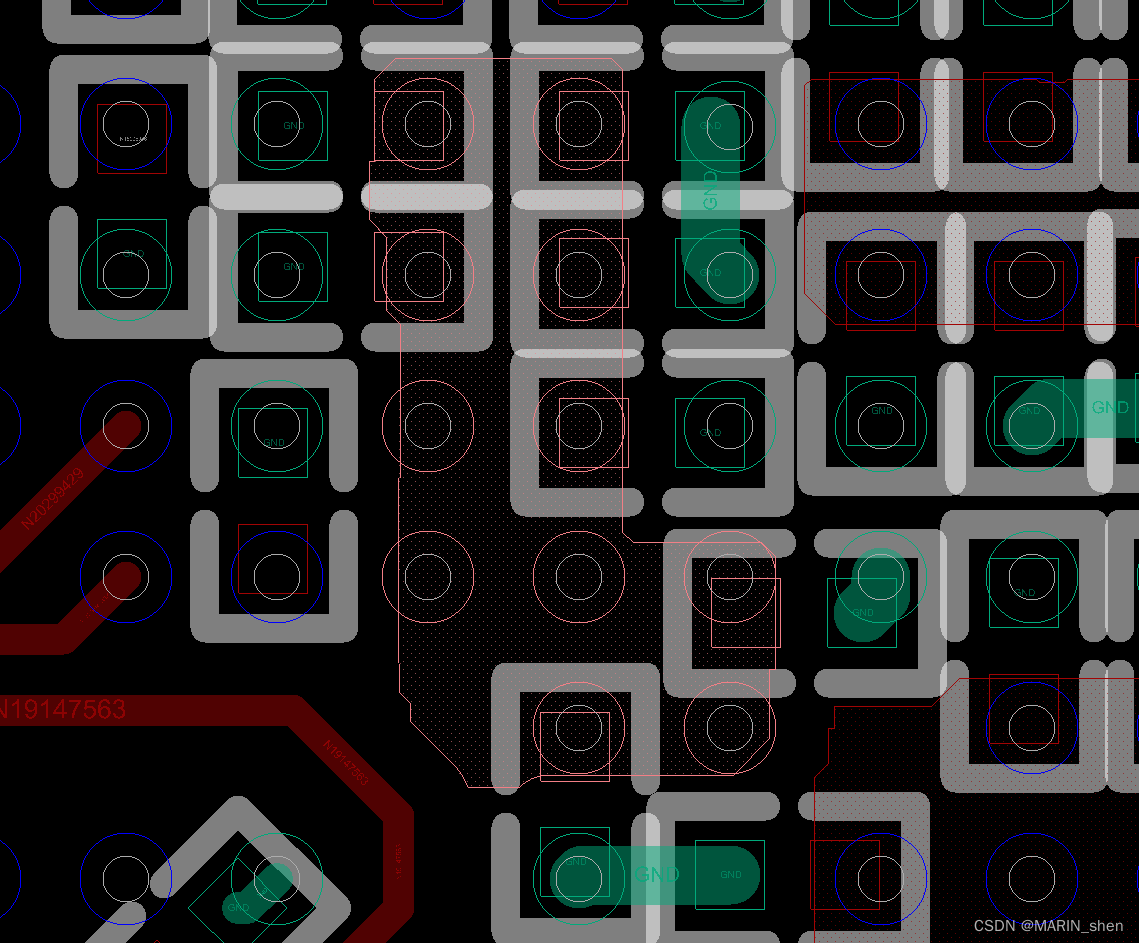

(初始版本)

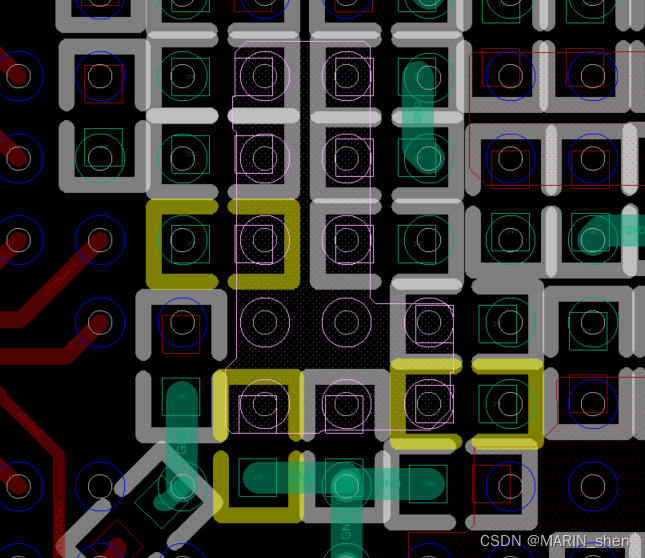

(改善后的版本)

至于为啥是加3个电容而不是一个:多电容并联使用,在PCB设计中非常常见,单一去耦电容不能提供一个足够低的电感值,因此,高频去耦问题的实际解决方法依赖于使用多个去耦电容,这个前提是布局有空间的前提下。然后接着在电源信号PIN脚附近加了一个电源孔,一个GND孔。

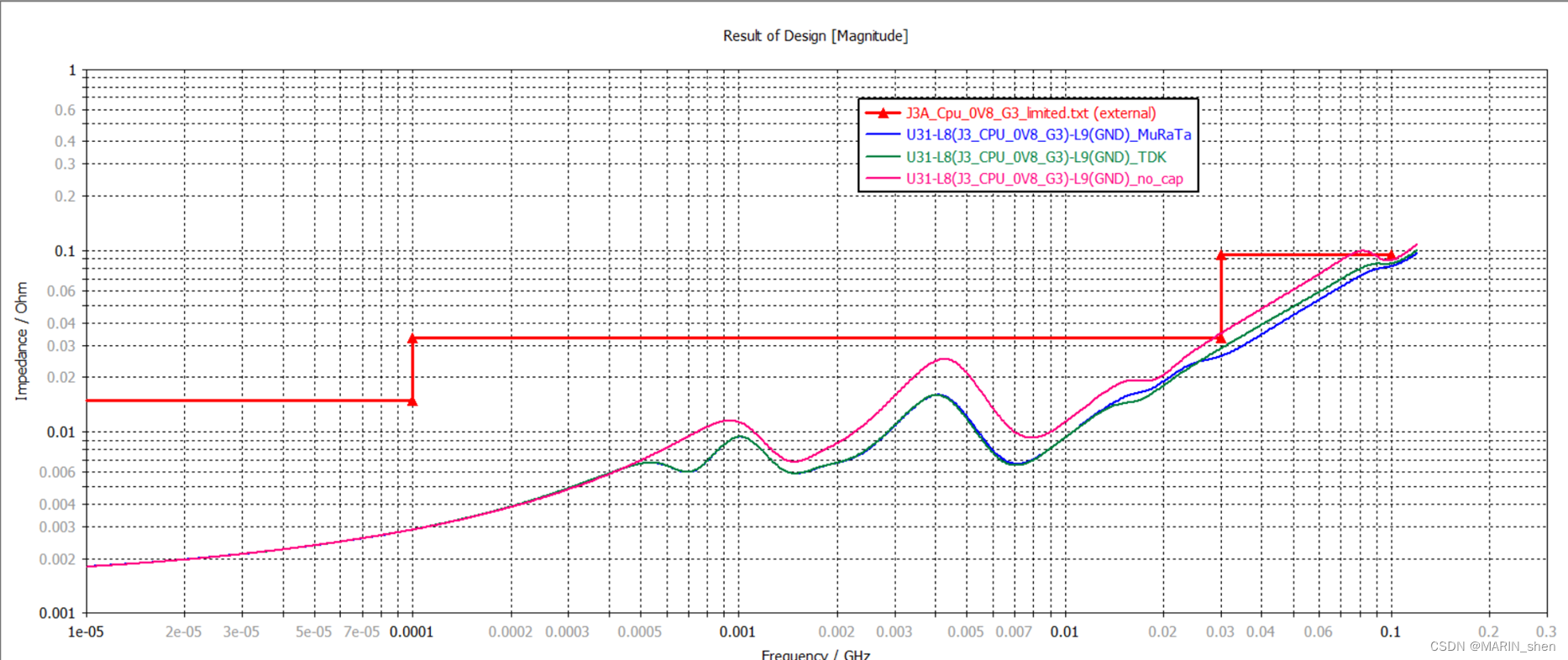

改善后的仿真如下图所示:

从上面的PDN曲线图可知:曲线限制值在频段是30MHz的时候是33毫欧,我们30MHz的频段曲线对应的是29毫欧,差值大概是4毫欧左右,比之前的压线过的情况相对好一些,(当然了这个改善的前提是不影响其他电源网络的PDN的前提下做的)

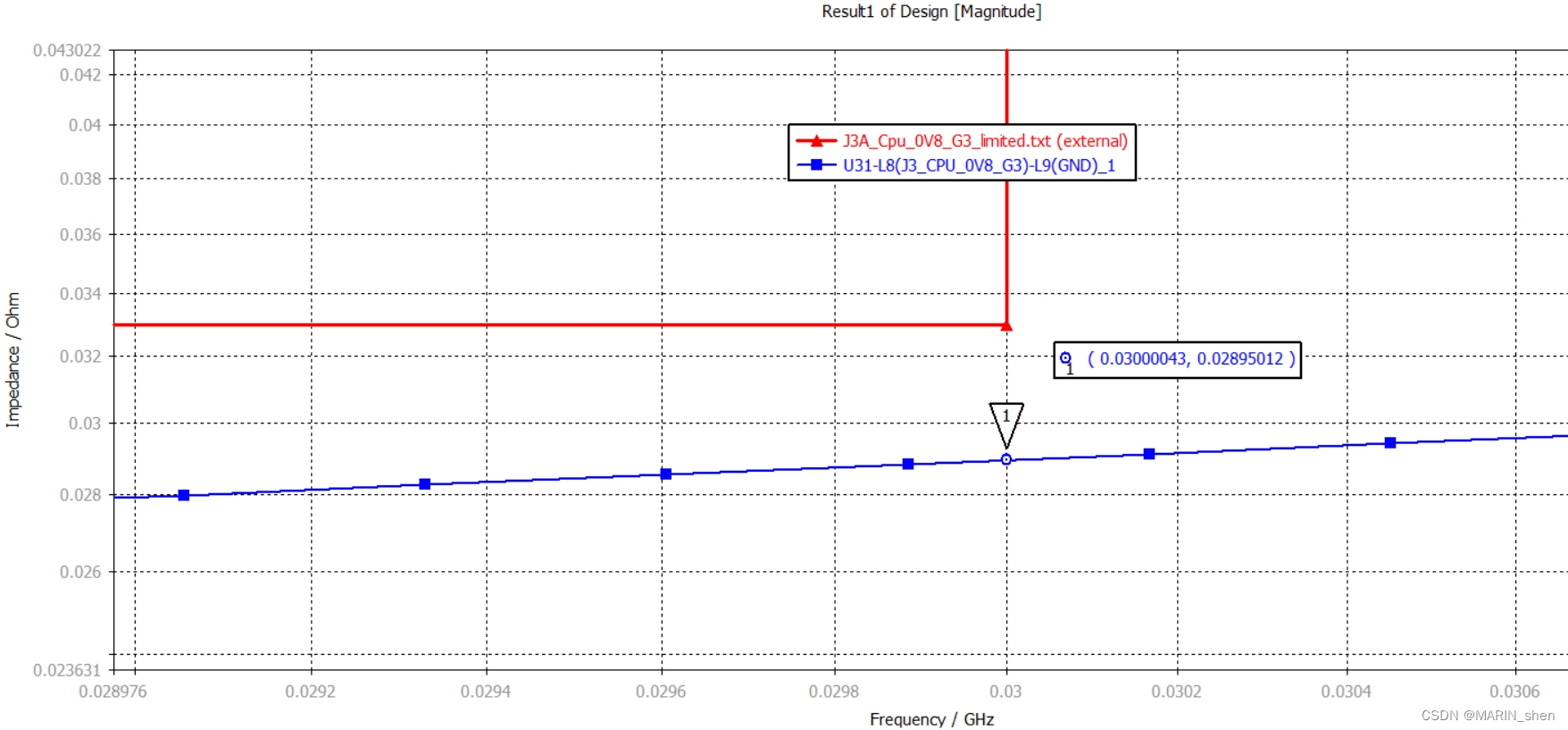

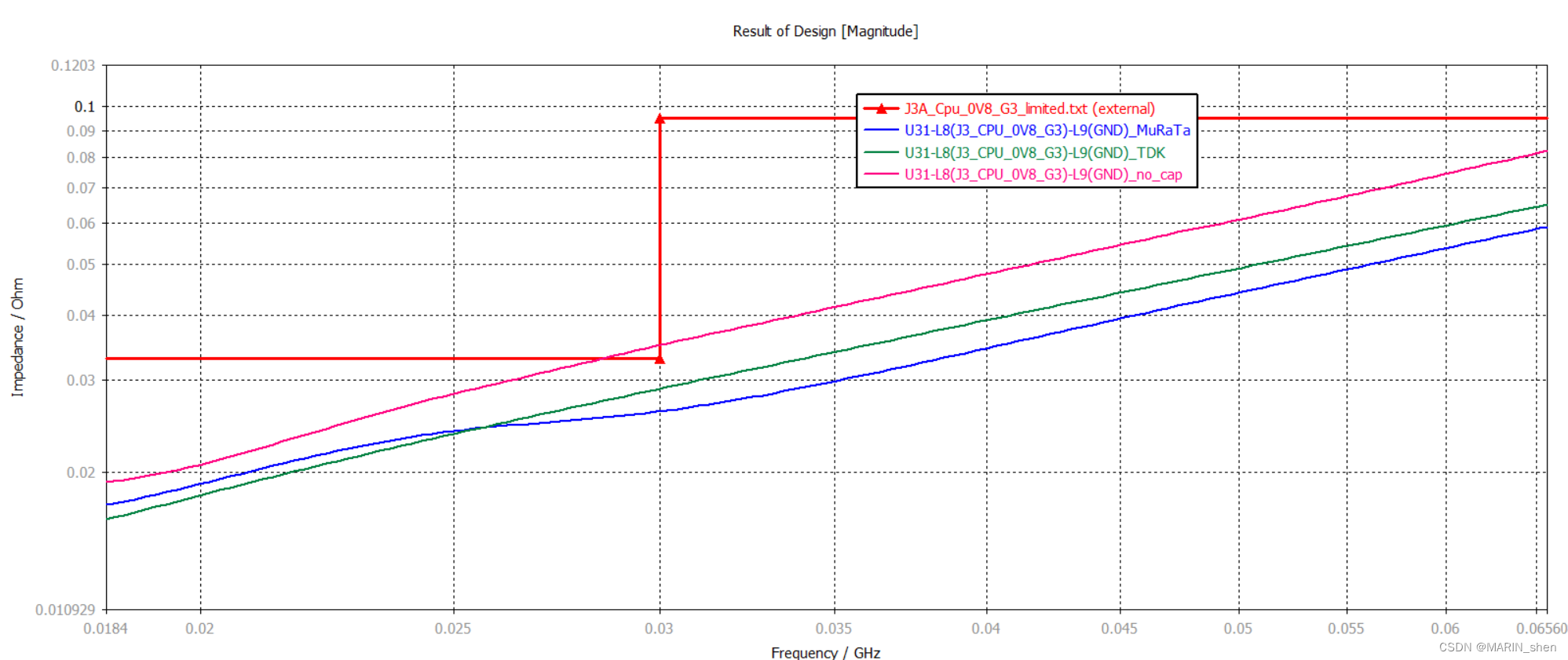

小编我心中突然冒出来一个想法就是:如果说我们的项目上是没有呆滞料这个硬性条件的话,把新加三个TDK的电容都换成Murata的话,实际的效果如何呢?从理论分析肯定是裕量比现在的还有好一些(前面小编已经对比过这两课物料的PDN曲线图),具体的我们还是以仿真结果为准:

从上面的图示可知:3颗电容物料替换成Murata后,PDN的仿真结果比TDK的差了3毫欧左右,这个值你直接单独来看的话确实时改善不是很多,但是对于那些裕量本身就不是很充足的电源网络改善还是蛮多的。(需不需要替换其实看你本身的电源网络的PDN裕量了,裕量本身就很多的话,可以不做修改的,不足的就替换成Murata 封装的比较好一些的,就拿上图来看,频段在1MHz-2MHz之间电源网络的PDN裕量还是挺足的,这个频段所对应的去耦电容就不需要增加或者是替换成Murata的电容器了。)

若是只加一个电源孔和一个GND孔,三颗TDK或者是Murata的电容空贴的情况下来看下实际效果图:

上图明显可以看出来只是加了电源和GND的过孔是不仅不能解决PDN曲线压线过的这个问题的,好像还加剧了情况。之前初始版本还有一些裕量,现在是直接超过了限制值曲线了。主要原因还是因为:高的过孔分布电感,会抵消部分电容的去耦性能,实际情况如下图所示。

有的时候就是这个样子的,鱼与熊掌不可兼得,具体问题还是需要具体分析的,以上就是这次的文章分享,若有不足之处还望路过的朋友们一起指点迷津,好了,我们下期话题不见不散,还有就是大家若是有与PCB设计相关的一些问题也可以在评论区写下留言,大家一起探讨学习一下。

这篇关于Marin说PCB之电源完整性PDN(1)--电容位置的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!