本文主要是介绍STA:时序检查,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

- 1. reg2reg

- 2. input2reg

- 3. reg2output

- 4. input2output

- 4. 时钟门控检查

介绍静态时序分析(Static Timing Analysis, STA)基本原理和过程。

基于标准单元库中触发器的特性,和配置好的STA环境,针对设计中综合之后的模块,对触发器建立时间和保持时间进行检查,包括最差情况的慢速条件和最佳情况的快速条件。如果而时序检查通过就为时序收敛,否则就为时序违例,即可能出现亚稳态现象。

通常,最差情况的慢速条件对于建立时间检查很关键,而最佳情况的快速条件对于保持时间检查很关键。

本文中的SDC指令可在STA环境中查看,标准单元库的SDF可在STA标准单元中查看

STA要分析的时序路径有如下四种

1. reg2reg

第一种是芯片内部触发器到触发器的路径。

发起触发器到捕获触发器路径如下:

参数定义:

● T c l k 2 U F F 0 T_{clk2UFF0} Tclk2UFF0:上升沿从时钟CLKM传输到UFF0的CK引脚的时钟树延迟。

时钟树综合之前,该值通过下方SDC指定

set_clock_latency 0.8 [get_clocks CLKM]

综合之后,则会根据综合后实际的线路计算延迟。

如果还存在时钟缓冲器(CKBUF),则会根据CKBUF的输入过渡时间(即CLKM的过渡时间)和CKBUF的输出负载计算CKBUF的延迟。其中CLKM的过渡时间同过下方SDC指定

set_clock_transition -rise 0.3 [get_clocks CLKM]

set_clock_transition -fall 0.45 [get_clocks CLKM]

CKBUF的输出负载则通过标准单元库的SDF指定。

● T C K 2 Q U F F 0 T^{UFF0}_{CK2Q} TCK2QUFF0:数据从UFF0的D引脚到Q引脚的传播延迟

取决于标准单元库触发器的SDF描述。

● T U F F 02 U F F 1 T_{UFF02UFF1} TUFF02UFF1:数据从UFF0的Q引脚,经过一系列组合逻辑元件,最终到达UFF1的D引脚的时间

取决于综合后两触发器之间的组合逻辑,组合逻辑延迟通过标准单元库的SDF指定。

● T c l k 2 U F F 1 T_{clk2UFF1} Tclk2UFF1:上升沿从时钟CLKM传输到UFF1的CK引脚的时间

该值与 T c l k 2 U F F 0 T_{clk2UFF0} Tclk2UFF0确定方式相同。

● T c l k T_{clk} Tclk:时钟CLKM周期,该时钟域电路工作频率

该值通过下方SDC指定

create_clock -period 10 [get_ports CLKM]

● T s e t u p _ u n c e r t a i n T_{setup\_uncertain} Tsetup_uncertain:时钟CLKM建立时间不确定度,即预期时钟沿提前一段时间。

该值通过下方SDC指定

set_clock_uncertainty -setup 0.3 [get_clocks CLKM]

● T h o l d _ u n c e r t a i n T_{hold\_uncertain} Thold_uncertain:时钟CLKM保持时间不确定度,即预期时钟沿延后一段时间。

该值通过下方SDC指定

set_clock_uncertainty -hold 0.3 [get_clocks CLKM]

● T s e t u p U F F 1 T^{UFF1}_{setup} TsetupUFF1:UFF1的建立时间。

该值通过标准单元库中触发器的SDF指定。

● T s e t u p _ s l a c k U F F 02 U F F 1 T^{UFF02UFF1}_{setup\_slack} Tsetup_slackUFF02UFF1:路径UFF0-UFF1的建立时间裕度。为待计算量,大于零表示建立时间满足。

● T h o l d U F F 1 T^{UFF1}_{hold} TholdUFF1:UFF1的保持时间。

该值通过标准单元库中触发器的SDF指定。

● T h o l d _ s l a c k U F F 02 U F F 1 T^{UFF02UFF1}_{hold\_slack} Thold_slackUFF02UFF1:路径UFF0-UFF1的保持时间裕度

1.1. 建立时间 T s e t u p T_{setup} Tsetup检查

建立时间要求触发器输入的数据D必须在采样时钟沿CK到来捕获触发器之前保持稳定一段时间,以保证CK时钟沿能够正确采样到数据。

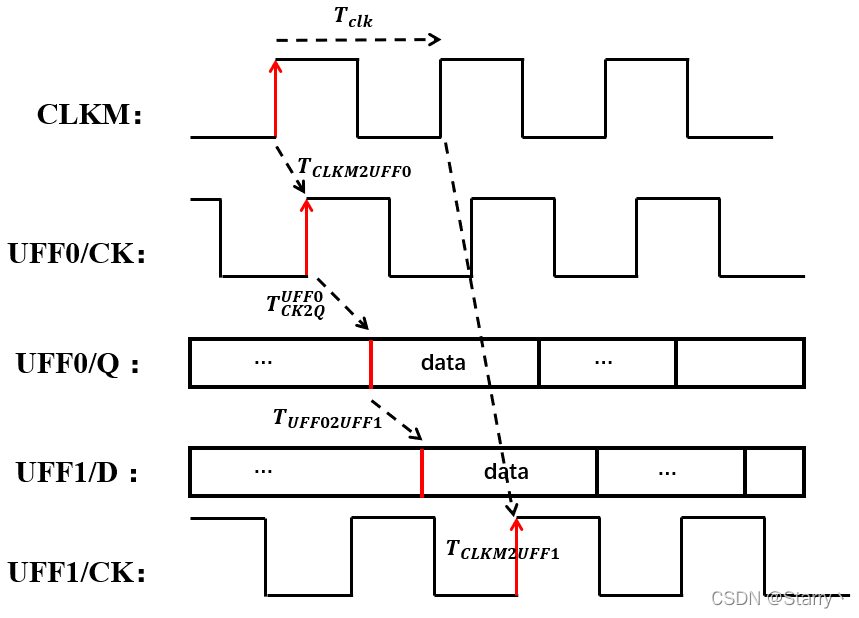

当CLKM的上升沿到来时,各端口的时序图如下所示:

需要说明的是,平时也仿真工具看到的波形,其实主要是CLKM和UFF0/Q这两项,而且posedge CLKM与UFF0/Q会对齐,其实就是忽略了很多内部的延迟。

以CLKM的红线为时间原点,对捕获触发器进行STA

● 数据实际到达UFF1/D端的时间(Arrival Time): T c l k 2 U F F 0 + T C K 2 Q U F F 0 + T U F F 02 U F F 1 T_{clk2UFF0}+T^{UFF0}_{CK2Q}+T_{UFF02UFF1} Tclk2UFF0+TCK2QUFF0+TUFF02UFF1

● UFF1/D端新信号应该到达的时间(Required Time): T c l k − T s e t u p _ u n c e r t a i n + T c l k 2 U F F 1 − T s e t u p U F F 1 T_{clk}-T_{setup\_uncertain}+T_{clk2UFF1}-T^{UFF1}_{setup} Tclk−Tsetup_uncertain+Tclk2UFF1−TsetupUFF1

所以路径UFF0-UFF1中UFF1的建立时间裕度为:

0 < T s e t u p _ s l a c k U F F 02 U F F 1 = R e q u i r e d T i m e − A r r i v a l T i m e = ( T c l k − T s e t u p _ u n c e r t a i n + T c l k 2 U F F 1 − T s e t u p U F F 1 ) − ( T c l k 2 U F F 0 + T C K 2 Q U F F 0 + T U F F 02 U F F 1 ) (1.1) 0<T^{UFF02UFF1}_{setup\_slack}=Required Time-ArrivalTime \\\ =(T_{clk}-T_{setup\_uncertain}+T_{clk2UFF1}-T^{UFF1}_{setup})-(T_{clk2UFF0}+T^{UFF0}_{CK2Q}+T_{UFF02UFF1}) \\\ \tag{1.1} 0<Tsetup_slackUFF02UFF1=RequiredTime−ArrivalTime =(Tclk−Tsetup_uncertain+Tclk2UFF1−TsetupUFF1)−(Tclk2UFF0+TCK2QUFF0+TUFF02UFF1) (1.1)

其中, T s e t u p _ s l a c k U F F 02 U F F 1 T^{UFF02UFF1}_{setup\_slack} Tsetup_slackUFF02UFF1为正说明时序检查通过。

input2reg型、reg2output型和input2output型的建立时间裕度公式均可看作是reg2reg型建立时间裕度公式 ( 1.1 ) (1.1) (1.1)的变种。

最长路径

如果UFF0/Q到UFF1/D有多个路径呢,从公式 ( 1.1 ) (1.1) (1.1)可以看出,不同的UFF0/Q到UFF1/D路径中除了 T U F F 02 U F F 1 T_{UFF02UFF1} TUFF02UFF1其他量均是相同的。所以UFF1的建立时间收敛将取决于 m a x ( T U F F 02 U F F 1 ) max(T_{UFF02UFF1}) max(TUFF02UFF1)

1.2. 保持时间 T h o l d T_{hold} Thold检查

保持时间要求触发器输入的数据D必须在采样时钟沿CLKM到达捕获触发器之后保持稳定一段时间,以保证触发器能够正确输出数据。

或者说采样时钟沿CLKM到达捕获触发器之后,捕获触发器D端数据稳定一段时间之后再更新。

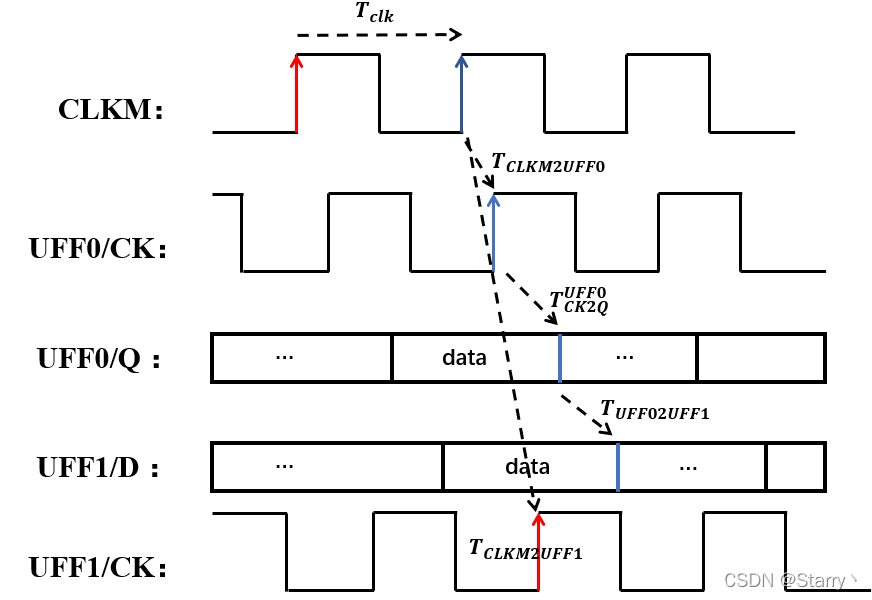

当CLKM的上升沿到来时,各端口的时序图如下所示:

还以CLKM的红线为时间原点

● UFF1/D端旧数据实际被更新的时间(Arrival Time): T c l k + T h o l d _ u n c e r t a i n + T c l k 2 U F F 0 + T C K 2 Q U F F 0 + T U F F 02 U F F 1 T_{clk}+T_{hold\_uncertain}+T_{clk2UFF0}+T^{UFF0}_{CK2Q}+T_{UFF02UFF1} Tclk+Thold_uncertain+Tclk2UFF0+TCK2QUFF0+TUFF02UFF1

UFF1/D端旧数据实际被更新的时间 就等价于 新数据实际到达UFF1/D端的时间

● UFF1/D端旧数据应该更新的时间(Required Time): T c l k + T h o l d _ u n c e r t a i n + T c l k 2 U F F 1 + T h o l d U F F 1 T_{clk}+T_{hold\_uncertain}+T_{clk2UFF1}+T^{UFF1}_{hold} Tclk+Thold_uncertain+Tclk2UFF1+TholdUFF1

所以路径UFF0-UFF1中UFF1的保持时间裕度为:

0 < T h o l d _ s l a c k U F F 02 U F F 1 = A r r i v a l T i m e − R e q u i r e d T i m e = ( T c l k 2 U F F 0 + T C K 2 Q U F F 0 + T U F F 02 U F F 1 ) − ( T c l k 2 U F F 1 + T h o l d U F F 1 ) (1.2) 0<T^{UFF02UFF1}_{hold\_slack}=ArrivalTime-Required Time \\\ =(T_{clk2UFF0}+T^{UFF0}_{CK2Q}+T_{UFF02UFF1})-(T_{clk2UFF1}+T^{UFF1}_{hold}) \\\ \tag{1.2} 0<Thold_slackUFF02UFF1=ArrivalTime−RequiredTime =(Tclk2UFF0+TCK2QUFF0+TUFF02UFF1)−(Tclk2UFF1+TholdUFF1) (1.2)

其中, T h o l d _ s l a c k U F F 02 U F F 1 T^{UFF02UFF1}_{hold\_slack} Thold_slackUFF02UFF1为正说明时序检查通过。可以看出保持时间裕度与时钟周期无关。

input2reg型、reg2output型和input2output型的保持时间裕度公式均可看作是reg2reg型保持时间裕度公式 ( 1.2 ) (1.2) (1.2)的变种。

最短路径

与最长路径类似,从公式 ( 1.2 ) (1.2) (1.2),如果UFF0/Q到UFF1/D有多个组合路径,那么UFF1的保持时间收敛将取决于 m i n ( T U F F 02 U F F 1 ) min(T_{UFF02UFF1}) min(TUFF02UFF1)

1.3. 亚稳态原因

知道了亚稳态的本质,经过了STA分析,那么亚稳态的原因非常容易得出。

( 1.1 ) (1.1) (1.1)和 ( 1.2 ) (1.2) (1.2)两个式子中

T s e t u p U F F 1 T^{UFF1}_{setup} TsetupUFF1、 T h o l d U F F 1 T^{UFF1}_{hold} TholdUFF1和 T C K 2 Q U F F 0 T^{UFF0}_{CK2Q} TCK2QUFF0是触发器自身特性无法改变

T c l k T_{clk} Tclk是同步时钟,与电路无关

剩余的量就是引起同步电路亚稳态的原因了

组合逻辑: T U F F 02 U F F 1 T_{UFF02UFF1} TUFF02UFF1

当其他量保持不变时,可以发现这个东西不能太大也不能太小。

● 如果 T U F F 02 U F F 1 T_{UFF02UFF1} TUFF02UFF1太大,建立时间不满足,其实就是UFF1/CK要采样啦,UFF1/D还没稳定呢

● 如果 T U F F 02 U F F 1 T_{UFF02UFF1} TUFF02UFF1太小,保持时间不满足,其实就是UFF1/Q还没驱动完,UFF1/D的值就变了

时钟偏斜(Clock Skew): T c l k 2 U F F 0 − T c l k 2 U F F 1 T_{clk2UFF0}-T_{clk2UFF1} Tclk2UFF0−Tclk2UFF1

看公式就知道时钟偏斜是啥意思了,就是时钟信号到达不同触发器的时间不同

这个东西在同步电路中必然存在

● 如果CLKM到达UFF0先于UFF1,即 T c l k 2 U F F 0 − T c l k 2 U F F 1 < 0 T_{clk2UFF0}-T_{clk2UFF1} <0 Tclk2UFF0−Tclk2UFF1<0,保持时间不满足,其实就是UFF1/D的变化提前了

● 如果CLKM到达UFF0晚于UFF1,即 T c l k 2 U F F 0 − T c l k 2 U F F 1 > 0 T_{clk2UFF0}-T_{clk2UFF1}>0 Tclk2UFF0−Tclk2UFF1>0,建立时间不满足,其实就是UFF1/CK采样提前了

还有个时钟抖动(Clock Jitter)的概念,是指不同时期时钟周期长短不一

2. input2reg

STA:时序检查 - input2reg型

3. reg2output

STA:时序检查 - reg2output型

4. input2output

STA:时序检查 - input2output型

4. 时钟门控检查

这篇关于STA:时序检查的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!