本文主要是介绍【计算机组成原理】单周期CPU设计与实现-十条指令CPU,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

单周期CPU设计与实现

合肥工业大学 计算机组成原理 实验五 单周期CPU设计与实现——十条指令CPU

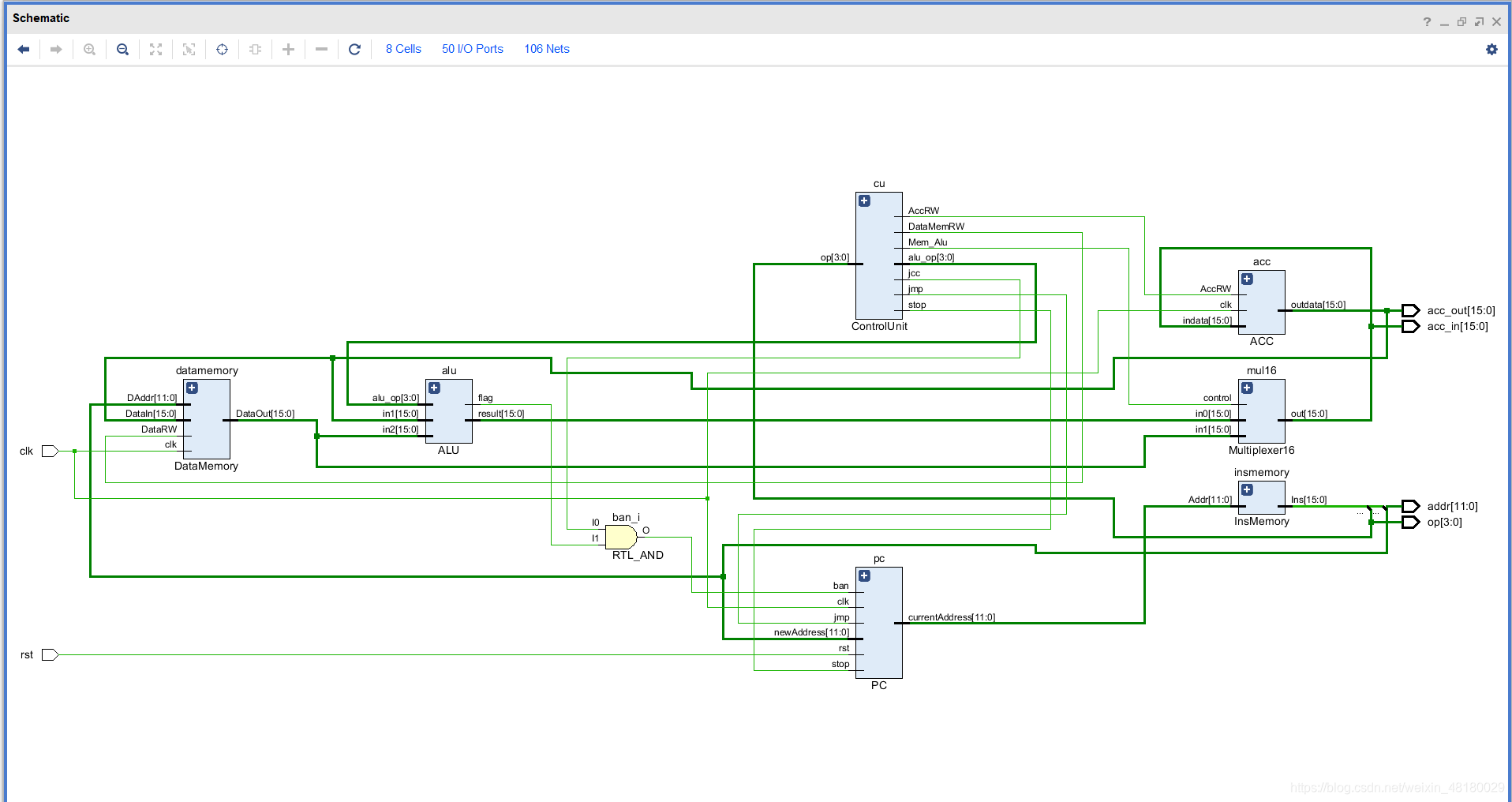

自己在图上画出来指令的执行过程就会很清晰明了。首先确认有哪些模块,PC,指令存储器,CU,ACC,ALU,数据存储器,像多路选择器,符号位扩展模块都是根据指令后来添加的。再确认模块的输入信号和输出信号。当然,我也一下子无法把每个模块的输入信号和输出信号的数量确定好,这是一个增量过程,根据不同的指令变化而变化,但是大致还是能确定一些的。

然后,在纸上画出每条指令的执行过程。比如CLA指令,一条指令从指令存储器出来,操作码送入CU,剩余的部分根据指令需求送入不同模块。从CU出来的是ACC的写信号,也有alu的操作控制信号。下一个周期有效。ACC中的数据会输入到ALU中,从ALU中的计算的结果还要回写到ACC中。剩余的非访存指令皆是如此。

PC模块

module PC(clk,rst,stop,//停机信号jmp,//无条件跳转信号,为1跳转ban,//有条件条跳转信号,为1跳转newAddress,currentAddress);

input clk,rst,stop,jmp,ban;

input[11:0]newAddress;

output reg[11:0] currentAddress;reg state;

initial beginstate = 1; currentAddress = 0;

end

always@(posedge clk or negedge rst)beginif(stop)state = 0; if(!rst)currentAddress = 0;else beginif(state)beginif(!jmp && !ban)currentAddress = currentAddress + 1;else beginif(jmp)currentAddress = newAddress;if(ban)currentAddress = currentAddress+newAddress;endendend

end

endmodule

InsMemory模块

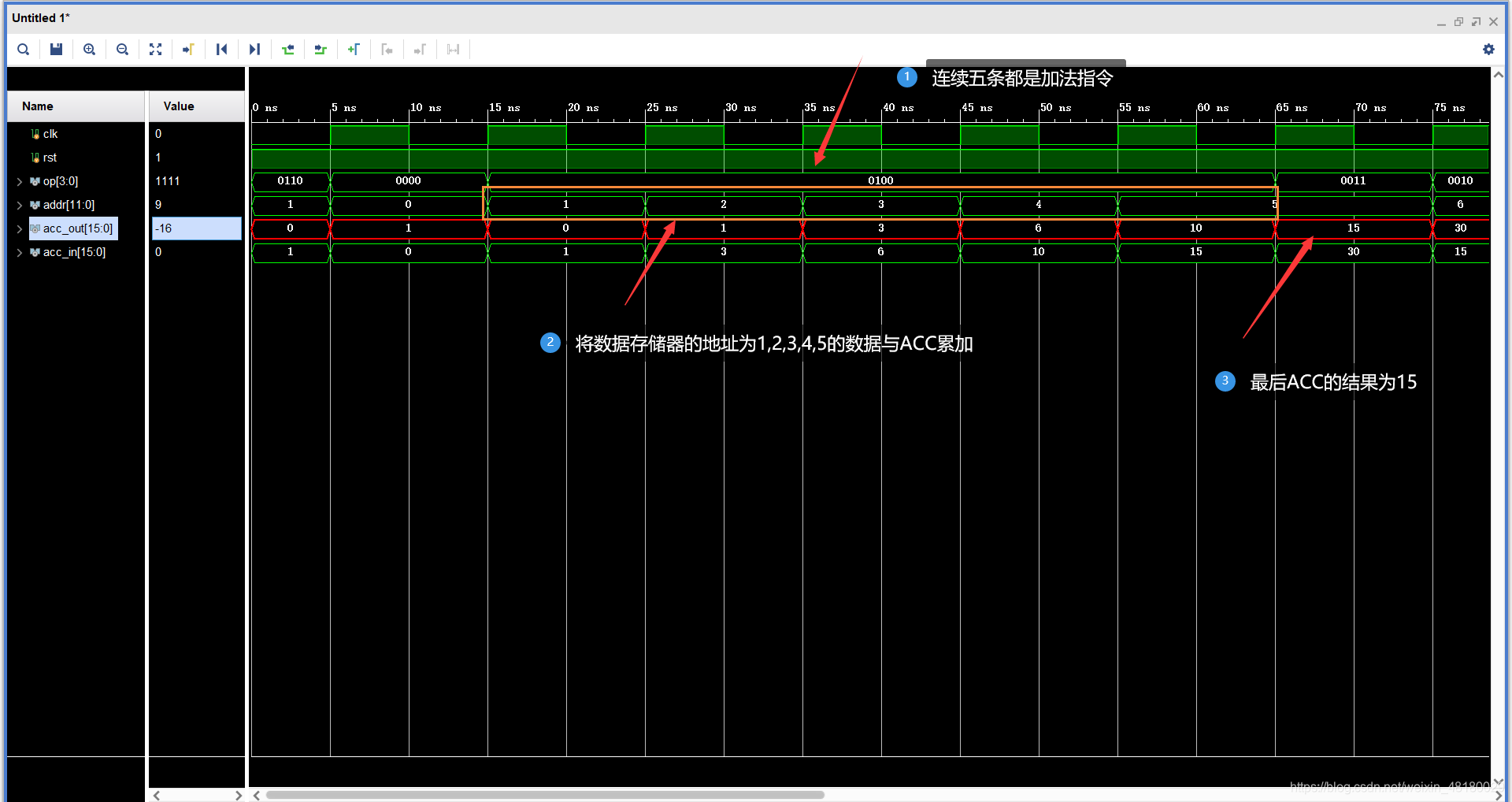

本来想通过条件跳转实现一个从1+2+3+…+n的程序的,但是由于判断条件在ACC,结果也放到ACC中,因此就无法实现。如果再写一个寄存器堆的话,就可以实现了。再写个寄存器堆工作量又要上升不少,所以采取很笨的方法,多写几条加法指令就行了。

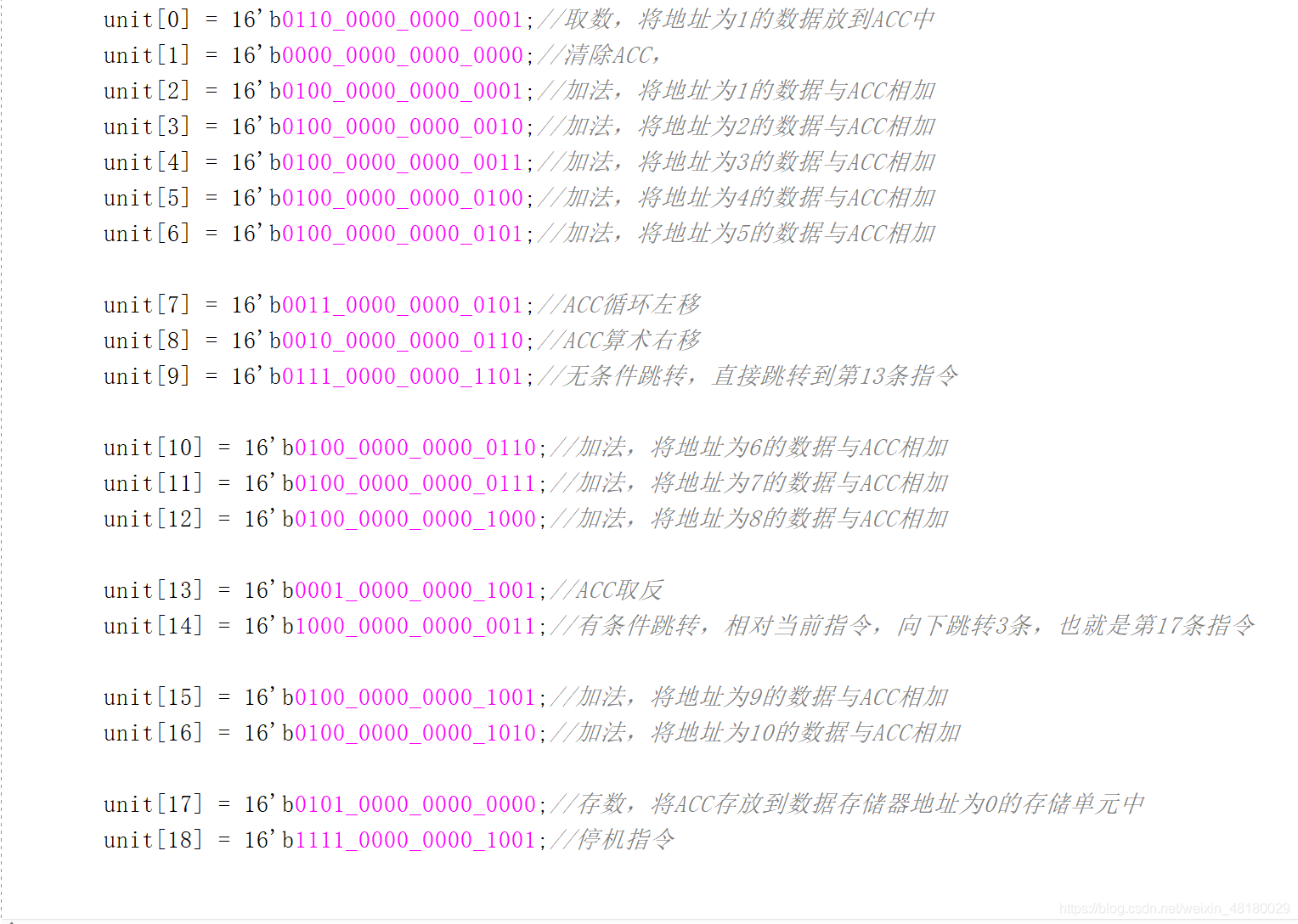

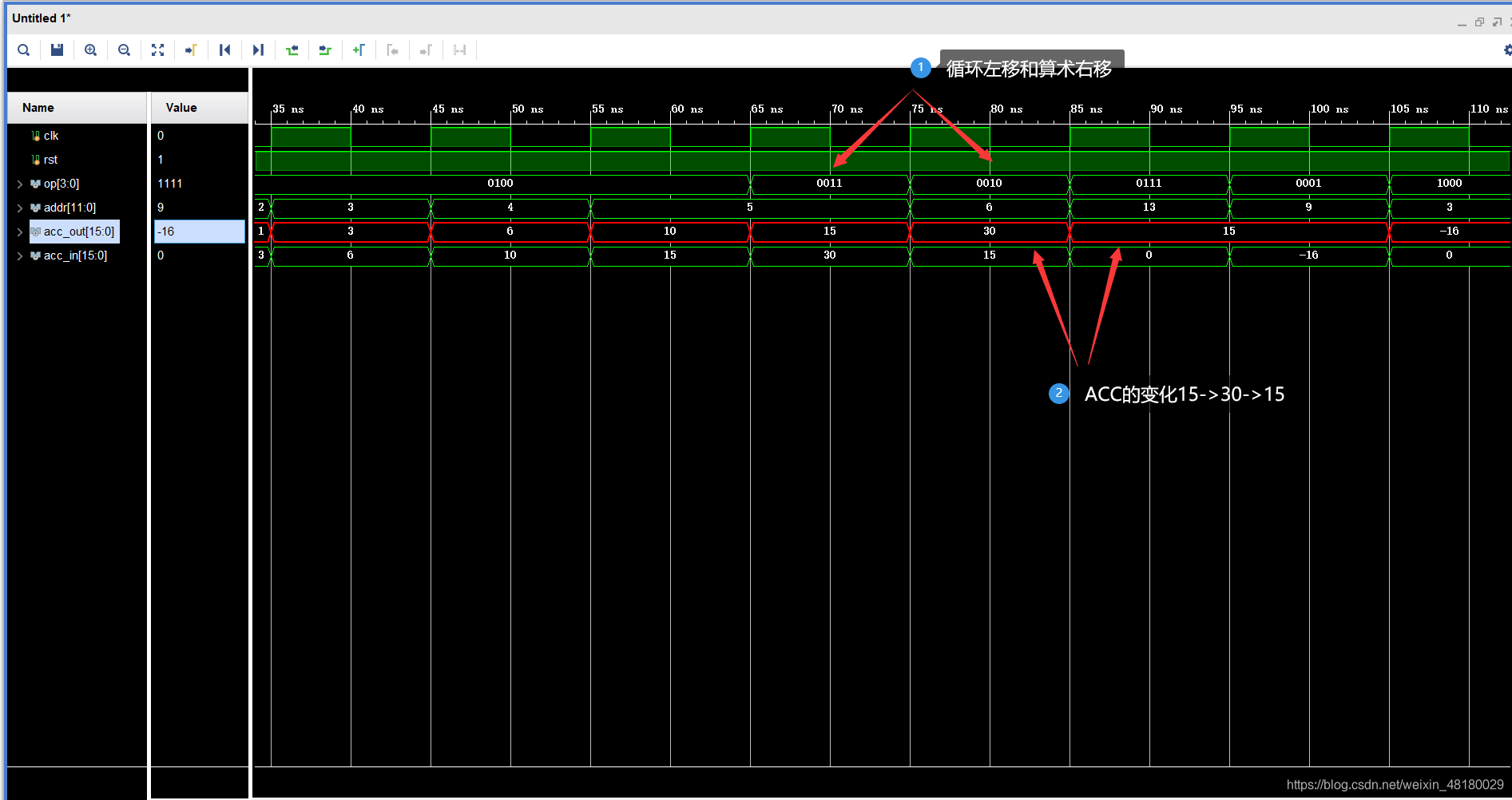

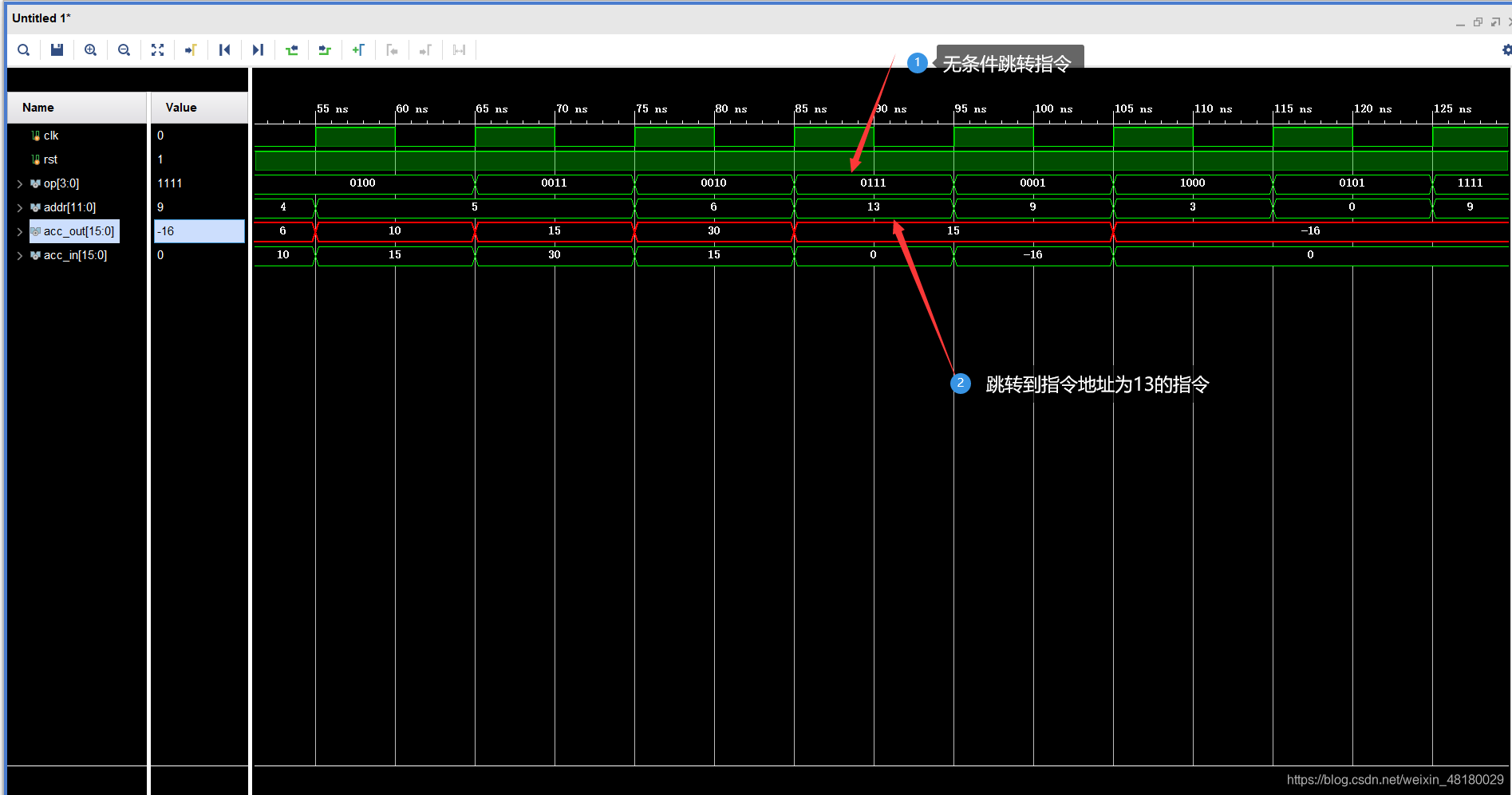

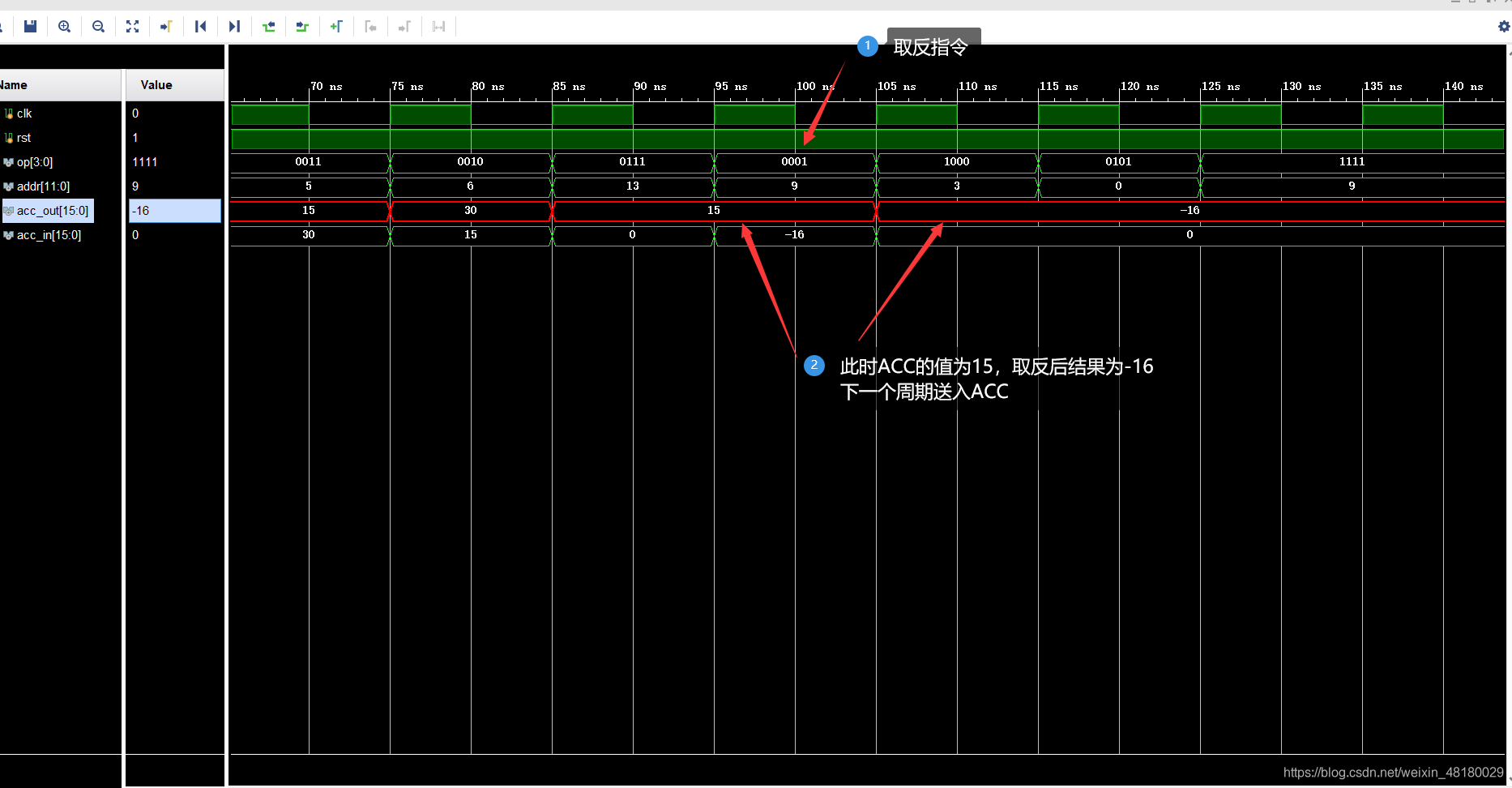

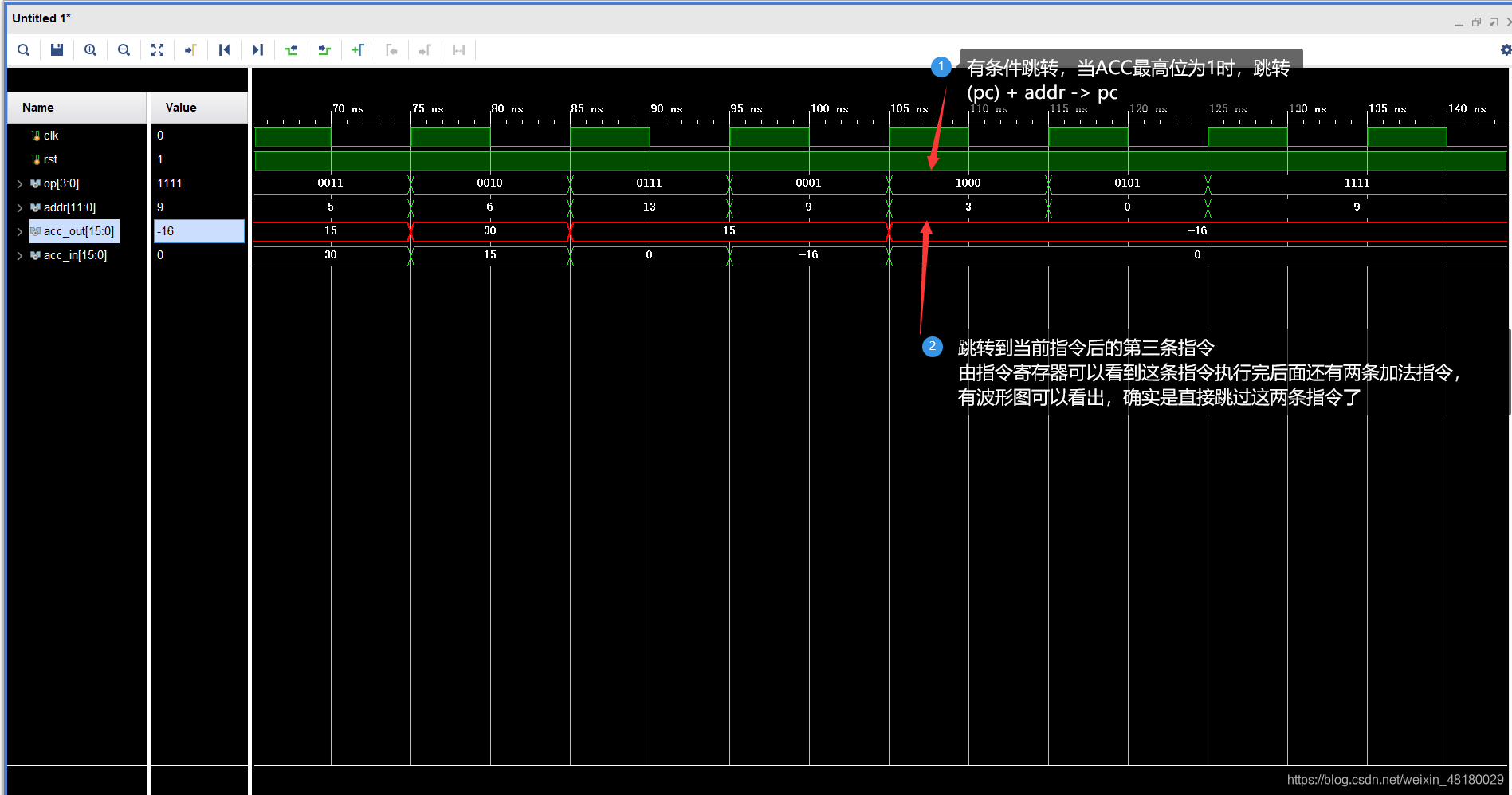

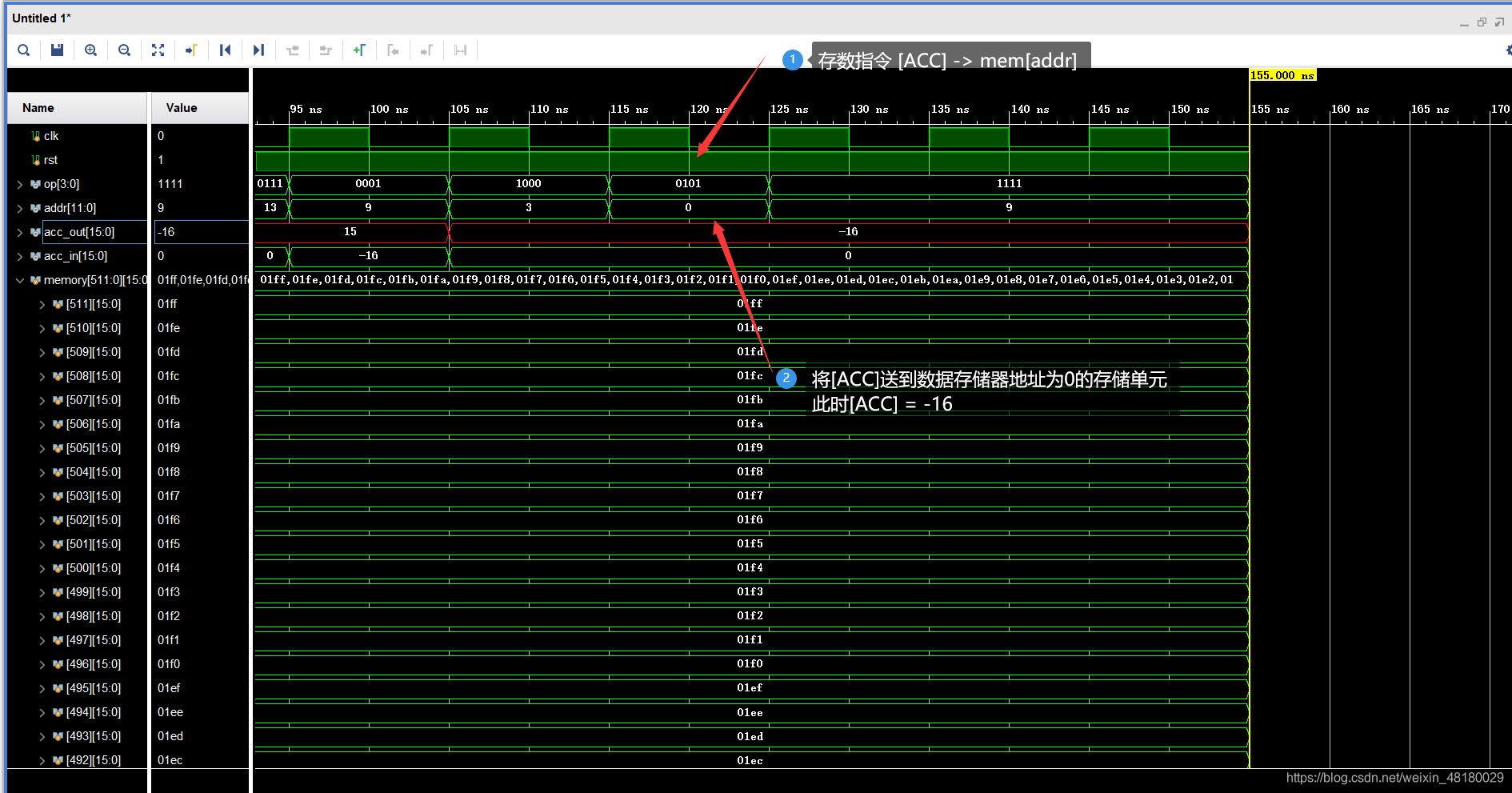

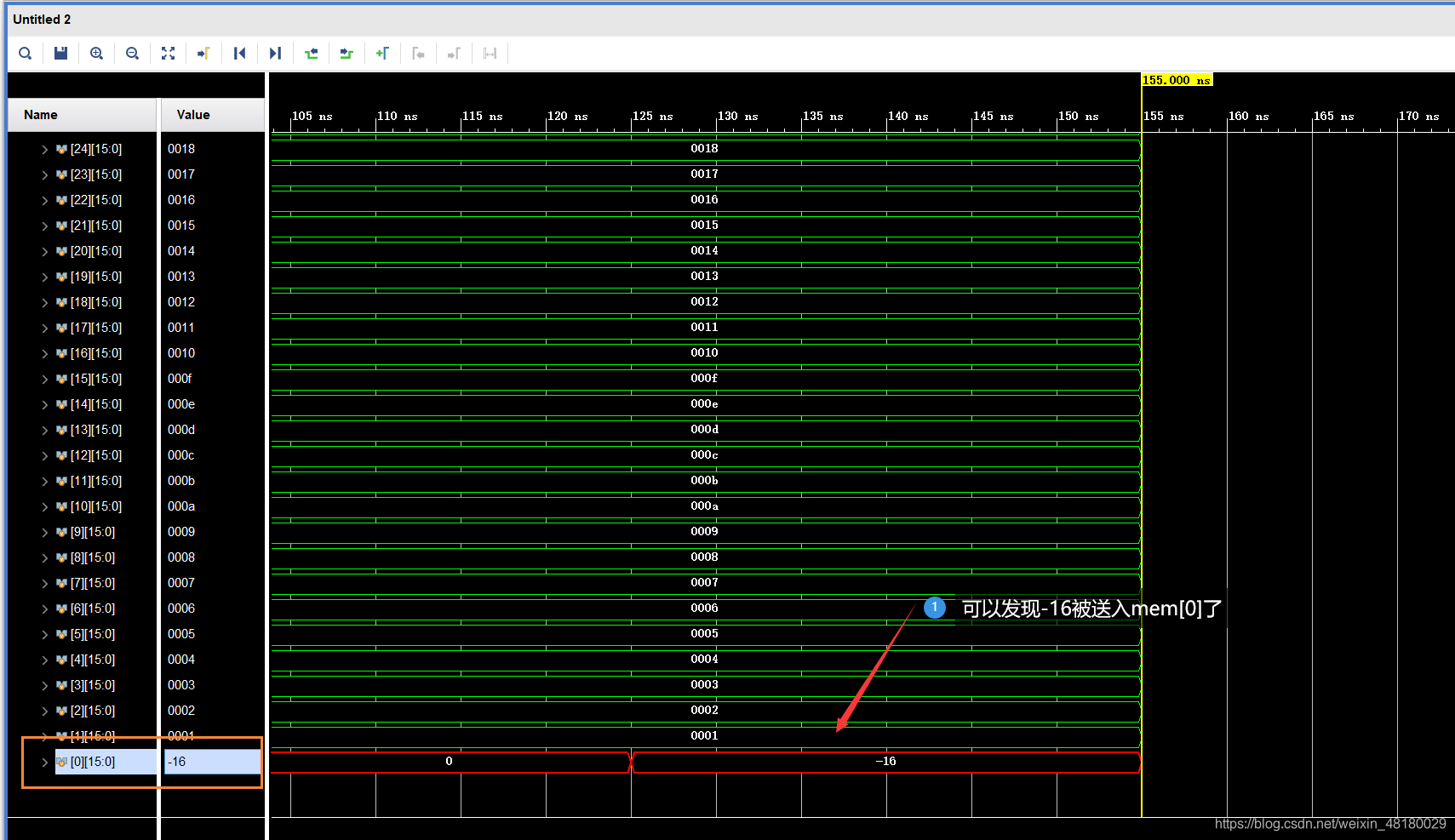

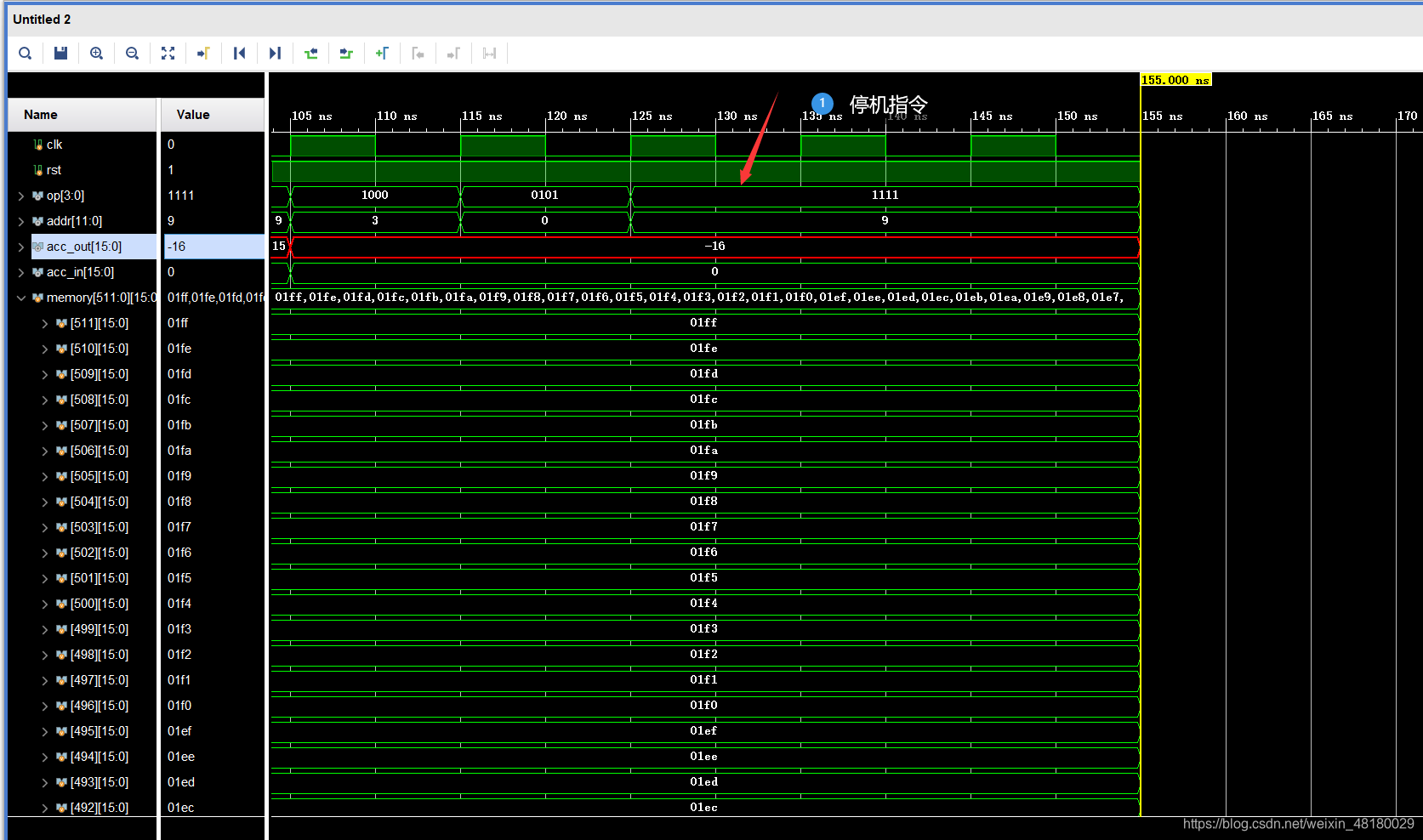

module InsMemory(input[11:0] Addr,output reg[15:0] Ins);reg[15:0]unit[5'd31:0];//32个16位存储单元initial beginunit[0] = 16'b0110_0000_0000_0001;//取数,将地址为1的数据放到ACC中unit[1] = 16'b0000_0000_0000_0000;//清除ACC,unit[2] = 16'b0100_0000_0000_0001;//加法,将地址为1的数据与ACC相加unit[3] = 16'b0100_0000_0000_0010;//加法,将地址为2的数据与ACC相加unit[4] = 16'b0100_0000_0000_0011;//加法,将地址为3的数据与ACC相加unit[5] = 16'b0100_0000_0000_0100;//加法,将地址为4的数据与ACC相加unit[6] = 16'b0100_0000_0000_0101;//加法,将地址为5的数据与ACC相加unit[7] = 16'b0011_0000_0000_0101;//ACC循环左移unit[8] = 16'b0010_0000_0000_0110;//ACC算术右移unit[9] = 16'b0111_0000_0000_1101;//无条件跳转,直接跳转到第13条指令unit[10] = 16'b0100_0000_0000_0110;//加法,将地址为6的数据与ACC相加unit[11] = 16'b0100_0000_0000_0111;//加法,将地址为7的数据与ACC相加unit[12] = 16'b0100_0000_0000_1000;//加法,将地址为8的数据与ACC相加unit[13] = 16'b0001_0000_0000_1001;//ACC取反unit[14] = 16'b1000_0000_0000_0011;//有条件跳转,相对当前指令,向下跳转3条,也就是第17条指令unit[15] = 16'b0100_0000_0000_1001;//加法,将地址为9的数据与ACC相加unit[16] = 16'b0100_0000_0000_1010;//加法,将地址为10的数据与ACC相加unit[17] = 16'b0101_0000_0000_0000;//存数,将ACC存放到数据存储器地址为0的存储单元中unit[18] = 16'b1111_0000_0000_1001;//停机指令endalways@(*)beginIns = unit[Addr];end endmodule

ACC模块

module ACC(input clk,input AccRW,//读写信号input[15:0] indata,output[15:0] outdata);reg[15:0] acc;initial beginacc = 0; endassign outdata = acc;always@(posedge clk)beginif(AccRW)acc = indata;end

endmodule

ALU模块

module ALU(input [3:0]alu_op,input[15:0]in1,in2,output reg flag,//当ACC的最高位为1时,输出1output reg[15:0] result);always@(*)begincase(alu_op) 4'b0000: result = 0;//清除4'b0001: result = ~in1;//取反4'b0010: result = in1[15] == 1 ? {1'b1,in1[15:1]} : {1'b0,in1[15:1]};//逻辑右移4'b0011: result = {in1[14:0],in1[15]};//循环左移4'b0100: result = in1 + in2;//加法default:result = 0;endcaseflag = in1[15];end

endmodule

DataMemory模块

module DataMemory(clk,DataRW,//读写信号,当为1时,写入;为0时,读出DAddr, //读或写的地址DataIn,//要写入的数据DataOut,//要读出的数据);input clk,DataRW;input[11:0] DAddr;input[15:0] DataIn;output [15:0] DataOut;reg [15:0] memory[9'd511:0];//512个16位存储单元integer i;initial beginfor(i=0;i<512;i=i+1)memory[i] = i;endalways@(posedge clk)beginif(DataRW)memory[DAddr] = DataIn;endassign DataOut = memory[DAddr];endmodule

二路选择器模块

module Multiplexer16(control, //选择信号,当为1时,输出in1,当为0时,输出in0in1,in0,out);input control;input[15:0] in1,in0;output[15:0] out;assign out = control ? in1:in0;

endmodule

ControlUnit模块

module ControlUnit(input [3:0]op,output reg stop,output reg jmp,output reg jcc,output reg Mem_Alu,//二路选择器信号,当为1时,输出Memoutput reg AccRW,//ACC读写信号,为1时写output reg DataMemRW,//数据存储器读写信号output reg[3:0]alu_op//alu控制信号);initial beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 0;DataMemRW = 0;alu_op = 0; endalways@(*)begincase(op)//CLA 清除4'b0000:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 1;DataMemRW = 0;alu_op = 0; end//COM 取反4'b0001:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 1;DataMemRW = 0;alu_op = 4'b0001; end//SHR 算术右移4'b0010:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 1;DataMemRW = 0;alu_op = 4'b0010; end//CSL 循环左移4'b0011:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 1;DataMemRW = 0;alu_op = 4'b0011; end//ADD 加法4'b0100:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 1;DataMemRW = 0;alu_op = 4'b0100; end//STA 存数4'b0101:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 0;DataMemRW = 1;alu_op = 4'b0000; end//LDA 取数4'b0110:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 1;AccRW = 1;DataMemRW = 0;alu_op = 4'b0000; end//JMP 无条件跳转4'b0111:beginstop = 0;jmp = 1;jcc = 0;Mem_Alu = 0;AccRW = 0;DataMemRW = 0;alu_op = 4'b0000; end//BAN 有条件跳转4'b1000:beginstop = 0;jmp = 0;jcc = 1;Mem_Alu = 0;AccRW = 0;DataMemRW = 0;alu_op = 4'b0000; end//STP 停机4'b1111:beginstop = 1;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 0;DataMemRW = 0;alu_op = 4'b0000; enddefault:beginstop = 0;jmp = 0;jcc = 0;Mem_Alu = 0;AccRW = 0;DataMemRW = 0;alu_op = 0; endendcaseend

endmodule

顶层模块

module SignleCPU(input clk,input rst,output[3:0]op,output[11:0]addr,//指令分割操作码后的剩余部分output[15:0]acc_in,output[15:0]acc_out);wire[11:0]currentAddress;wire stop,jmp,ban,jcc,Mem_Alu,AccRW,DataMemRW,flag;wire[3:0] alu_op;wire[15:0]Ins,DataMem_out,result;PC pc(clk,rst,stop,jmp,ban,addr,currentAddress);InsMemory insmemory(currentAddress,Ins);assign op = Ins[15:12];assign addr = Ins[11:0];ControlUnit cu(op,stop,jmp,jcc,Mem_Alu,AccRW,DataMemRW,alu_op);ACC acc(clk,AccRW,acc_in,acc_out);ALU alu(alu_op,acc_out,DataMem_out,flag,result);assign ban = jcc & flag;DataMemory datamemory(clk,DataMemRW,addr,acc_out,DataMem_out);Multiplexer16 mul16(Mem_Alu,DataMem_out,result,acc_in);endmodule

测试模块

module Test();reg clk,rst;wire[3:0]op;wire[11:0]addr;wire[15:0]acc_out,acc_in;SignleCPU f(clk,rst,op,addr,acc_in,acc_out);initial beginclk = 0;rst=1;#155 $stop;endalways #5 clk = ~clk;

endmodule

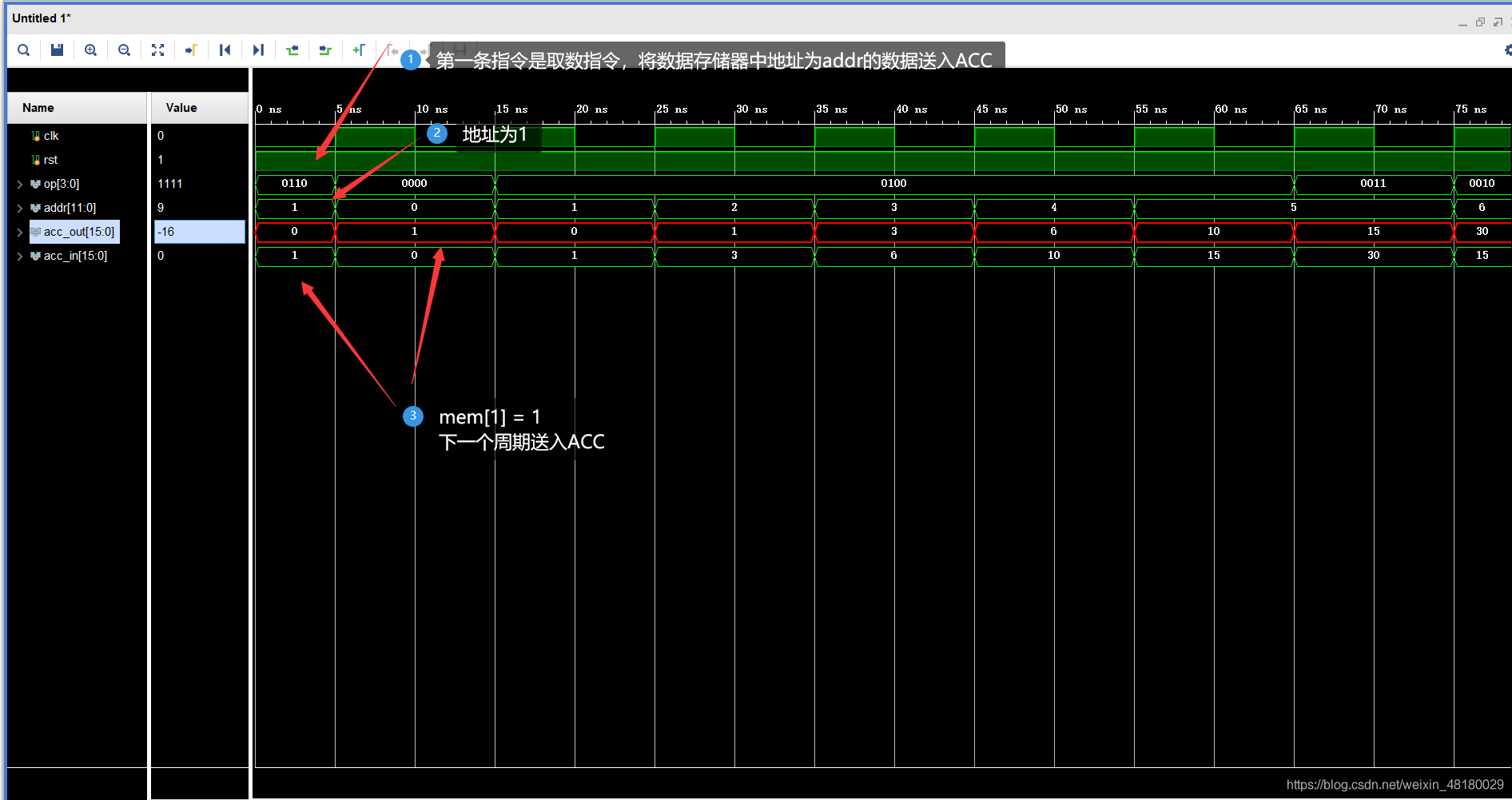

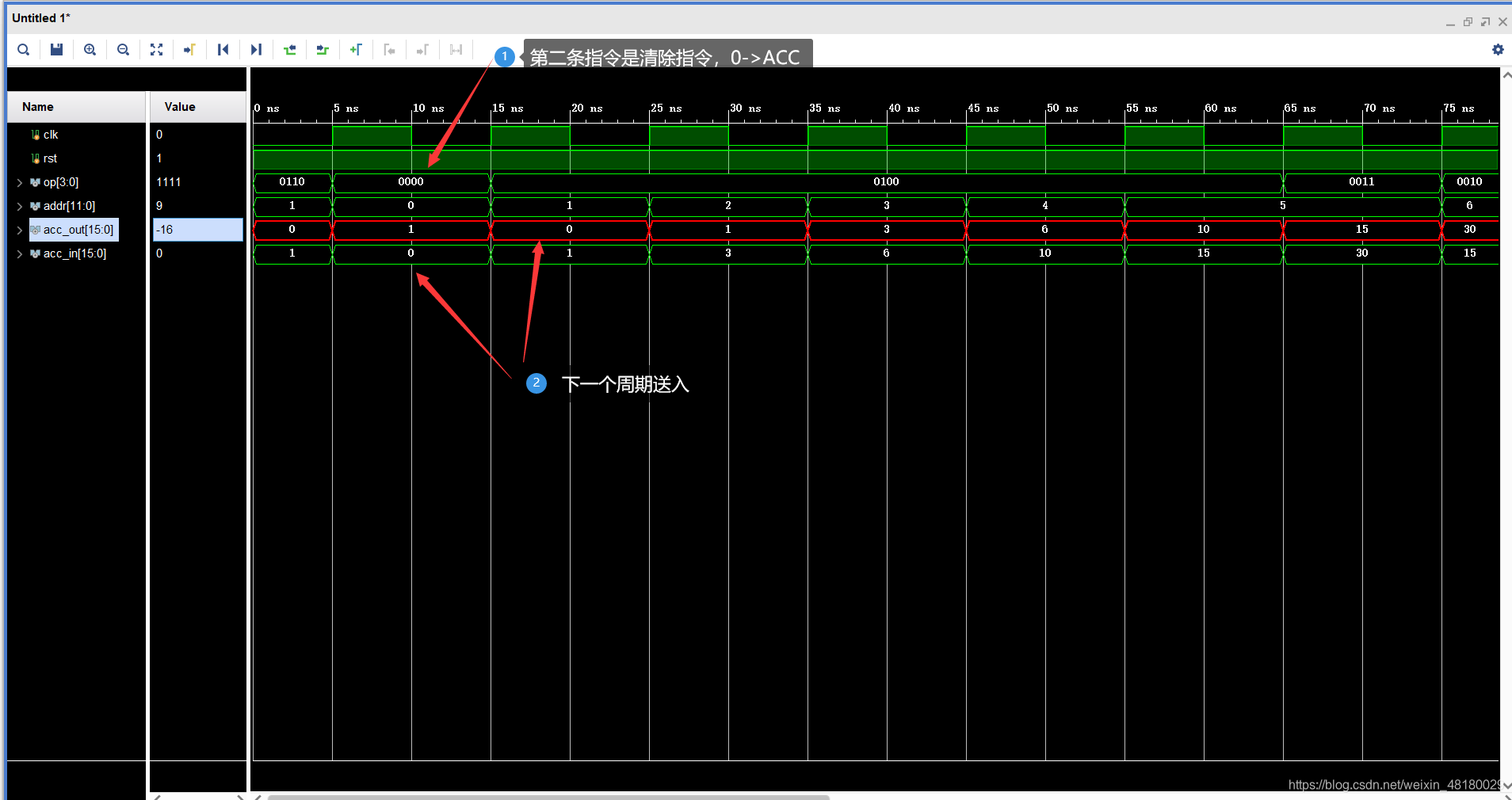

波形图要结合指令来看

这篇关于【计算机组成原理】单周期CPU设计与实现-十条指令CPU的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!