本文主要是介绍基于QC-LDPC编码的循环移位网络的FPGA实现,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

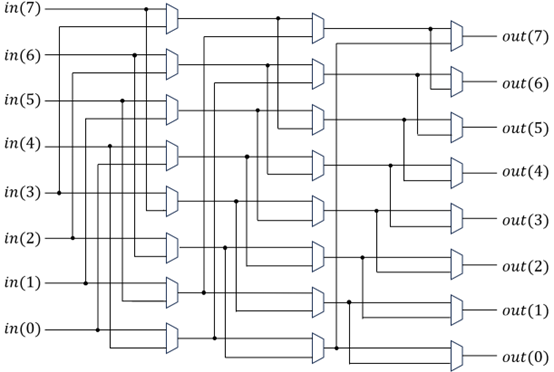

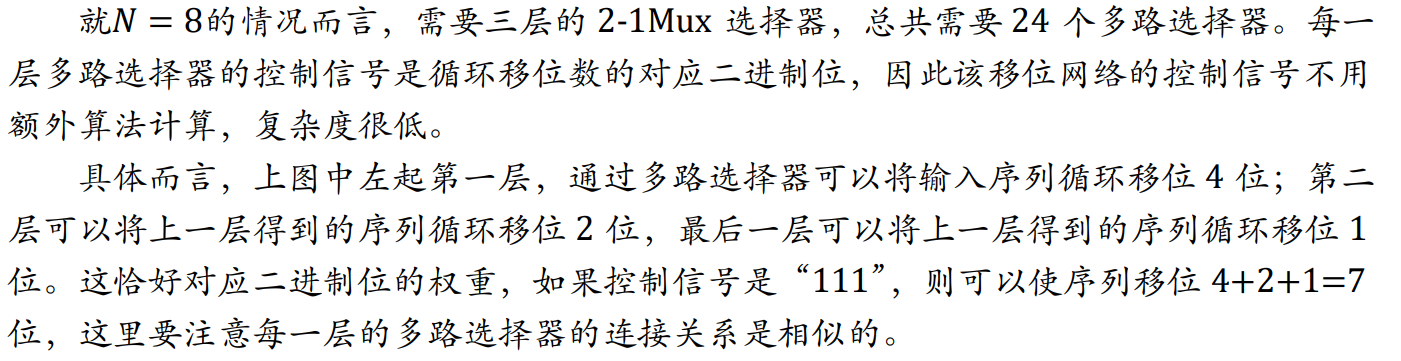

一、桶式移位寄存器(barrel shifter)

一、桶式移位寄存器(barrel shifter)

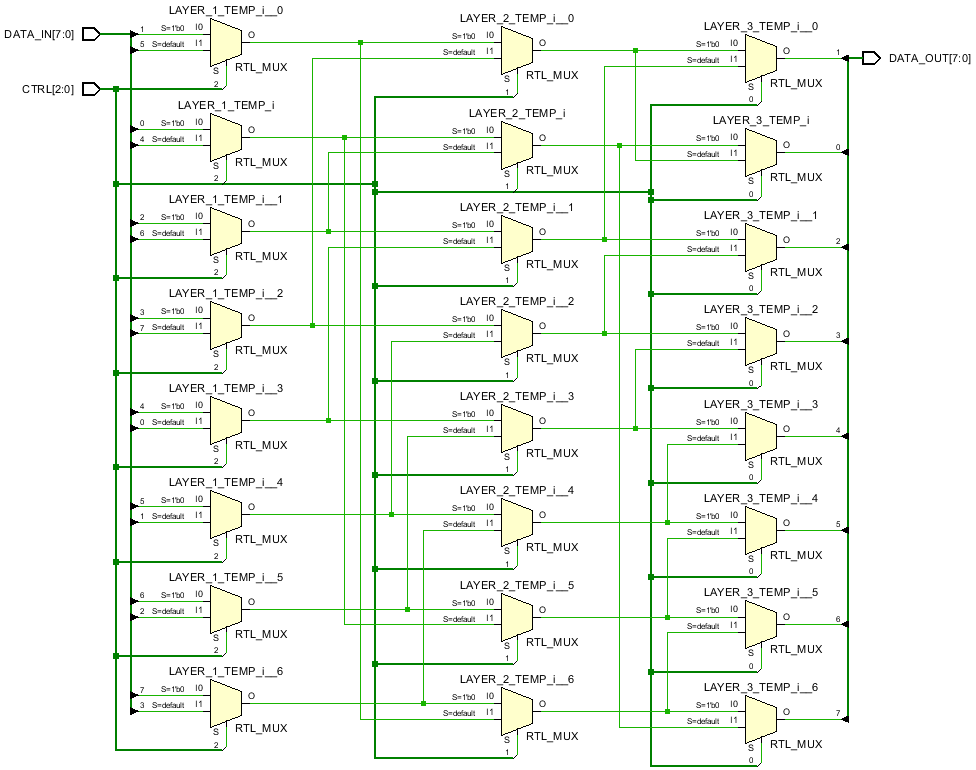

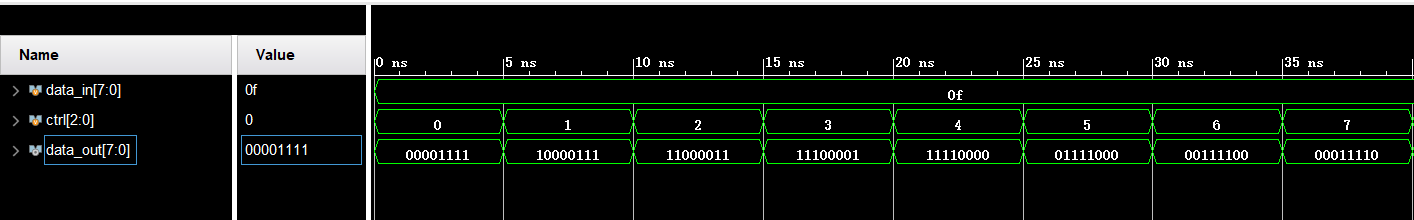

八位桶式移位寄存器的VHDL实现如下,由于每一层结构相似,于是采用生成语句for_generate实现,使用该代码实现的RTL级分析和理论的结构一致,仿真结果也符合预期。

entity barrel_shift isGENERIC(DATA_WIDTH: INTEGER:=8;CTRL_WIDTH: INTEGER:=3);Port (DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);CTRL: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0));

end barrel_shift;architecture Behavioral of barrel_shift is

SIGNAL LAYER_1_TEMP: STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);

SIGNAL LAYER_2_TEMP: STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);

SIGNAL LAYER_3_TEMP: STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);

beginLAYER_1:FOR I IN 0 TO 7 GENERATEG1:IF I<=3 GENERATELAYER_1_TEMP(I)<=DATA_IN(I)WHEN CTRL(2)='0'ELSE DATA_IN(I+4);END GENERATE G1;G2:IF I>3 GENERATE LAYER_1_TEMP(I)<=DATA_IN(I)WHEN CTRL(2)='0'ELSE DATA_IN(I-4);END GENERATE G2; END GENERATE LAYER_1;LAYER_2:FOR I IN 0 TO 7 GENERATEG3:IF I<=5 GENERATELAYER_2_TEMP(I)<=LAYER_1_TEMP(I)WHEN CTRL(1)='0'ELSE LAYER_1_TEMP(I+2);END GENERATE G3;G4:IF I>5 GENERATE LAYER_2_TEMP(I)<=LAYER_1_TEMP(I)WHEN CTRL(1)='0'ELSE LAYER_1_TEMP(I-6);END GENERATE G4; END GENERATE LAYER_2;LAYER_3:FOR I IN 0 TO 7 GENERATEG5:IF I<=6 GENERATELAYER_3_TEMP(I)<=LAYER_2_TEMP(I)WHEN CTRL(0)='0'ELSE LAYER_2_TEMP(I+1);END GENERATE G5;G6:IF I>6 GENERATE LAYER_3_TEMP(I)<=LAYER_2_TEMP(I)WHEN CTRL(0)='0'ELSE LAYER_2_TEMP(I-7);END GENERATE G6; END GENERATE LAYER_3; DATA_OUT<=LAYER_3_TEMP;end Behavioral;

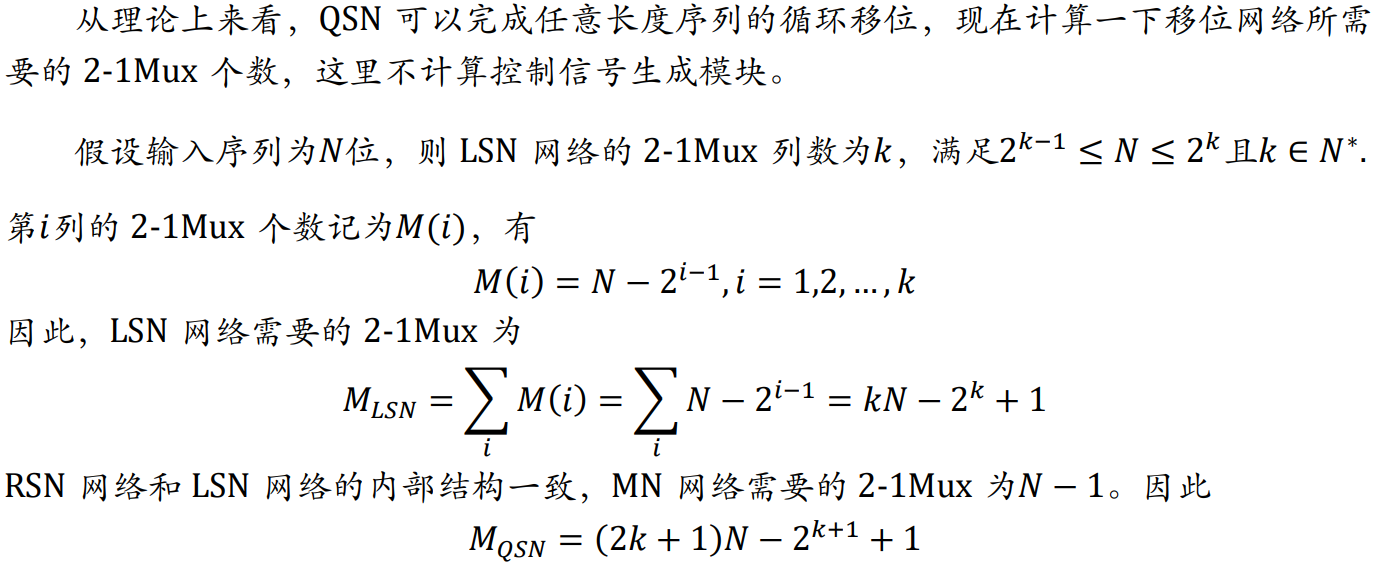

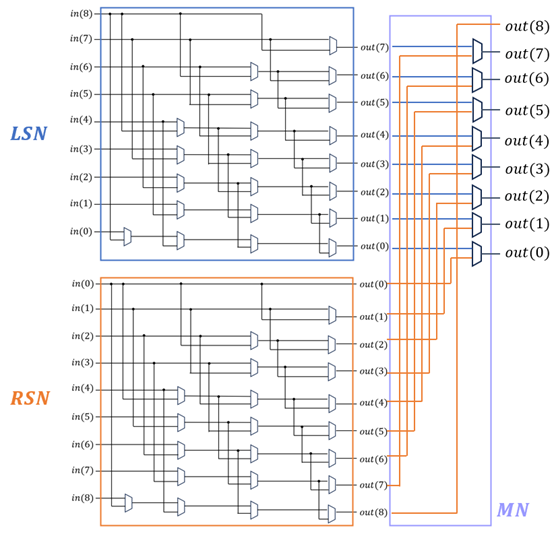

二、QSN网络

2.1LSN网络

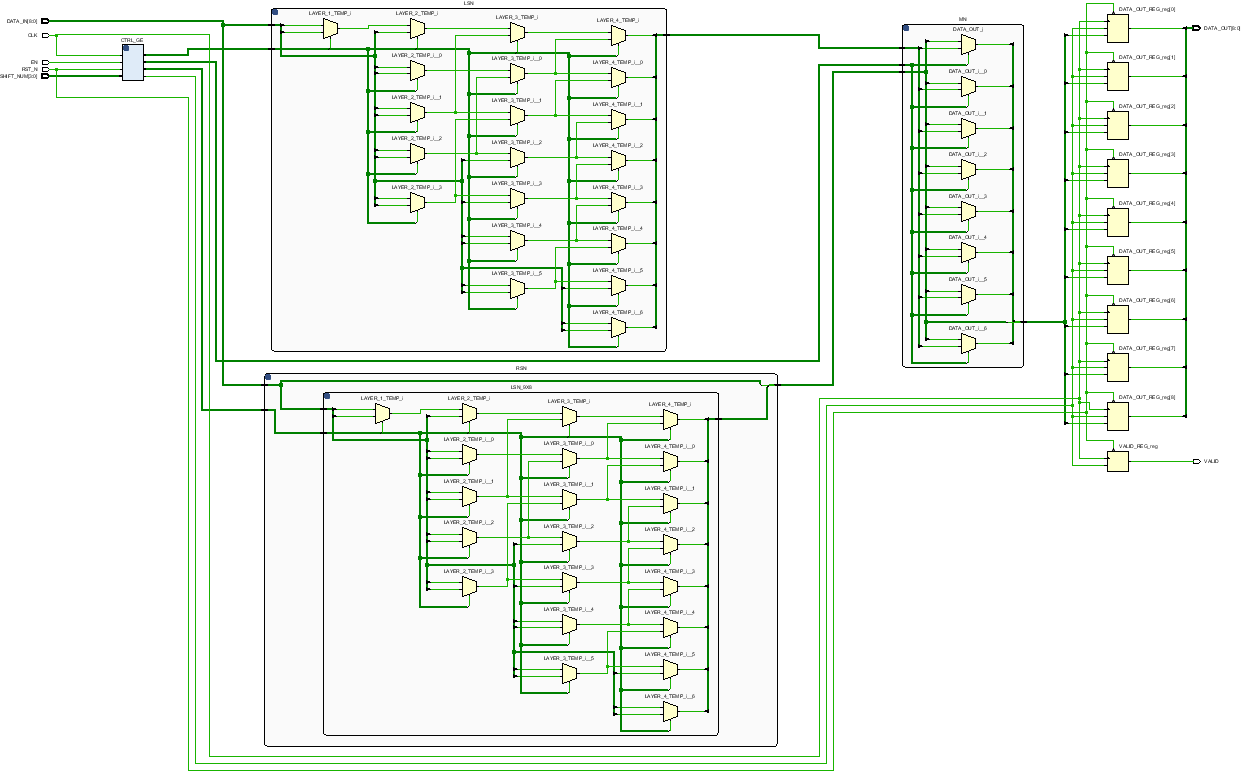

该网络的VHDL代码和RTL分析如下

entity LSN_9x8_network isGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);LSN_CTRL: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0));

end LSN_9x8_network;architecture Behavioral of LSN_9x8_network is

SIGNAL LAYER_1_TEMP: STD_LOGIC_VECTOR(DATA_WIDTH-9 DOWNTO 0);

SIGNAL LAYER_2_TEMP: STD_LOGIC_VECTOR(DATA_WIDTH-5 DOWNTO 0);

SIGNAL LAYER_3_TEMP: STD_LOGIC_VECTOR(DATA_WIDTH-3 DOWNTO 0);

SIGNAL LAYER_4_TEMP: STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);

beginLAYER_1:FOR I IN 0 TO 0 GENERATEG1:IF I=0 GENERATELAYER_1_TEMP(I)<=DATA_IN(I)WHEN LSN_CTRL(3)='0'ELSE DATA_IN(I+8);END GENERATE G1; END GENERATE LAYER_1;LAYER_2:FOR I IN 0 TO 4 GENERATE--5G2:IF I=0 GENERATELAYER_2_TEMP(I)<=LAYER_1_TEMP(I)WHEN LSN_CTRL(2)='0'ELSE DATA_IN(I+4);END GENERATE G2; G3:IF I>0 GENERATELAYER_2_TEMP(I)<=DATA_IN(I) WHEN LSN_CTRL(2)='0'ELSE DATA_IN(I+4);END GENERATE G3; END GENERATE LAYER_2;LAYER_3:FOR I IN 0 TO 6 GENERATE--7G4:IF I<=2 GENERATELAYER_3_TEMP(I)<=LAYER_2_TEMP(I)WHEN LSN_CTRL(1)='0'ELSE LAYER_2_TEMP(I+2);END GENERATE G4; G5:IF I>2 AND I<=4 GENERATELAYER_3_TEMP(I)<=LAYER_2_TEMP(I)WHEN LSN_CTRL(1)='0'ELSE DATA_IN(I+2);END GENERATE G5;G6:IF I>4 GENERATELAYER_3_TEMP(I)<=DATA_IN(I) WHEN LSN_CTRL(0)='0'ELSE DATA_IN(I+2);END GENERATE G6; END GENERATE LAYER_3; LAYER_4:FOR I IN 0 TO 7 GENERATE---8G7:IF I<=5 GENERATELAYER_4_TEMP(I)<=LAYER_3_TEMP(I)WHEN LSN_CTRL(0)='0'ELSE LAYER_3_TEMP(I+1);END GENERATE G7; G8:IF I=6 GENERATELAYER_4_TEMP(I)<=LAYER_3_TEMP(I)WHEN LSN_CTRL(0)='0'ELSE DATA_IN(I+1);END GENERATE G8;G9:IF I>6 GENERATELAYER_4_TEMP(I)<=DATA_IN(I) WHEN LSN_CTRL(0)='0'ELSE DATA_IN(I+1);END GENERATE G9; END GENERATE LAYER_4; DATA_OUT<=LAYER_4_TEMP(DATA_WIDTH-2 DOWNTO 0);end Behavioral;

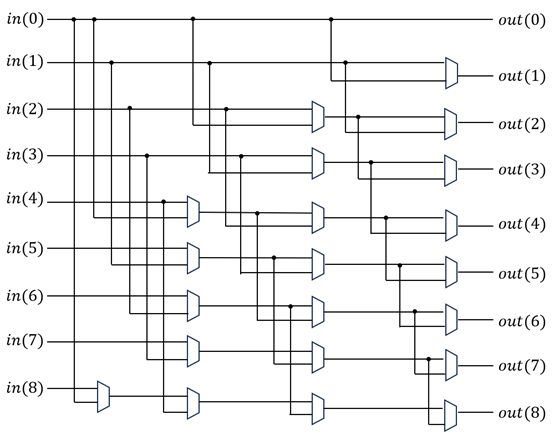

2.2RSN网络

9x9的右移网络的VHDL实现和RTL分析如下

entity RSN_9x9_network isGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);RSN_CTRL: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0));

end RSN_9x9_network;architecture Behavioral of RSN_9x9_network isCOMPONENT LSN_9x8_network ISGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);LSN_CTRL: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0));END COMPONENT;

beginLSN_9X8:LSN_9x8_networkGENERIC MAP(DATA_WIDTH => DATA_WIDTH,CTRL_WIDTH => CTRL_WIDTH)PORT MAP( DATA_IN(0) => DATA_IN(8),DATA_IN(1) => DATA_IN(7),DATA_IN(2) => DATA_IN(6),DATA_IN(3) => DATA_IN(5),DATA_IN(4) => DATA_IN(4),DATA_IN(5) => DATA_IN(3),DATA_IN(6) => DATA_IN(2),DATA_IN(7) => DATA_IN(1), DATA_IN(8) => DATA_IN(0), LSN_CTRL => RSN_CTRL,DATA_OUT(0) => DATA_OUT(8),DATA_OUT(1) => DATA_OUT(7),DATA_OUT(2) => DATA_OUT(6),DATA_OUT(3) => DATA_OUT(5),DATA_OUT(4) => DATA_OUT(4),DATA_OUT(5) => DATA_OUT(3),DATA_OUT(6) => DATA_OUT(2),DATA_OUT(7) => DATA_OUT(1)); DATA_OUT(0) <= DATA_IN(0);

end Behavioral;

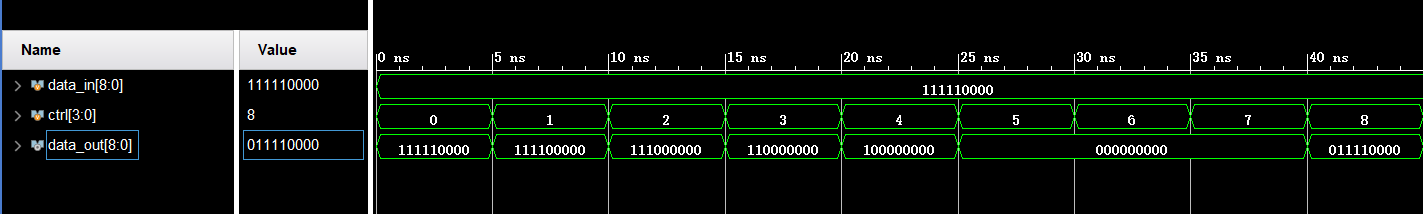

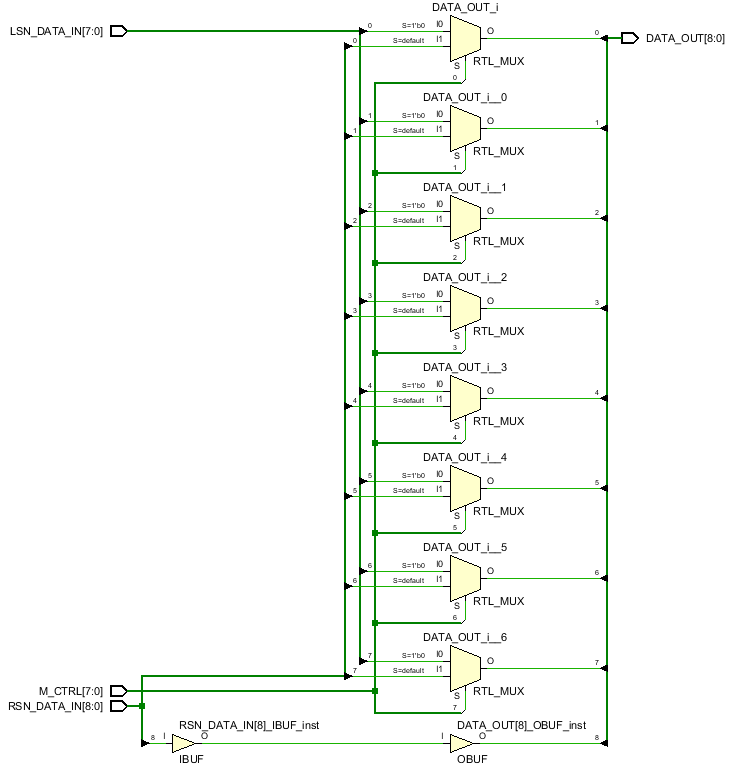

2.3MN网络

entity MN_9x9_network isGENERIC(DATA_WIDTH: INTEGER:=9);Port (LSN_DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);RSN_DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);M_CTRL: IN STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0));

end MN_9x9_network;architecture Behavioral of MN_9x9_network is

beginG1:FOR I IN 0 TO DATA_WIDTH-2 GENERATEDATA_OUT(I)<=RSN_DATA_IN(I) WHEN M_CTRL(I)='0' ELSE LSN_DATA_IN(I);END GENERATE G1;DATA_OUT(8)<='0' WHEN FALSE ELSE RSN_DATA_IN(8);

end Behavioral;

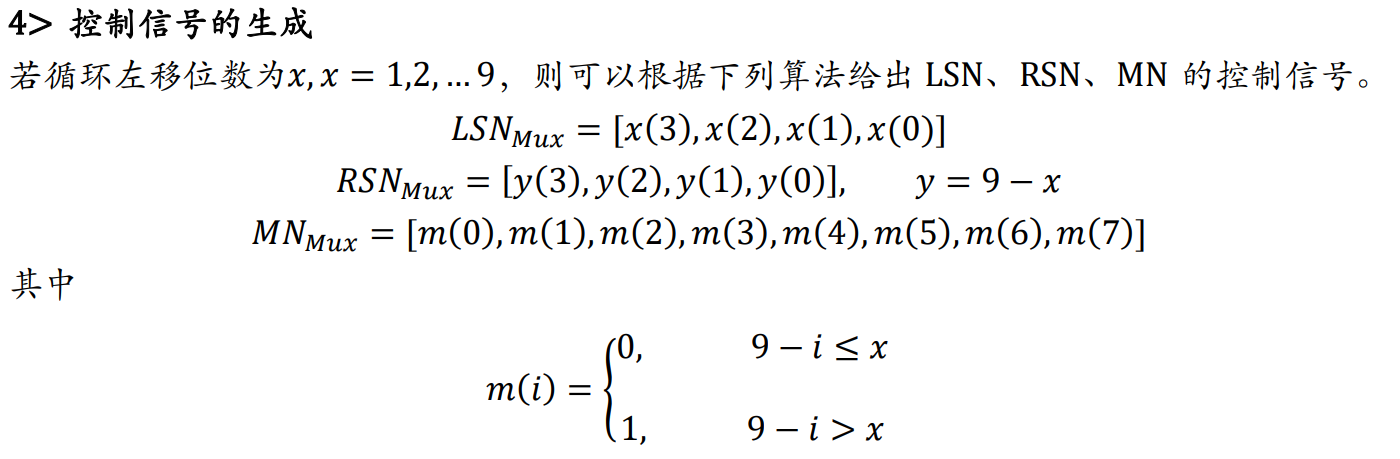

2.4控制模块

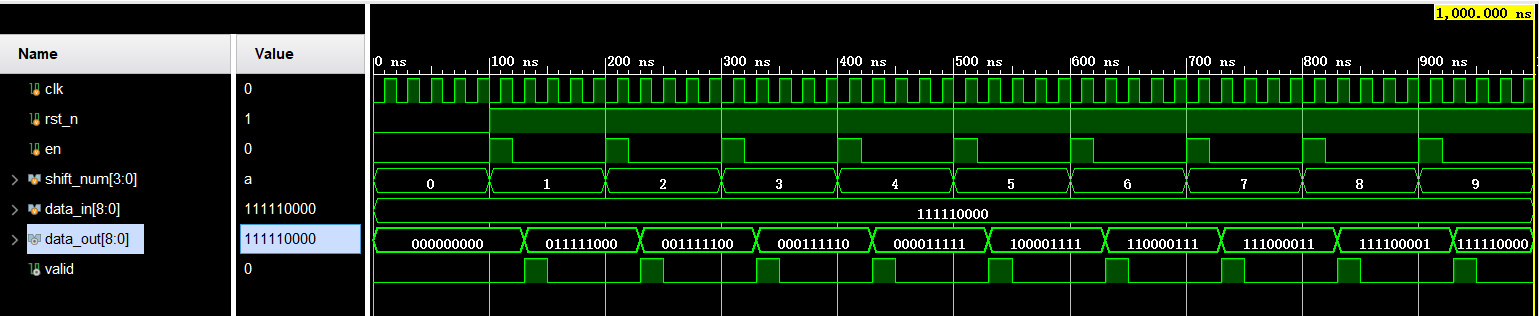

控制模块的VHDL实现和仿真波形图如下

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;entity CTRL isGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (CLK: IN STD_LOGIC;RST_N: IN STD_LOGIC;EN: IN STD_LOGIC;SHIFT_NUM: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);M: OUT STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);LSN_SHIFT: OUT STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);RSN_SHIFT: OUT STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0); VALID: OUT STD_LOGIC );

end CTRL;architecture Behavioral of CTRL isbeginLSN_SHIFT_GE:PROCESS(CLK,RST_N)BEGINIF RST_N='0'THENLSN_SHIFT<=(OTHERS=>'0');ELSIF RISING_EDGE(CLK) THENIF EN='1'THENLSN_SHIFT<=SHIFT_NUM;END IF;END IF;END PROCESS;RSN_SHIFT_GE:PROCESS(CLK,RST_N)BEGINIF RST_N='0'THENRSN_SHIFT<=(OTHERS=>'0');ELSIF RISING_EDGE(CLK) THENIF EN='1'THENRSN_SHIFT<=9-SHIFT_NUM;END IF;END IF;END PROCESS;M_GE:PROCESS(CLK,RST_N)BEGINIF RST_N='0'THENM<=(OTHERS=>'0');ELSIF RISING_EDGE(CLK) THENIF EN='1'THENIF SHIFT_NUM>=9 THEN M(0)<='0';ELSE M(0)<='1';END IF;IF SHIFT_NUM>=8 THEN M(1)<='0';ELSE M(1)<='1';END IF;IF SHIFT_NUM>=7 THEN M(2)<='0';ELSE M(2)<='1';END IF;IF SHIFT_NUM>=6 THEN M(3)<='0';ELSE M(3)<='1';END IF;IF SHIFT_NUM>=5 THEN M(4)<='0';ELSE M(4)<='1';END IF;IF SHIFT_NUM>=4 THEN M(5)<='0';ELSE M(5)<='1';END IF;IF SHIFT_NUM>=3 THEN M(6)<='0';ELSE M(6)<='1';END IF;IF SHIFT_NUM>=2 THEN M(7)<='0';ELSE M(7)<='1';END IF;END IF;END IF;END PROCESS;VALID_GE:PROCESS(CLK,RST_N)BEGINIF RST_N='0'THEN VALID<='0'; ELSIF RISING_EDGE(CLK) THEN IF EN='1'THENVALID<='1'; ELSEVALID<='0'; END IF;END IF;END PROCESS;

end Behavioral; 2.5顶层

2.5顶层

顶层的作用是将子模块例化,VHDL实现和RTL分析如下

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;entity QSN_9x9_network isGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (CLK: IN STD_LOGIC;RST_N: IN STD_LOGIC;EN: IN STD_LOGIC;SHIFT_NUM: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);VALID: OUT STD_LOGIC);

end QSN_9x9_network;architecture Behavioral of QSN_9x9_network isCOMPONENT LSN_9x8_network ISGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);LSN_CTRL: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0));END COMPONENT;COMPONENT RSN_9x9_network ISGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);RSN_CTRL: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0));END COMPONENT;COMPONENT MN_9x9_network ISGENERIC(DATA_WIDTH: INTEGER:=9);Port (LSN_DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);RSN_DATA_IN: IN STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);M_CTRL: IN STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);DATA_OUT: OUT STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0));END COMPONENT;COMPONENT CTRL ISGENERIC(DATA_WIDTH: INTEGER:=9;CTRL_WIDTH: INTEGER:=4);Port (CLK: IN STD_LOGIC;RST_N: IN STD_LOGIC;EN: IN STD_LOGIC;SHIFT_NUM: IN STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);M: OUT STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);LSN_SHIFT: OUT STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);RSN_SHIFT: OUT STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0); VALID: OUT STD_LOGIC );END COMPONENT;

--CTRL

SIGNAL M_CTRL: STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);

SIGNAL LSN_SHIFT: STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);

SIGNAL RSN_SHIFT: STD_LOGIC_VECTOR(CTRL_WIDTH-1 DOWNTO 0);

SIGNAL CTRL_EN: STD_LOGIC;

--LSN

SIGNAL LSN_OUT: STD_LOGIC_VECTOR(DATA_WIDTH-2 DOWNTO 0);

--RSN

SIGNAL RSN_OUT: STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);

--MN_OUT

SIGNAL OUT_REG: STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);

SIGNAL DATA_OUT_REG:STD_LOGIC_VECTOR(DATA_WIDTH-1 DOWNTO 0);

--VALID_REG

SIGNAL VALID_REG: STD_LOGIC;

beginCTRL_GE:CTRLGENERIC MAP(DATA_WIDTH => DATA_WIDTH,CTRL_WIDTH => CTRL_WIDTH)PORT MAP(CLK => CLK,RST_N => RST_N,EN => EN,SHIFT_NUM => SHIFT_NUM,M => M_CTRL,LSN_SHIFT => LSN_SHIFT,RSN_SHIFT => RSN_SHIFT,VALID => CTRL_EN);LSN:LSN_9x8_networkGENERIC MAP(DATA_WIDTH => DATA_WIDTH,CTRL_WIDTH => CTRL_WIDTH)PORT MAP(DATA_IN => DATA_IN, LSN_CTRL => LSN_SHIFT,DATA_OUT => LSN_OUT);RSN:RSN_9x9_networkGENERIC MAP(DATA_WIDTH => DATA_WIDTH,CTRL_WIDTH => CTRL_WIDTH)PORT MAP(DATA_IN => DATA_IN, RSN_CTRL => RSN_SHIFT,DATA_OUT => RSN_OUT);MN:MN_9x9_networkGENERIC MAP(DATA_WIDTH => DATA_WIDTH)PORT MAP( LSN_DATA_IN=> LSN_OUT,RSN_DATA_IN=> RSN_OUT,M_CTRL => M_CTRL,DATA_OUT => OUT_REG);OUT_GE:PROCESS(CLK,RST_N)BEGINIF RST_N='0'THENDATA_OUT_REG<=(OTHERS=>'0');ELSIF RISING_EDGE(CLK)THENIF CTRL_EN='1'THENDATA_OUT_REG<=OUT_REG;END IF;END IF;END PROCESS;DATA_OUT<=DATA_OUT_REG;VALID_REG_GE:PROCESS(CLK,RST_N)BEGINIF RST_N='0'THENVALID_REG<='0';ELSIF RISING_EDGE(CLK)THENIF CTRL_EN='1'THENVALID_REG<='1';ELSEVALID_REG<='0';END IF;END IF;END PROCESS;VALID<=VALID_REG;end Behavioral;

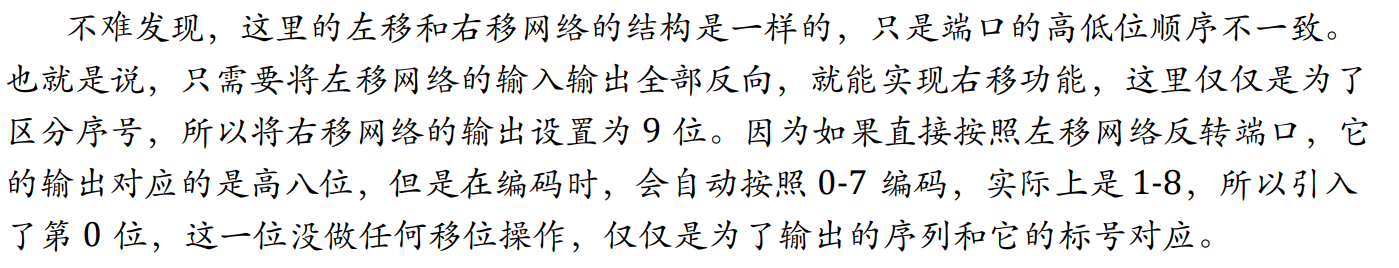

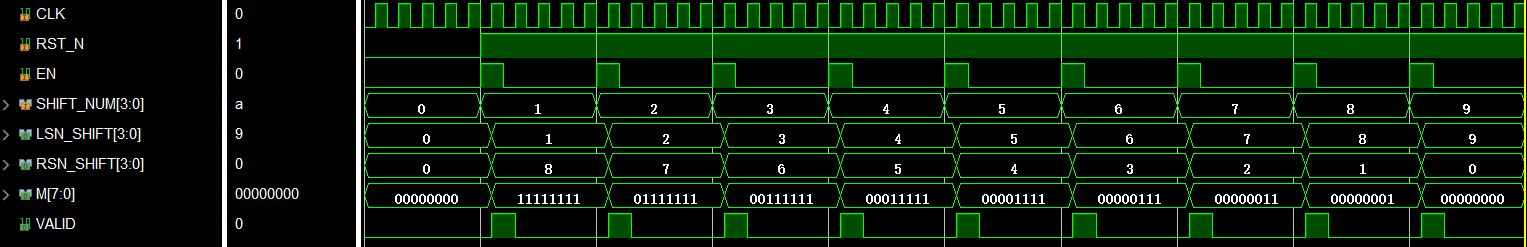

使用时钟CLK和复位信号RST_N控制时序,并加入输入输出使能信号。最后实现的结果如下,可以看到左循环移位1~9的结果均正确。

这篇关于基于QC-LDPC编码的循环移位网络的FPGA实现的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!