本文主要是介绍OV7725 摄像头驱动,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

STM32 的处理速度比传统的8、16 位机快得多,所以使用它驱动摄像头采集图像信息并进行基本的加工处理非常适合,本章讲解使用STM32 驱动OV7725 型号的摄像头。

一、摄像头简介

在各类信息中,图像含有最丰富的信息,作为机器视觉领域的核心部件,摄像头被广泛地应用在安防、探险以及车牌检测等场合。摄像头按输出信号的类型来看可以分为数字摄像头和模拟摄像头,按照摄像头图像传感器材料构成来看可以分为CCD 和CMOS。现在智能手机的摄像头绝大部分都是CMOS 类型的数字摄像头。

1.1 OV7725 摄像头

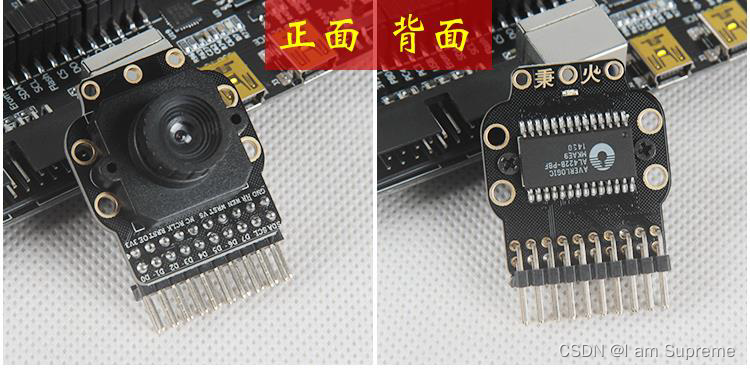

本节主要讲解实验板配套的摄像头,是一款分辨率为30w的CMOS摄像头它的实物见图,该摄像头主要由镜头、图像传感器、板载电路、FIFO 缓存及下方的信号引脚组成。

镜头部件包含一个镜头座和一个可旋转调节距离的凸透镜,通过旋转可以调节焦距,正常使用时,镜头座覆盖在电路板上遮光,光线只能经过镜头传输到正中央的图像传感器,它采集光线信号,采集得的数据被缓存到摄像头背面的FIFO缓存中,然后外部器件通过下方的信号引脚获取拍摄得到的图像数据。

若拆开摄像头座,在摄像头的正下方可看到PCB 板上的一个方形器件,它是摄像头的核心部件,型号为OV7725 的CMOS 类型数字图像传感器。该传感器支持输出最大为30 万像素的图像 (640x480 分辨率),它的体积小,工作电压低,支持使用VGA 时序输出图像数据,输出图像的数据格式支持YUV(422/420)、YCbCr422 以及RGB565 格式。它还可以对采集得的图像进行补偿,支持伽玛曲线、白平衡、饱和度、色度等基础处理。

1.2 OV7725 引脚及功能框架图

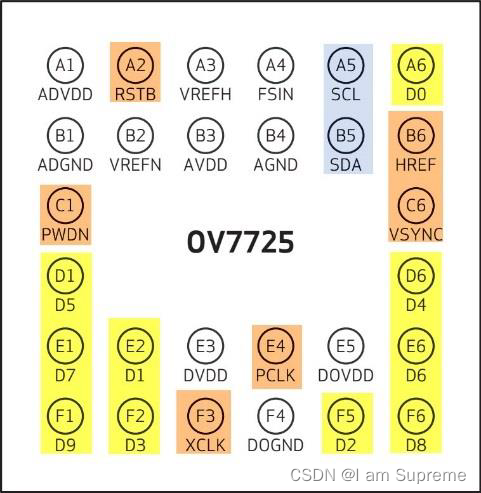

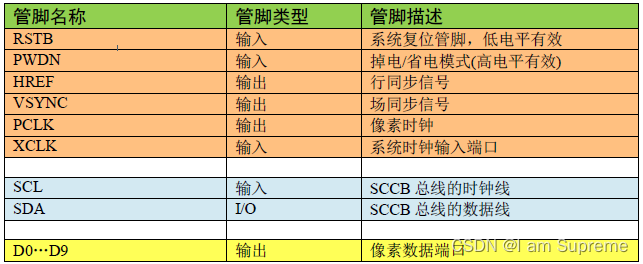

OV7725 传感器采用BGA 封装,它的前端是采光窗口,引脚都在背面引出,引脚的分布见图

图中的非彩色部分是电源相关的引脚,彩色部分是主要的信号引脚,其介绍如表

二、功能框图

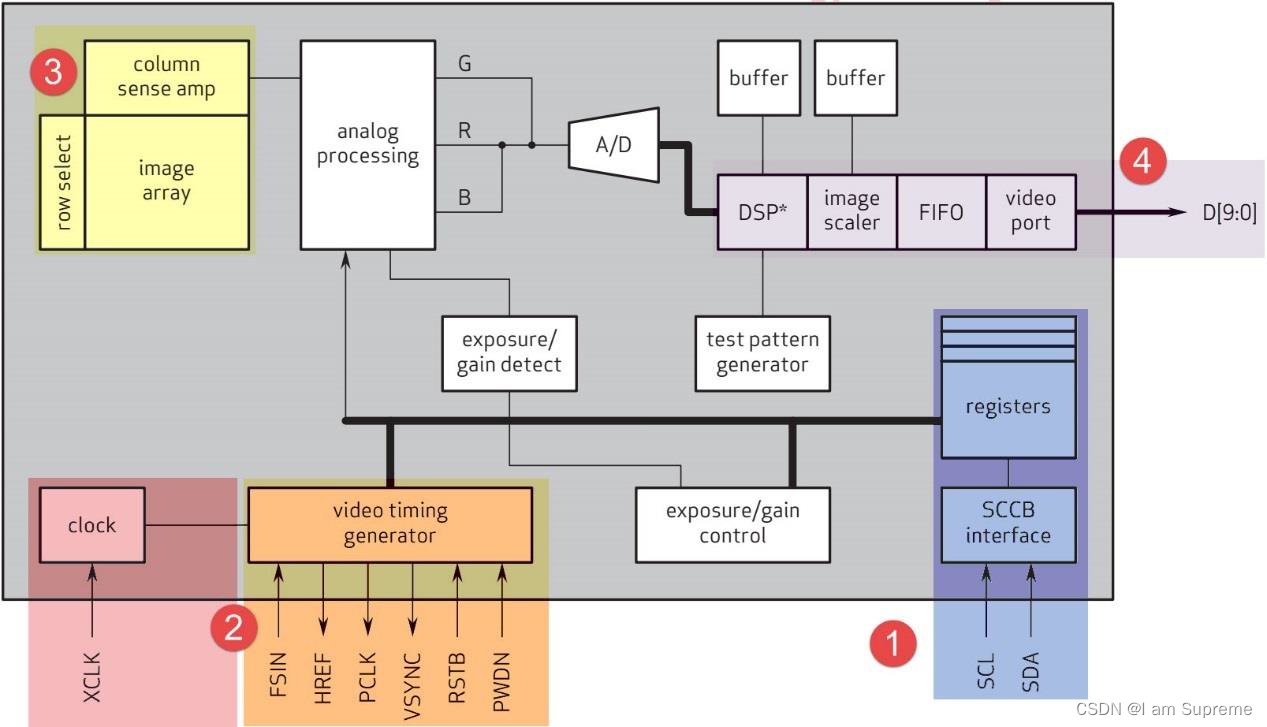

(1)控制寄存器

标号①处的是OV7725 的控制寄存器,它根据这些寄存器配置的参数来运行,而这些参数是由外部控制器通过SCL 和SDA 引脚写入的,SCL 与SDA 使用的通讯协议SCCB 跟I2C 十分类似,在STM32 中我们完全可以直接用I2C 硬件外设来控制。

(2)通信、控制信号及时钟

标号②处包含了OV7725的通信、控制信号及外部时钟,其中PCLK、HREF及VSYNC分别是像素同步时钟、行同步信号以及帧同步信号,这与液晶屏控制中的VGA 信号是很类似的。RSTB 引脚为低电平时,用于复位整个传感器芯片,PWDN 用于控制芯片进入低功耗模式。注意最后的一个XCLK 引脚,它跟PCLK是完全不同的,XCLK 是用于驱动整个传感器芯片的时钟信号,是外部输入到OV7725 的信号;而PCLK 是OV7725 输出数据时的同步信号,它是由OV7725 输出的信号。XCLK 可以外接晶振或由外部控制器提供,若要类比XCLK 之于OV7725 就相当于HSE 时钟输入引脚与STM32 芯片的关系,PCLK 引脚可类比STM32 的I2C 外设的SCL 引脚。

(3) 感光矩阵

标号③处的是感光矩阵,光信号在这里转化成电信号,经过各种处理,这些信号存储成由一个个像素点表示的数字图像。

(4) 数据输出信号

标号④处包含了DSP 处理单元,它会根据控制寄存器的配置做一些基本的图像处理运算。这部分还包含了图像格式转换单元及压缩单元,转换出的数据最终通过D0-D9 引脚输出,一般来说我们使用8 根据数据线来传输,这时仅使用D2-D9 引脚。

2.1SCCB 时序

外部控制器对OV7725 寄存器的配置参数是通过SCCB 总线传输过去的,而SCCB 总线跟I2C十分类似,所以在STM32驱动中可以直接使用片上I2C外设与它通讯,SCCB可以完全当成I2C使用。关于SCCB协议的完整内容可查看配套资料里的《SCCB 协议》文档,下面进行简单介绍。

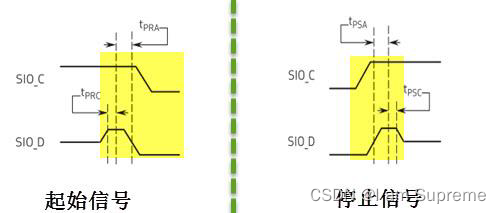

2.1.1 SCCB的起始、停止信号及数据有效性

SCCB的起始信号、停止信号及数据有效性与I2C完全一样,见下图

- 起始信号:SCL(图中为SIO_C)为高电平,SDA(图中为SIO_D)出现一个下降沿,则SCCB开始传输。

- 停止信号:在SCL为高电平时,SDA出现一个上升沿,则SCCB停止传输。

- 数据有效性:除了开始和停止状态,在数据传输过程中,当SCL为高电平时,必须保证SDA上的数据稳定,也就是说,SDA上的电平变换只能发生在SCL为低电平的时候,SDA的信号在SCL为高电平时被采集。

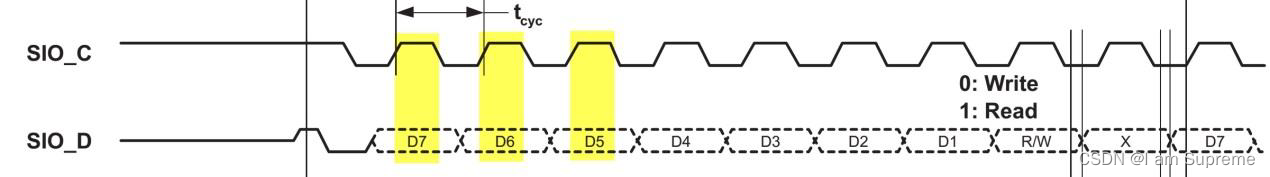

2.1.2 SCCB数据读写过程

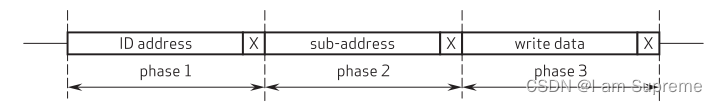

在SCCB协议中定义的读写操作与I2C也是一样的,只是换了一种说法。它定义了两种写操作,即三步写操作和两步写操作。三步写操作可向设备的一个目的寄存器写入数据,见下图。

在三步写操作中,第一阶段发送从设备的ID地址+W标志(等于I2C的设备地址:7位设备地址+读写方向标志),第二阶段发送从设备目标寄存器的8位地址,第三阶段发送要写入寄存器的8位数据。图中“X”数据可写入1或者0,对通讯无影响。

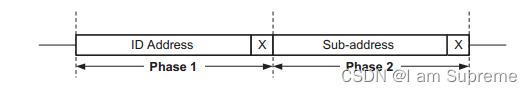

而两步写操作没有第三阶段,即只向从器件传输了设备ID+W标志和目的寄存器的地址,见下图,两步写操作是用来配合后面读寄存器数据操作的,它与读操作一起使用,实现I2C的复合过程。

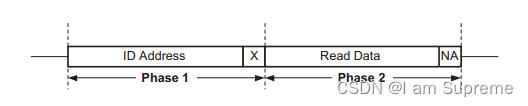

两步读操作,它用于读取从设备目的寄存器中的数据,见图 51-8。在第一阶段中发送从设备的设备ID+R标志(设备地址+读方向标志)和自由位,在第二阶段中读取寄存器中的8位数据和写NA 位(非应答信号)。由于两步读操作没有确定目的寄存器的地址,所以在读操作前,必需有一个两步写操作,以提供读操作中的寄存器地址。

可以看到,以上介绍的SCCB 特性都与I2C 无区别,完全可以使用STM32 的I2C 外设来与OV7725 进行SCCB 通讯。

2.1.3 OV7725寄存器

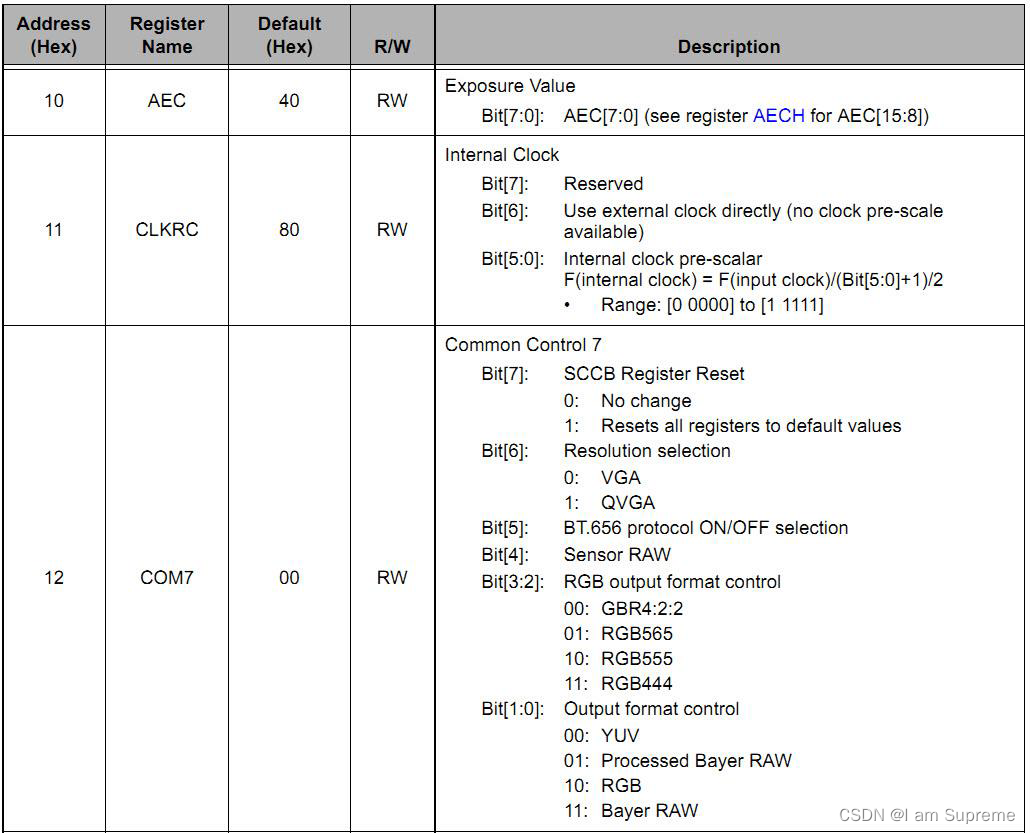

控制OV7725 涉及到它很多的寄存器,可直接查询《OV7725datasheet》了解,通过这些寄存器的配置,可以控制它输出图像的分辨率大小、图像格式、图像处理及图像方向等。见下图

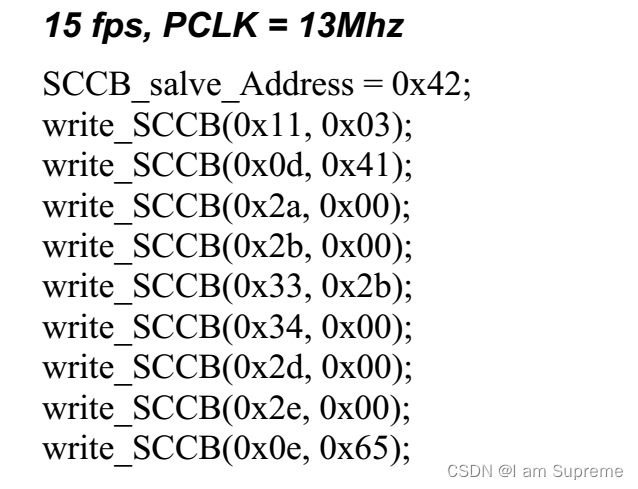

官方还提供了一个《OV7725 Software Application Note》的文档,它针对不同的配置需求,提供了配置范例,见下图。其中write_SCCB 是一个利用SCCB 向寄存器写入数据的函数,第一个参数为要写入的寄存器的地址,第二个参数为要写入的内容。

调节帧率的寄存器配置范例

2.1.4 像素数据输出时序

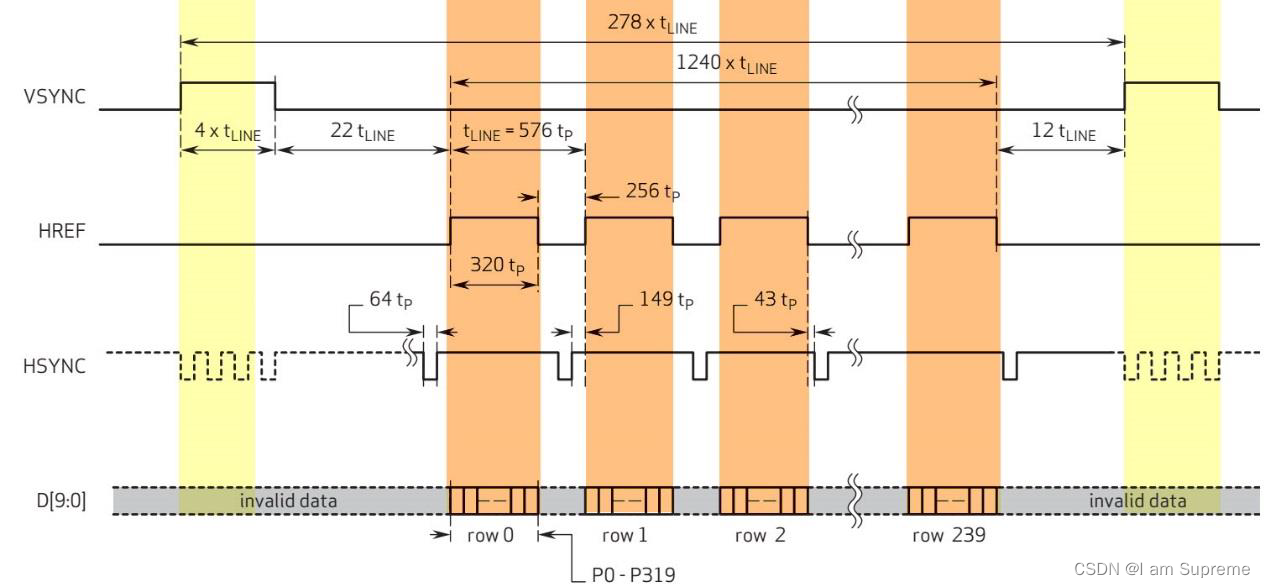

主控制器OV7725采样SCCB协议读写其寄存器,而它输出图像时则使用VGA或QVGA时序,其中VGA在输出图像分辨率为480*640时采样,QVGA 是Quarter VGA,其输出分辨率为240*320,这些时序跟控制液晶屏输出图像数据时十分类似。

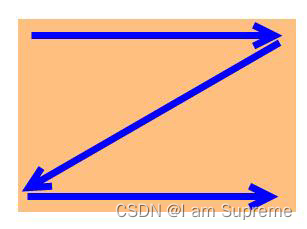

OV7725传感器输出图像时,一帧帧地输出,在帧内的数据一般从左到右,从上到下,一个像素一个像素地输出(也可以通过寄存器修改方向)

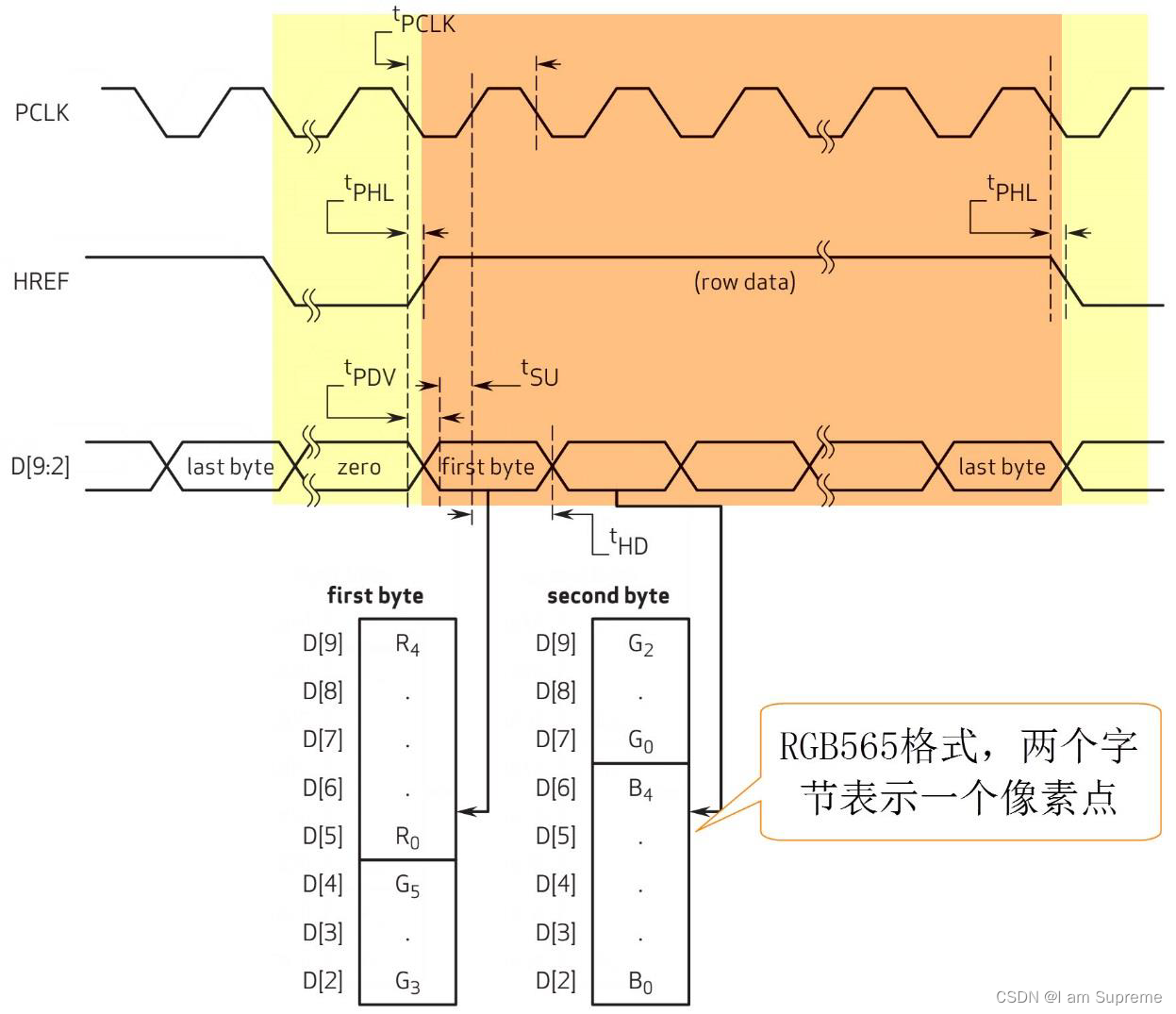

例如见下图,若我们使用D2-D9数据线,图像格式设置为RGB565,进行数据输出时,D2-D9数据线在PCLK在上升沿维持稳定,并且会在1个像素同步时钟PCLK的驱动下发送1字节的数据信号,所以2个PCLK时钟可发送1个RGB565格式的像素数据。当HERF为高电平时,像素数据依次传输,每传输完一行数据时,行同步信号HERF会输出一个电平跳变信号间隔开当前行和下一行的数据;一帧的图像由N行数据组成,当VSYNC为低电平时,各行的像素数据依次传输,每传输完一帧图像时,VSYNC会输出一个电平跳变信号。

2.1.5 FIFO读写时序

STM32F4 系列的控制器主频高、一般会扩展外部SRAM、SDRAM 等存储器,且具有DCMI 外设,可以直接根据VGA 时序接收并存储摄像头输出的图像数据;而STM32F1 系列的控制器一般主频较低、为节省成本可能不扩展SRAM 存储器,而且不具DCMI 外设,难以直接接收和存储OV7725 图像传感器输出的数据。

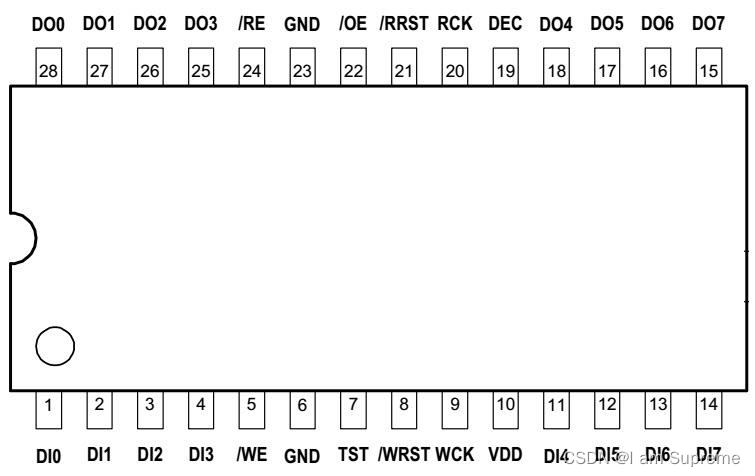

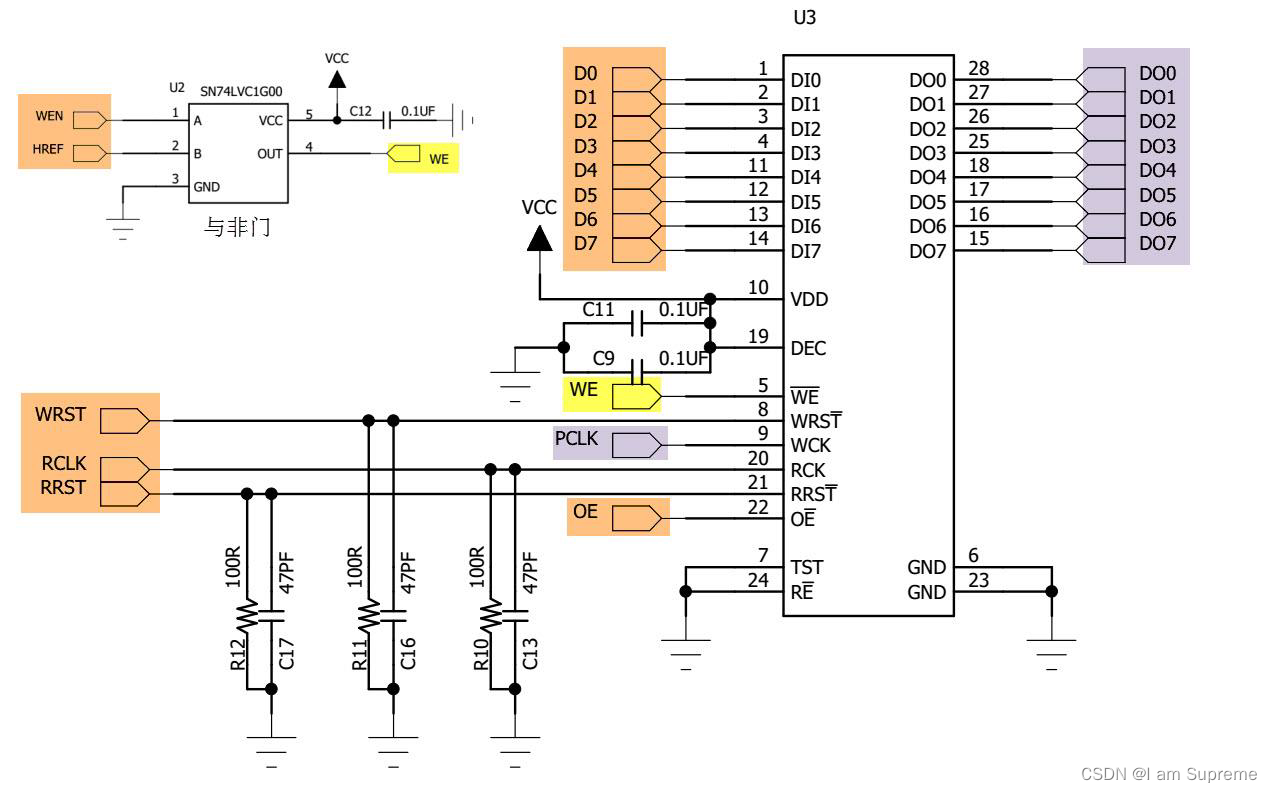

为了解决上述问题,针对类似STM32F1 或更低级的控制器秉火的OV7725 摄像头在图像传感器之外还添加了一个型号为AL422B 的FIFO,用于缓冲数据。AL422B 的本质是一种RAM存储器,见图 ,它的容量大小为393216 字节,支持同时写入和读出数据,这正是专门用于FIFO缓冲功能而设计的,关于它的详细说明可查阅《AL422_datasheet》文档。

AL422B 的各引脚功能介绍见表

由于AL422B支持同时写入和读出数据,所以它的输入和输出的控制信号线都是互相独立的。写入和读出数据的时序类似,跟VGA的像素输出时序一致,读写时序介绍如下:

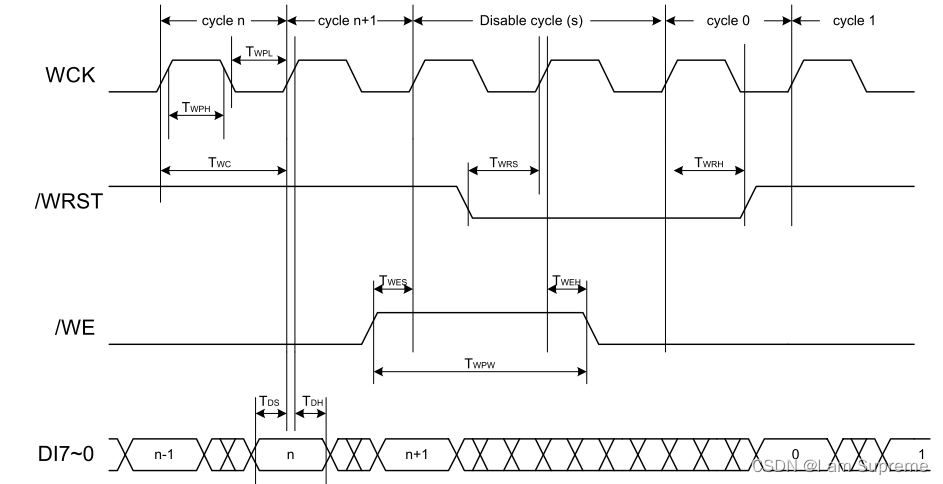

写时序:写FIFO(AL422B,下面统称为FIFO)时序见图

在写时序中,当WE管教为低电平的时候,FIFO写入处于使能状态,随着读时钟WCK的运转,DI[0:7]标识的数据将会按地址递增的方式存入FIFO;当WE管脚为高电平时,关闭输入,DI[0:7]的数据不会被写入FIFO。

在控制写入数据时,一般会先控制写指针作一个复位操作,把WRST设置为低电平,写指针会复位到FIFO的0地址,然后FIFO接收到的数据会从该地址开始按照自增的方式写入。

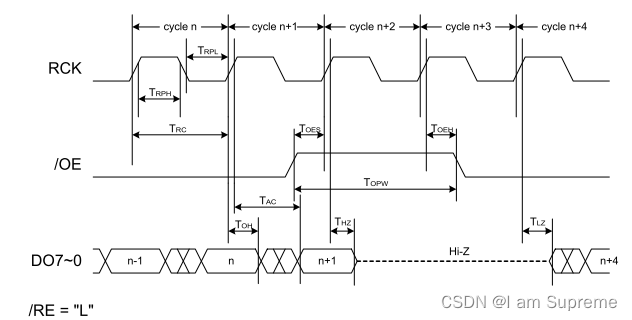

读时序,读FIFO时序见图

FIFO的读时序类似,不过读使能由两个引脚共同控制,即OE和RE引脚均为低电平时,输出处于使能状态,随着读时钟RCK的运转,在数据输出管教DO[0:7]就会按地址递增的方式输出数据。

类似地,在控制读出数据时,一般会先控制读指针作为一个复位操作,把RRST设置为低电平,读指针会复位到FIFO的0地址,然后FIFO数据从该地址开始按自增的方式输出。

三、摄像头的驱动原理

OV7725 摄像头中包含有FIFO,所以外部控制器驱动摄像头时,需要协调FIFO与OV7725传感器的院系,下面配合摄像头的原理讲解其驱动原理

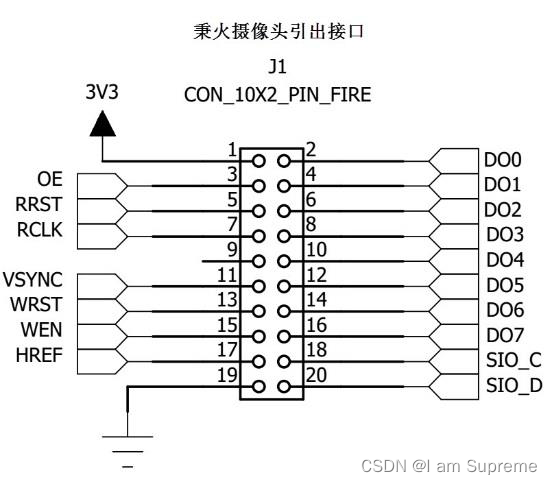

原理图主要分为外部引出接口、OV7725及FIFO部分

摄像头引出的接口包含了OV7725 传感器及FIFO 的混合引脚,外部的控制器使用这些引脚即可驱动摄像头,其说明见表

与OV7725传感器像素输出相关的PCLK和D[0:7]并没有引出,因为这些引脚被连接到了FIFO的输入部分,OV7725的像素输出时序与FIFO的写入数据时序是一致的,所以在OV7725时钟PCLK的驱动下,它输出的数据会一个字节一个字节地被FIFO接收并存储起来。

其中最为特殊的是WEN引脚,它与OV7725的HREF连接到一个与非门的输入,与非门的输出连接到FIFO的WE引脚,因此,当WEN与HREF均为高电平时,FIFO的WE为低电平,此时允许OV7725向FIFO写入数据。

外部控制器通过控制WEN引脚,可防止OV7725覆盖了还未被控制器读出得旧FIFO数据。另外,在OV7725输出时序中,只有当HERF为高电平时,PCLK驱动下D[0:7]线表示的才是有效像素数据,因此,利用HERF控制FIFO的WE可以确保只有有效数据才被写入到FIFO中

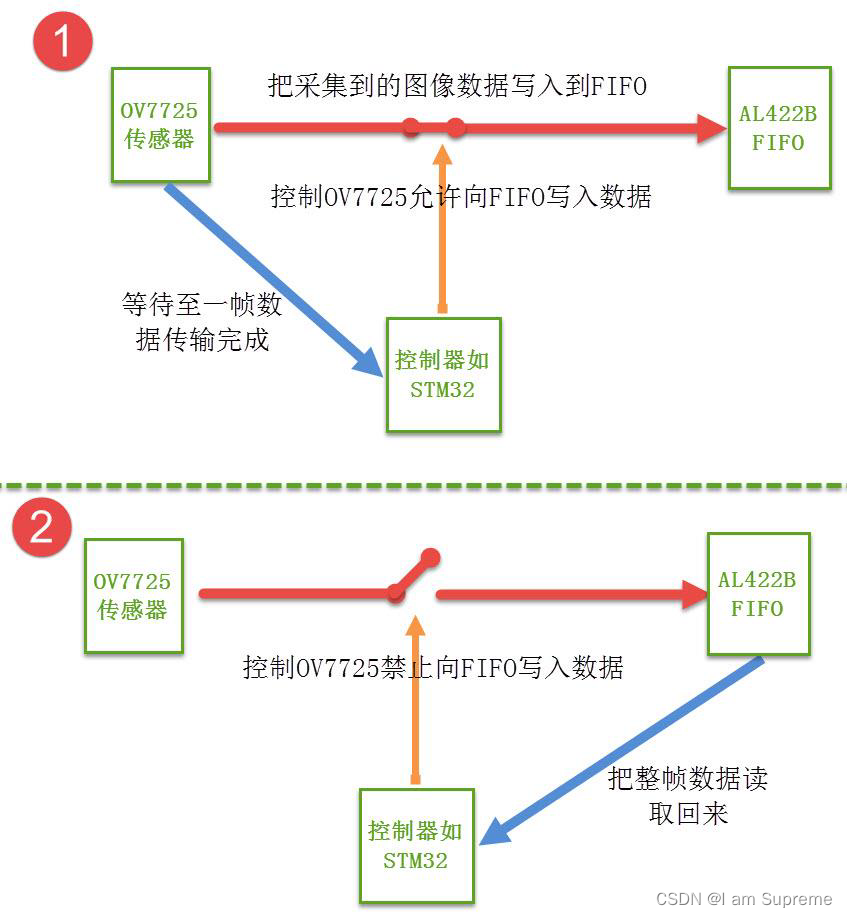

配合摄像头的原理图、OV7725、FIFO时序图,可总结出摄像头采集数据的过程如下:

- 利用SIO_C、SIO_D引脚通过SCCB协议向OV7725的寄存器写入初始化配置

- 初始化完成后,OV7725传感器会使用VGA时序输出图像数据,它的VSYNC会首先输出帧有效信号(低电平跳变),当外部的控制器(如STM32)检测到该信号时,把WEN引脚设置为高电平,并且WRST引脚复位,FIFO的写指针到0地址

- 随着OV7725继续按VGA时序输出图像数据,它在传输每行有效数据时,HERF引脚都会持续输出高电平,由于WEN和HREF同时为高电平输入至与非门,使得其连接到FIFO WE引脚的输出为低电平,允许向FIFO写入数据,所以在这期间,OV7725 通过它的PCLK 和D[0:7]信号线把图像数据存储到FIFO 中,由于前面复位了写指针,所以图像数据是从FIFO 的0 地址开始记录的;

- 各行图像数据持续传输至FIFO,受HERF控制的WE引脚确保写入到FIFO中的都是有效的图像数据,OV7725输出完一帧数据时,VSYNC会再次输出帧有效信号,表示一帧图像已输出完成。

- 控制器检测到上述VSYNC信号后,可知FIFO中已存储好一帧图像数据,这时控制WEN引脚为低电平,使得FIFO禁止写入,防止OV7725持续输出的下一帧数据覆盖当前FIFO数据。

- 控制器使用RRST复位读指针到FIFO的0地址,然后通过FIFO的RCLK和DO[0:7]引脚,从0 地址开始把FIFO 缓存的整帧图像数据读取出来。在这期间,OV7725是持续输出它采集到的图像数据的,但由于禁止写入FIFO,这些数据被丢弃了;

- 控制器使用WRST 复位写指针到FIFO 的0 地址,然后等待新的VSYNC 有效信号到来,检测到后把WEN 引脚设置为高电平,恢复OV7725 向FIFO 的写入权限,OV7725 输出的新一帧图像数据会被写入到FIFO 的0 地址中,重复上述过程。

摄像头的整个控制过程见图

使用本摄像头时,我们一般配套开发板的液晶屏,把OV7725 配置为240*320 分辨率(QVGA),RGB565 格式,那么OV7725 输出一帧的图像大小为240*320*2=153600 字节,而本摄像头采用的FIFO 型号AL422B 容量为393216 字节,最多可以缓存2 帧这样的图像,通过这样的方式,STM32 无需直接处理OV7725 高速输出的数据。但是,如果配置OV7725 为480*640 分辨率时,其一帧图像大小为480*640*2=614400 字节,FIFO 的容量不足以直接存储一帧这样的图像,因此,当OV7725 往FIFO写数据的时候,STM32端要同时读取数据,确保在OV7725 覆盖旧数据的之前,STM32 端已经把这部分数据读取出来了。

四、摄像头驱动实验

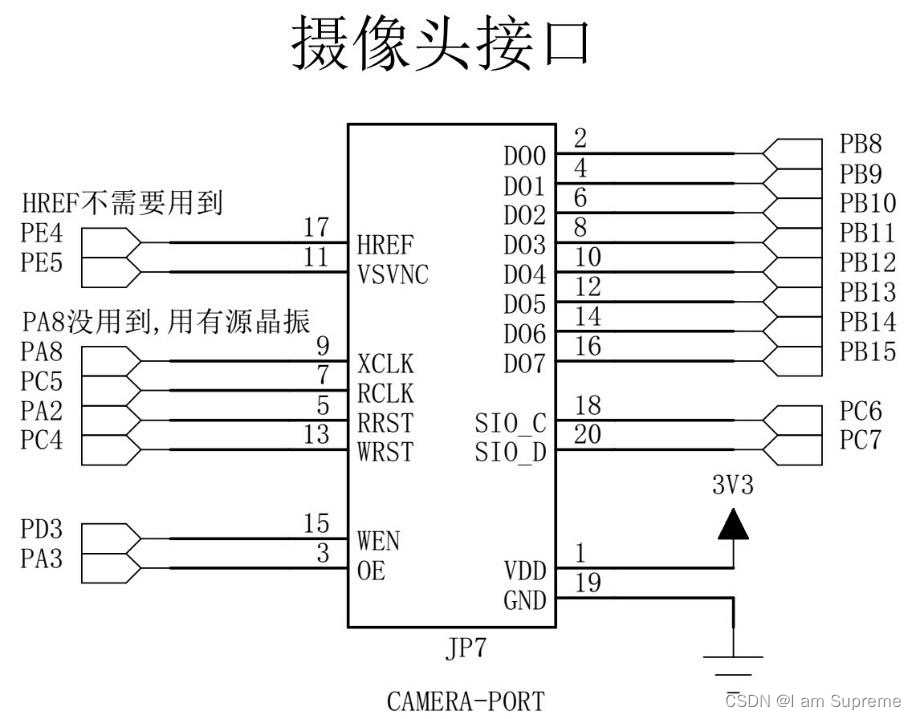

关于摄像头的原理图此处不再分析。在我们的实验板上有引出一个摄像头专用的排母,可直接与摄像头引出的引脚连,接入后它与STM32 引脚的连接关系见图

摄像头与STM32 连接关系中主要分为SCCB 控制、VGA 时序控制、FIFO 数据读取部分,介绍如下:

(1) SCCB 控制相关

摄像头中的SIO_C 和SIO_D 引脚直接连接到STM32 普通的GPIO,它们不具有硬件I2C 的功能,所以在后面的代码中采用模拟I2C 时序,实际上直接使用硬件I2C 是完全可以实现SCCB 协议的,本设计采用模拟I2C 是芯片资源分配妥协的结果。

(2) VGA 时序相关

检测VGA 时序的HREF、VSYNC 引脚,它们与STM32 连接的GPIO 均设置为输入模

式,其中HREF 在本实验中并没有使用,它已经通过摄像头内部的与非门控制了FIFO 的写

使能;VSYNC 与STM32 连接的GPIO 引脚会在程序中配置成中断模式,STM32 利用该中

断信号获知新的图像是否采集完成,从而控制FIFO 是否写使能。

(3) FIFO 相关

与FIFO 控制相关的RCLK、RRST、WRST、WEN 及OE 与STM32 连接的引脚均直接配置成推挽输出,STM32 根据图像的采集情况利用这些引脚控制FIFO;读取FIFO 数据内容使用的数据引脚DO[0:7]均连接到STM32 同一个GPIO端口连续的高8 位引脚PB[8:15],这些引脚使用时均配置成输入,程序设计中直接读取GPIO端口的高8 位状态直接获取一个字节的FIFO 内容,建议在连接这部分数据信号时,参考本设计采用同一个GPIO 端口连续的8 位(高8 位或低8 位均可),否则会导致读取数据的程序非常复杂。

(4) XCLK 信号

本设计中STM32 的摄像头接口还预留了PA8 引脚用于与摄像头的XCLK连接,STM32的PA8 可以对外输出时钟信号,所以在使用不带晶振的摄像头时,可以通过该引脚给摄像头提供时钟,秉火摄像头内部已自带晶振,在程序中没有使用PA8 引脚。以上原理图可查阅《霸道开发板—原理图》文档获知,请根据实际连接的引脚修改程序。

剩下明天更新!!!!

这篇关于OV7725 摄像头驱动的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!