本文主要是介绍UCIE协议介绍--芯粒间互联标准,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

UCIE协议介绍--芯粒间互联标准

- 1 背景

- 2 UCIE协议介绍

- 2.1 协议层

- 2.2 适配层

- 2.3 物理层

- 2.4 D2D接口

- 3 Transmission

- 3.1 SideBand数据包

- 3.2 SideBand包格式

- 3.2.1 MRd/Mwr/CfgRd/CfgWr

- 3.2.2 Completion

- 3.2.3 Message

- 3.3 FDI接口信号

- 4 链路训练

- 4.1 PHY LSM状态介绍

1 背景

为什么发展出芯片互联技术,从而才会有芯片互联的协议标准推出;UCIE:Universal Chiplet Internet Express.

面临:1.摩尔定律失效,不能无限制趋于小;2.降低成本,方便复用,多制程Die封装;

想象成搭积木拼接的样子,有的大粒度的积木,有的小粒度的积木,进行拼接起来

类比来看:UCIE考验的是芯粒之间进行封装;

UCIE创立的宗旨就是建立Chiplet生态开放生态;

2 UCIE协议介绍

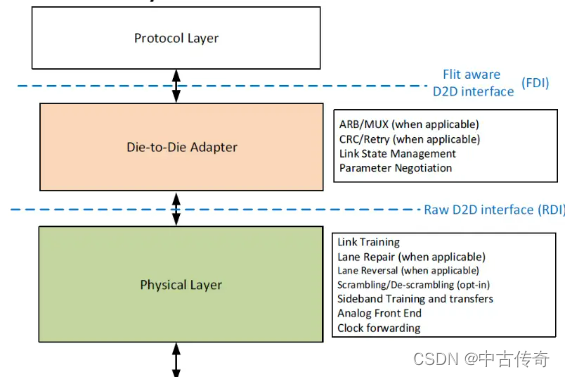

UCIE协议是一个规范标准,是基于分层的协议,其协议层各司其职,便于通用和复用,明确每层要支持的功能;

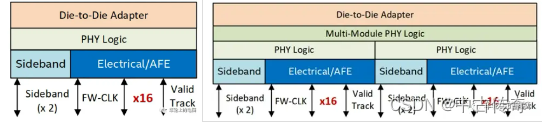

按照层级可分为:PHY层、Adapter层和Protocal层;PHY层和Adapter层之间接口为RDI;Adapter层和Protocol层之间接口为FDI;

2.1 协议层

区分协议概念VS Mode概念

- UCIE协议层支持PCIE6.0、CXL2.0/3.0协议,同时还支持Steaming协议(用来映射其他传输协议);支持自定义协议适配

- Raw Mode:PCIE6.0、CXL2.0/3.0都支持一种模式叫Raw Mode,用于自定义的Streaming协议只支持RAW Mode,在这模式下,所有64B或者256B数据都由协议层来负责填充,bypass适配层,CRC、FEC和Retry都由协议层来处理;

- Flit Mode:适配层要对协议层进行添加做2B hdr和2B CRC;协商过程中,适配层通过FDI接口把这些信息作为Link Trainning的一部分传给协议层;

2.2 适配层

当协议层发送64B Flit数据,会在前加上2B hdr(Protocol ID,Stack ID)和后面加上2B CRC值;对于256B Flit需要额外增加2B CRC;

适配层主要功能:CRC、FEC、Retry;CRC最多可以检测3bit错误;

2.3 物理层

物理层分为逻辑物理层和电气物理层;我们只需要关注逻辑物理层:即Lane概念;

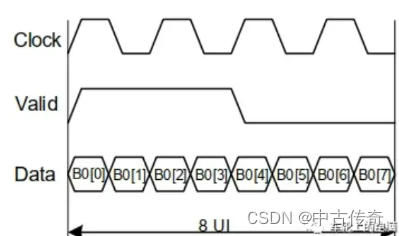

数据包是通过Byte形式发出的,一个Byte占用一个Lane使用4个clk传输;Main_band采用DDR的双沿采样;

2.4 D2D接口

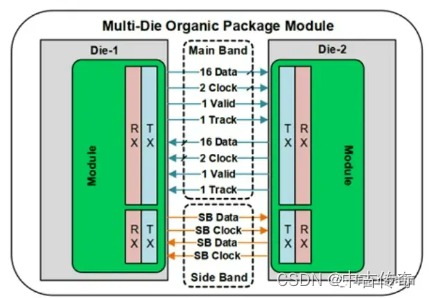

一个标准封装的UCIE module信号线即为下图所示:MainBand有16个TX Data Lane和16个RX Data Lane(先进封装对应64Lane);SideBand是一个x1 Data Lane;

Module UCIE 可以允许x1, x2和x4的配置,即MainBand+SideBand;

3 Transmission

UCIe 提供了两大数据通路:Mainband 及 Sideband。Mainband 用来传输业务数据流,Sideband 用来来处理一些 链路训练、链路管理、参数交换及寄存器访问 等非数据传输业务。Sideband 作为 Mainband 的 Back Channel,能够简化UCIE中的链路训练、链路管理和D2D参数交换,简化数据链路的建立过程、提升 Mainband 的带宽利用率、简化 Mainband 设计复杂度。

除了常规意义上的 Die 间 UCIe Link Sideband,UCIe 还有 FDI Sideband 及 RDI Sideband,在不同层次间传递边带信息。

UCIe 支持类似于 PCIe 的 4 种数据包,包括配置读写、内存读写、Completion 及 Message。

- 对MB来说 DDR双沿采样:传输业务数据流,比如256B Flit数据传输,对于标准封装x16来说:8个UI传输1个Byte,现在16Lane:256B = 1Byte/(8UI*1Lane) * 16Lane * 128UI;

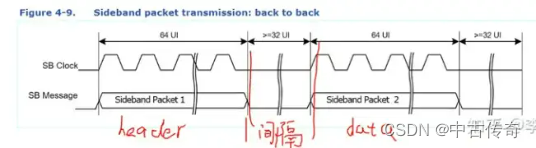

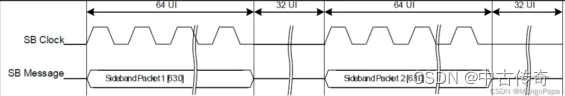

- 对SB来说 单沿采样(SB clk固定为800M):Serial frame/packet(没有明确区分),Sideband的一个帧是64bit数据,第一帧是64bit header,间隔至少32bits的’0’(无时钟), 然后是第二帧64bit data。如果数据是32bits,第二个数据帧需要MSB补零形成64bits.

UCIe Sideband 在 D2D 参数交换、链路训练、链路管理及寄存器访问方面发挥着不可或缺的作用,但无论是实现哪一方面功能,UCIe Sideband 能够做的方式就是:① 寄存器访问;② Message 传递; - 寄存器访问:

- Message传递:

3.1 SideBand数据包

UCIe Sideband 支持 4 种不同的数据包:① 配置读写(CfgRd/Wr)、② 内存读写(MRd/Wr)、③ 完成(Cpl/Cpld)及 ④ 消息(Msg/MsgD)。

分类:

- 配置读写及内存读写都是用于寄存器访问,区别在于寄存器位于配置空间还是 MMIO 空间。若访问 UCIe 配置空间内的寄存器,比如 Host Die 访问 EP UCIe Link DVSEC 内的寄存器,则采用 CfgRd/Wr;若访问其他 MMIO 区域的寄存器,比如 D2D Adapter 内的寄存器,则采用 MRd/Wr。 根据寄存器数据位宽的不同,寄存器访问请求又可以分为 32bit 及 64bit。

- Completion 一般对应寄存器访问请求的 Response。根据是否携带数据及返回数据的位宽不同,Completion 可以分为不带数据的 Cpl 及携带数据的 CplD,CplD 又分 32bit 数据及 64bit 数据。这里的 32/64bit 跟 PCIe 稍有不同,PCIe 中 32/64 bit 是指地址位宽,在 UCIe 中是指寄存器数据位宽。

- Message 一般用于 D2D 间参数交换、链路训练、链路管理及其他 Vendor 自定义的场景。根据是否携带数据,消息分为 Msg 及 MsgD。

跟 PCIe TLP Header 的 FMT+Type 字段类似,UCIe 通过 Sideband Packet 中的操作码(Opcode)来区分是哪种类型的 Sideband 数据包、是否携带数据、地址数据的位宽。

3.2 SideBand包格式

每一笔 Sideband Message 都由 64bit Header + 32 或 64bit Data 组成。若 Data 为 32bit,需要高位补 0 到 64bit。发送串行数据时,每 64bit 为 1 个 Packet,相邻 Packet 之间插入 32bit 0 以分隔不同的 Packet。每个 Clock Cycle 发送 1bit Sideband 数据,下降沿采样。

以位宽 32bit 的 FDI/RDI Sideband 数据接口为例,介绍下 Sideband 的数据格式。

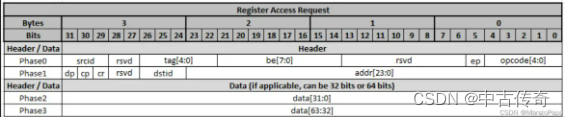

3.2.1 MRd/Mwr/CfgRd/CfgWr

寄存器访问请求的SideBand帧格式如下图所示:

重点介绍的几个字段:

- srcid 及 dstid 表明了 Sideband 寄存器请求的来源及目的地(协议层、Adapter、物理层,Local、Remote);

- tag 是 Requester 添加的标签,用以将 Outstanding 请求跟响应相对应;

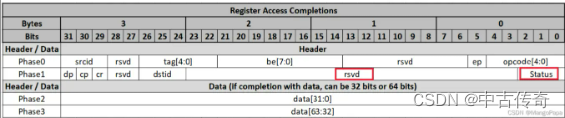

3.2.2 Completion

Completion 的 Sideband 帧格式如图 3 所示,其跟寄存器访问请求大同小异,其中有几点不同:

- Status,表明当前 Completion 的状态,包括 Success、UR、CA、Stall 四种状态。

- Completion 在 FDI 上的去向不依赖于 dstid 而是依赖于 tag。没有 addr 地址字段。

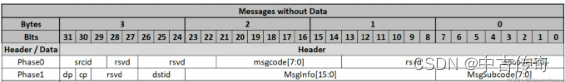

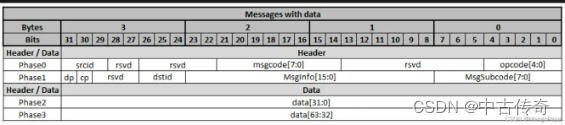

3.2.3 Message

带 Data Payload 和不带 Data 的 Message Sideband 帧格式如下图所示。比较关键的几个字段位 MsgCode、MsgSubcode、MsgInfo

3.3 FDI接口信号

MainBand

SideBand

Link State Management

4 链路训练

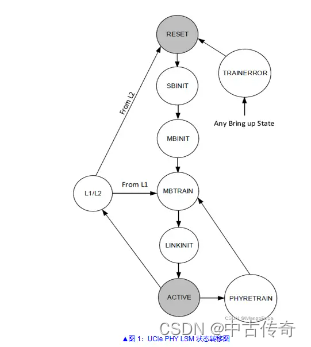

UCIE中很重要的链路训练–UCIE LSM即链路状态机理解;UCIE采用分层的LSM:FDI FSM、RDI FSM和PHY LSM。

其中FDI/RDI LSM用于UCIE链路管理,PHY LSM主要用于UCIE链路初始化及训练

4.1 PHY LSM状态介绍

UCIE PHY LSM包含10大状态,各状态及主要功能如下:

- RESET,复位状态,是系统复位后或 UCIe 退出 TRAINERROR 后的状态。

- SBINIT,Sideband 初始化,在该状态对 Sideband 进行初始化,选择可用的 SB Lane。

- MBINIT,Mainband 初始化,在该状态对 Mainband 进行初始化、修复坏的 MB Lane。该状态下 Mainband 处于最低速。

- MBTRAIN,Mainband 训练,在该状态对 Mainband 的 Clock、Valid、Data 等 Lane 进行训练,使得 UCIe 链路工作在链路两端设备协商* 好的最高速或协商速率之下物理所能达到的最高速。跟 PCIe 不同,PCIe 是从 Gen1 最低速开始一点点往最高速进行训练的,但 UCIe 除了在初始化的时候为最低速,其在 MBTRAIN 状态对 Mainband 进行训练时一次切速到最高速进行训练,训练失败的话再进行降速或者减宽。

- LINKINIT,链路管理状态,用以 D2D Adapter 完成初始链路管理。该状态时,进行 RDI Bring Up。

- ACTIVE,UCIe 的正常工作状态,该状态时进行 Mainband 的数据传输,对应 PCIe 的 L0 状态。

- L1/L2低功耗状态,处于这两种状态下的 UCIe Module 功耗较低,处于 L2 状态的 UCIe Module 比 L1 睡眠程度更深、功耗更低。L1 可以直接退出到 MBTRAIN 状态,免去 SBINIT 及 MBINIT 的过程,但 L2 只能退出到 RESET 状态,重新进行链路的初始化。

- PHYRETRAIN,需要重新对链路进行链路初始化及训练时,进入该状态。

- TRAINERROR,链路训练失败后进入该状态。

在 PHY 的初始化及训练过程中,Sideband、Mainband 是分开进行初始化和训练的。首先对 Sideband 进行初始化,使 Sideband 进入正常工作状态,便于后续初始化及训练过程中在 UCIe Link 上传递 Sideband Msg;然后进行 Mainband 初始化,UCIe Link 两侧的 Module 进行参数交换及协商、链路修复等工作,使 Mainband 能够工作在最低速(4 GT/s)。

Timeout机制:除了RESET和TRAINEERROR之外,所有状态都有个8ms超时退出机制

【Ref】

[1] https://new.qq.com/rain/a/20220616A073AH00

[2] https://developer.aliyun.com/article/1073772

[3] https://blog.csdn.net/weixin_40357487/article/details/127362477

这篇关于UCIE协议介绍--芯粒间互联标准的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!