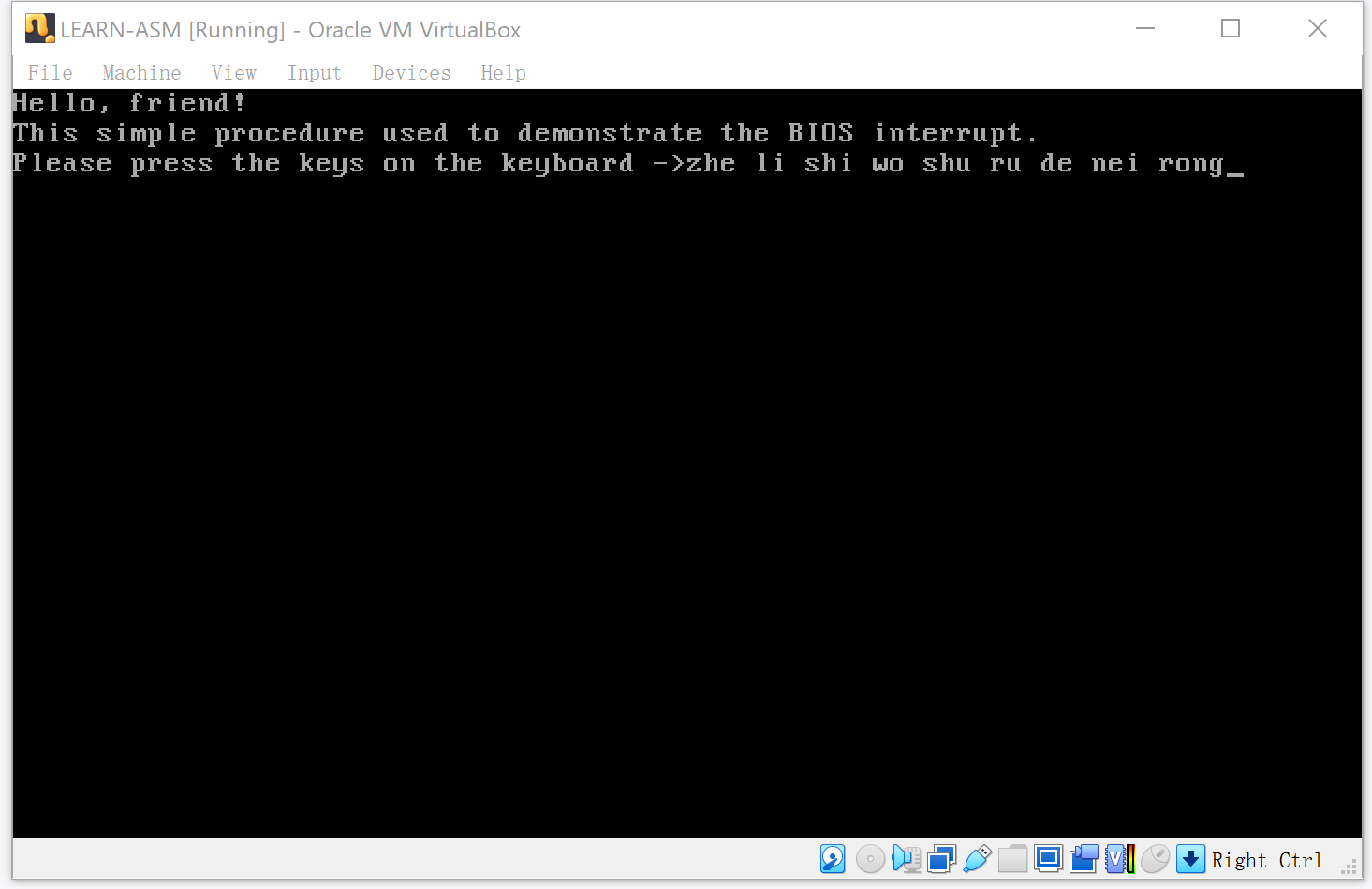

本文主要是介绍实验九 基于FPGA的计数译码显示电路设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

基本任务一:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW4-7控制数码管位选

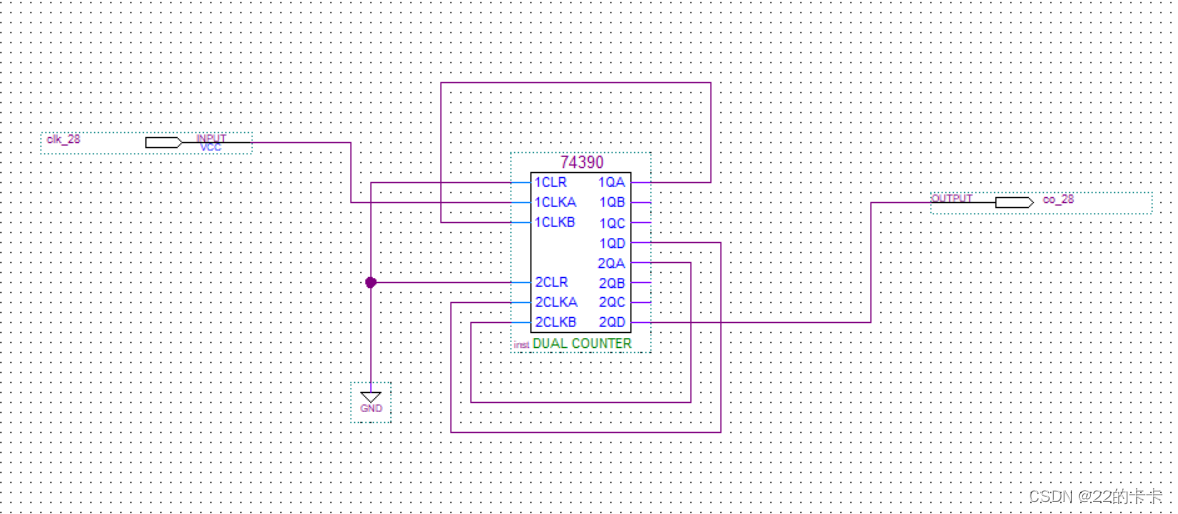

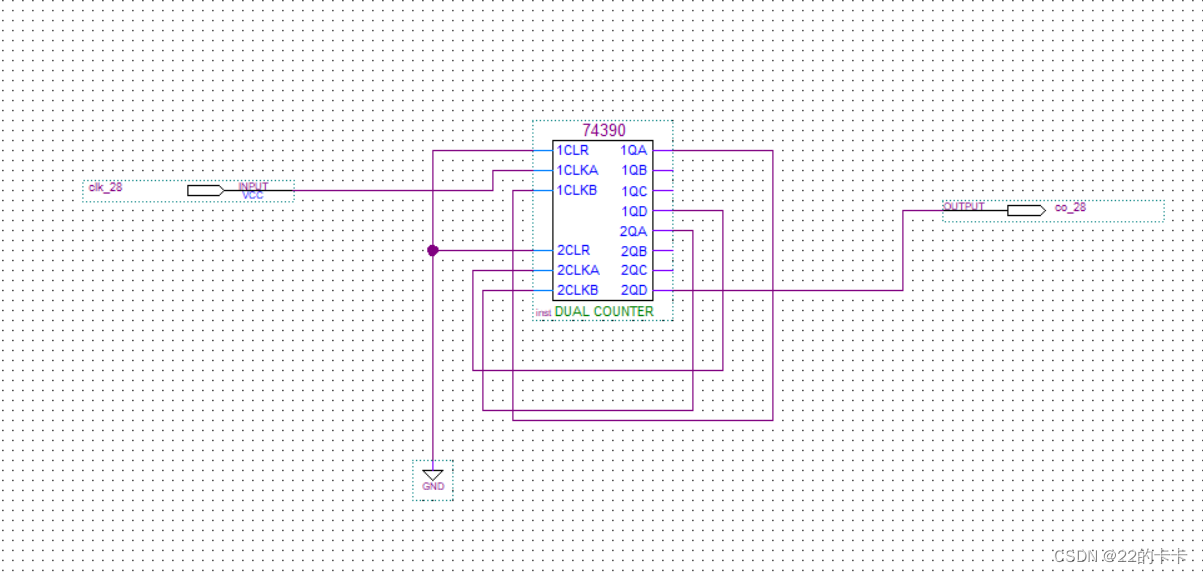

m100:

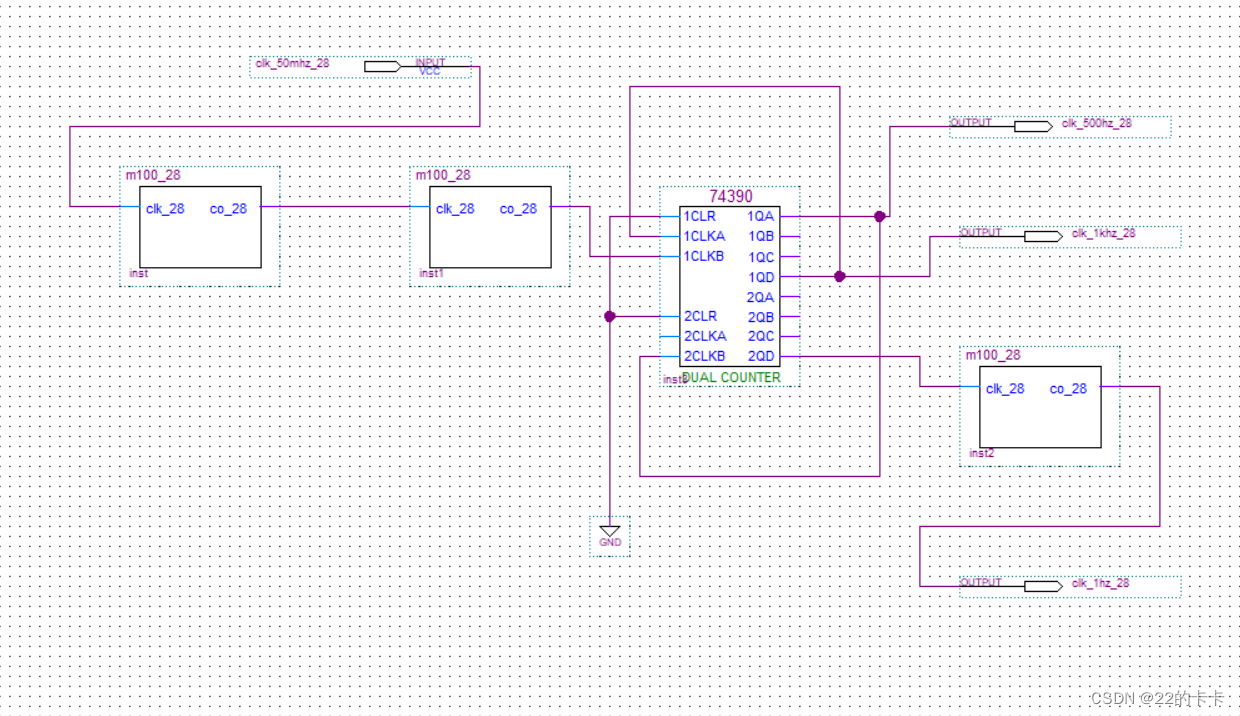

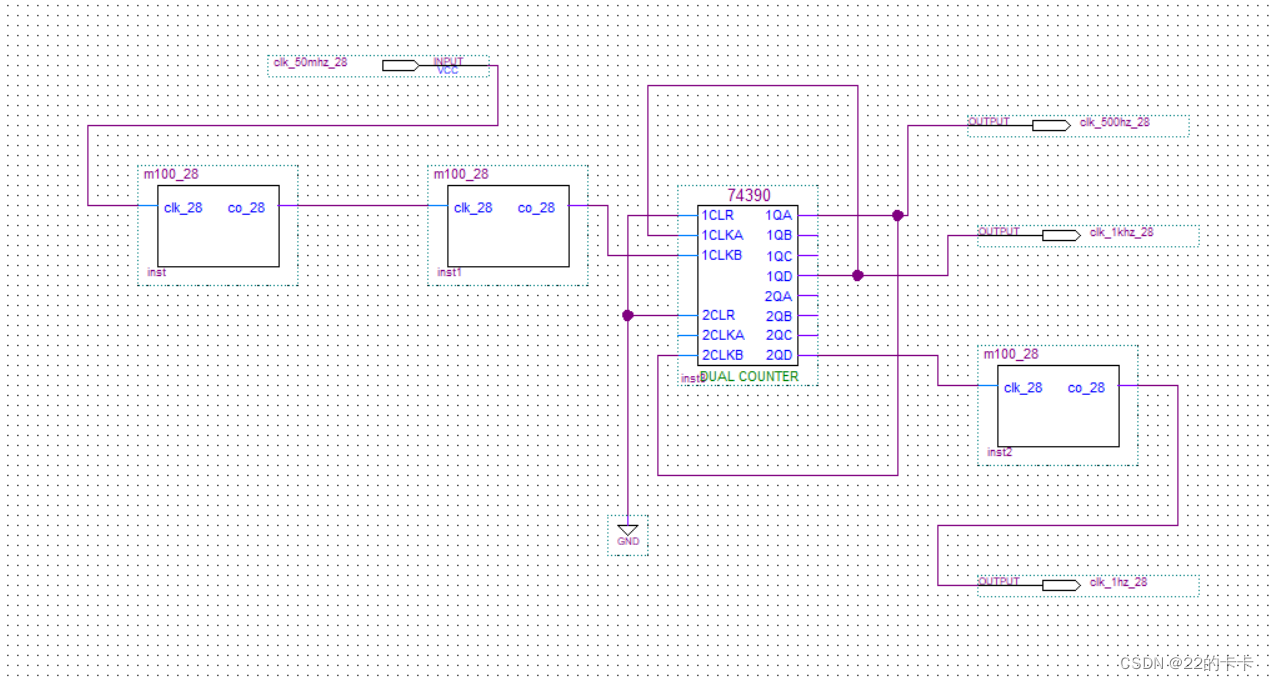

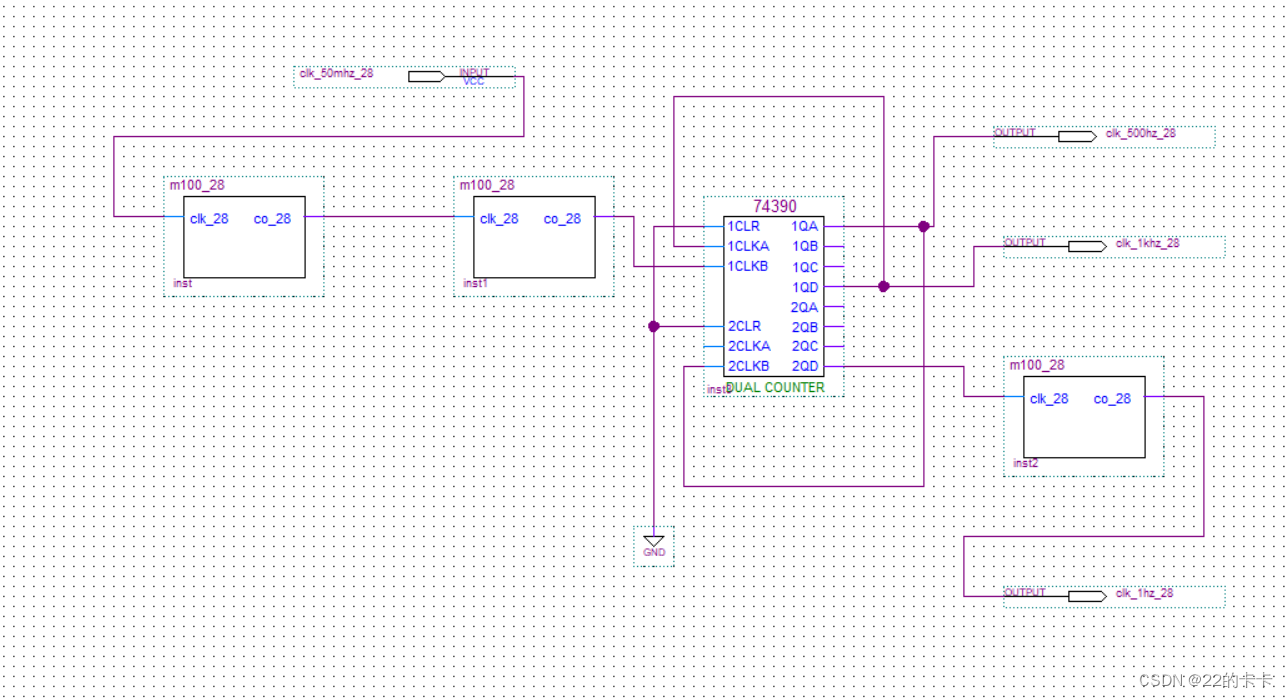

frediv:

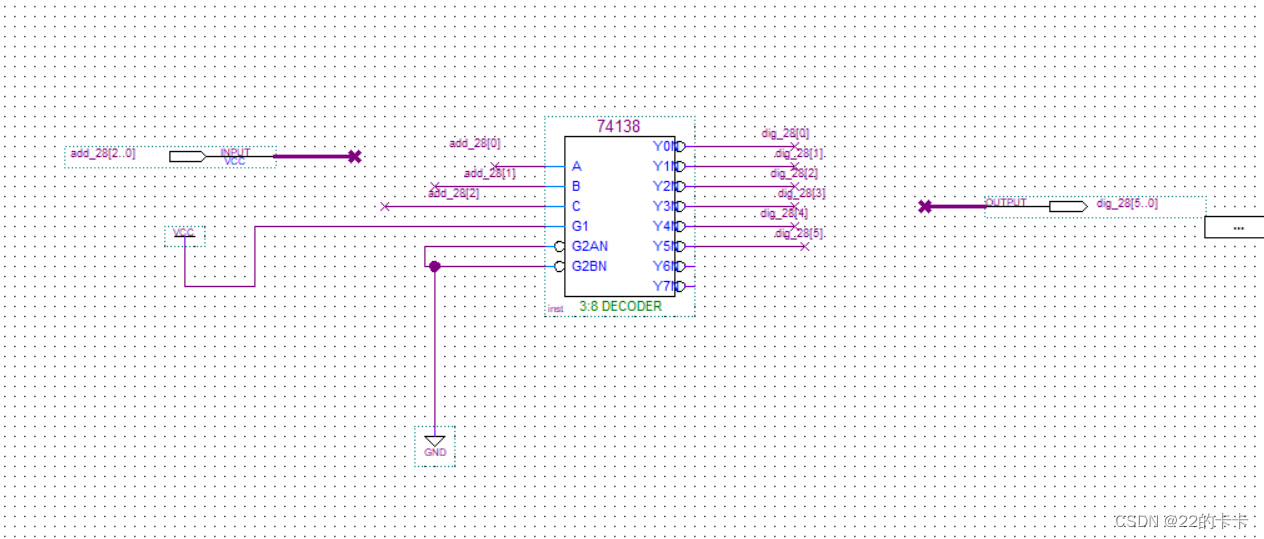

decoder:

基本任务二:利用FPGA硬件平台上的4位数码管显示m10技术结果

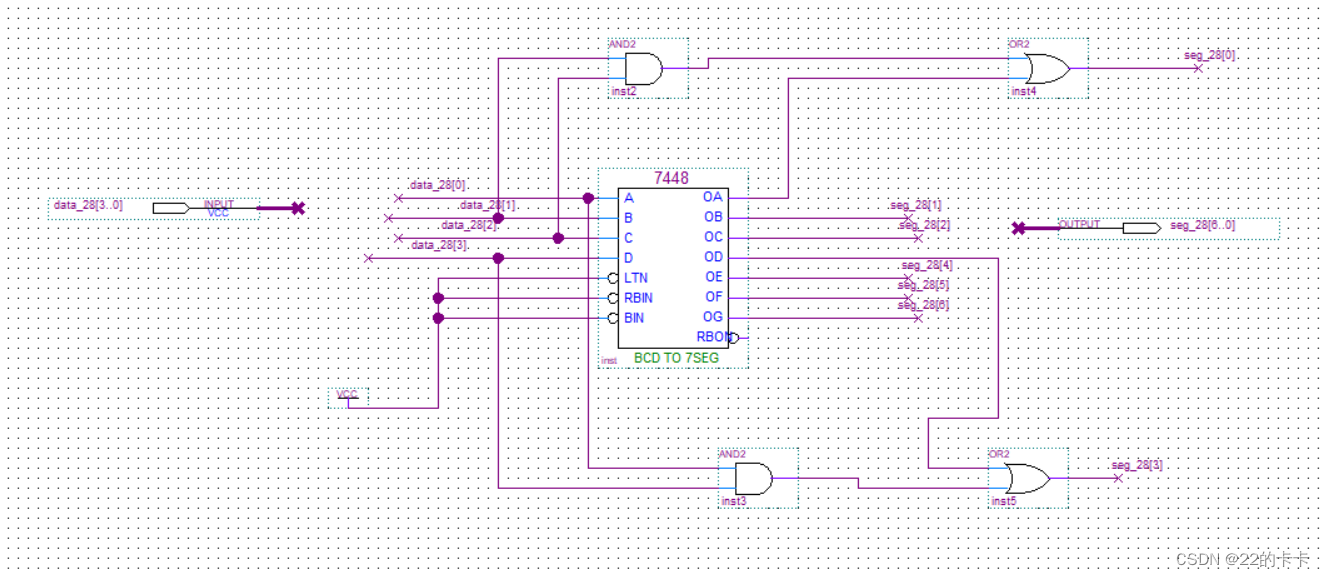

扩展任务一:对7448译码的6和9进行补段

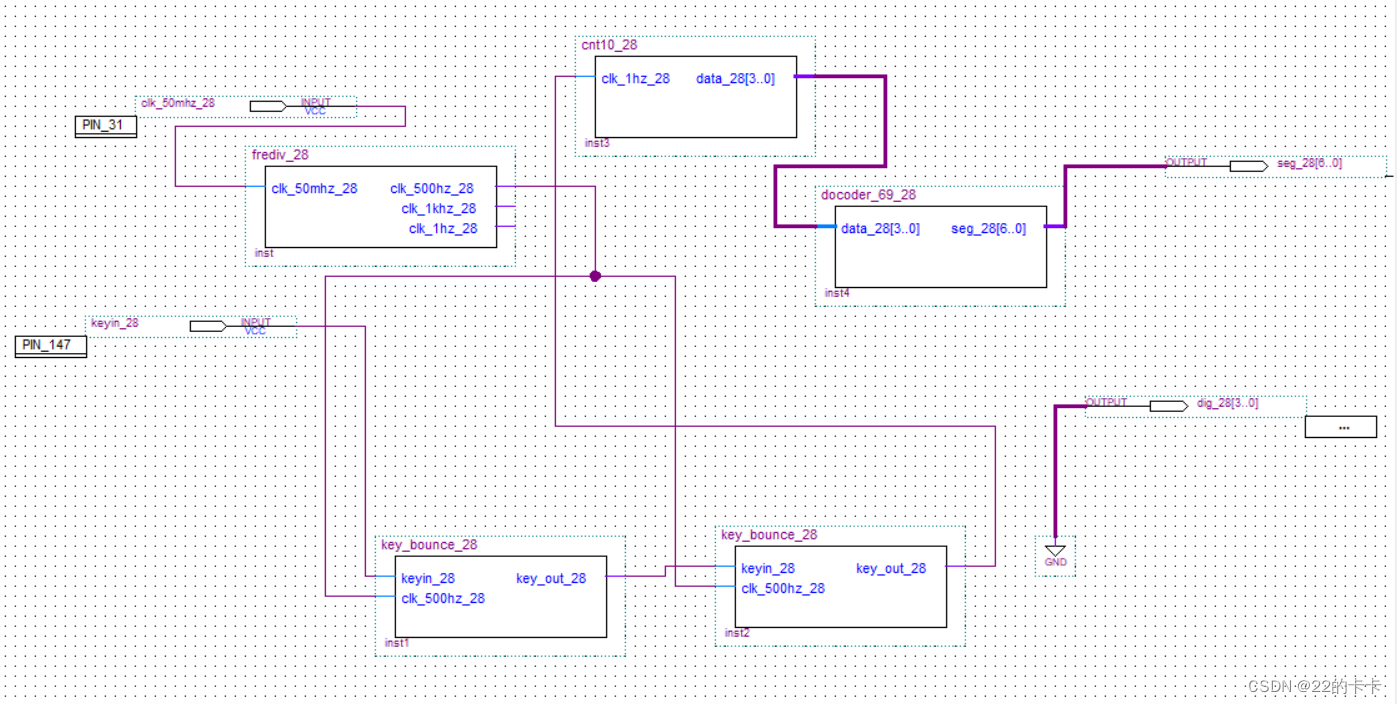

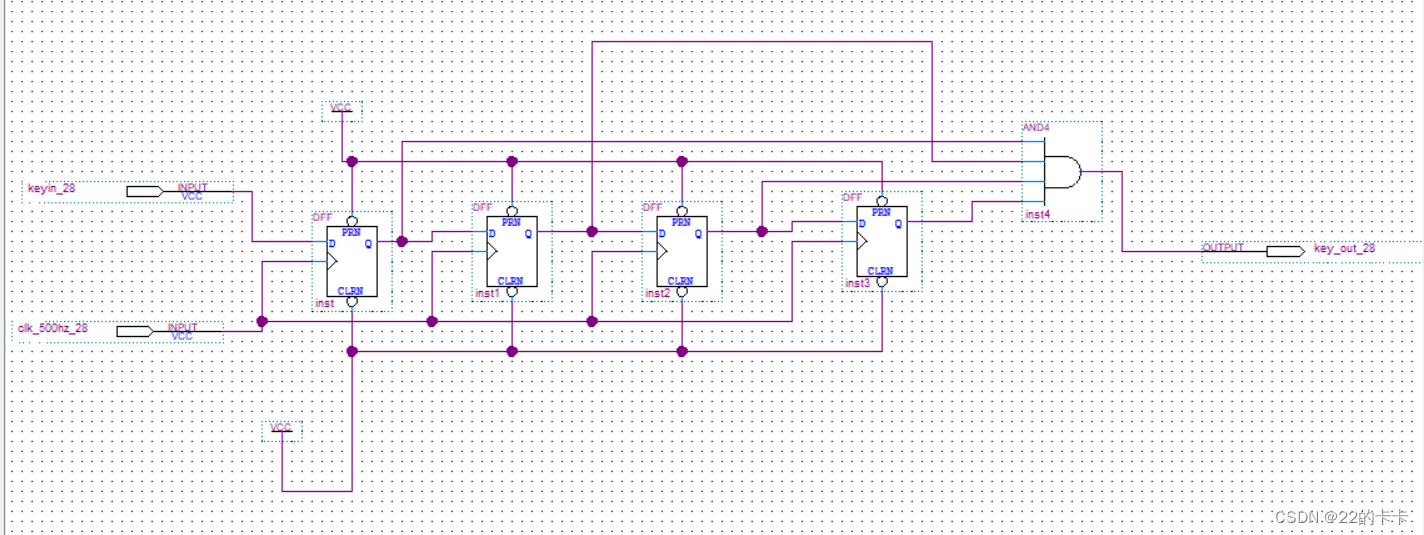

扩展任务二:用按键控制计数器从0-9计数,4位数码管显示技术结果。

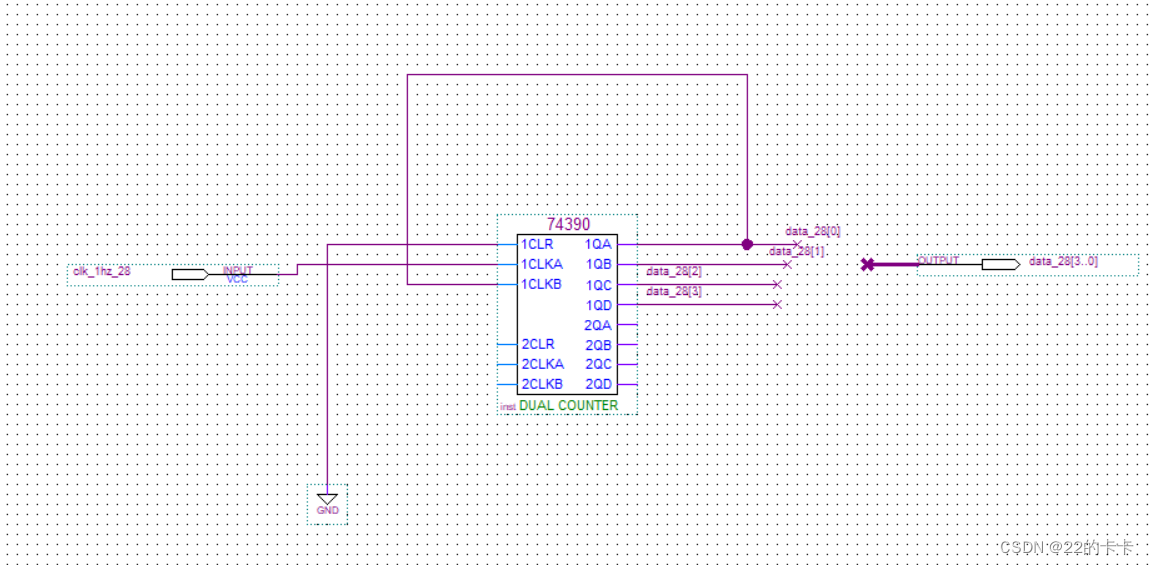

cnt10:

decoder69:

key_bounce:

frediv:

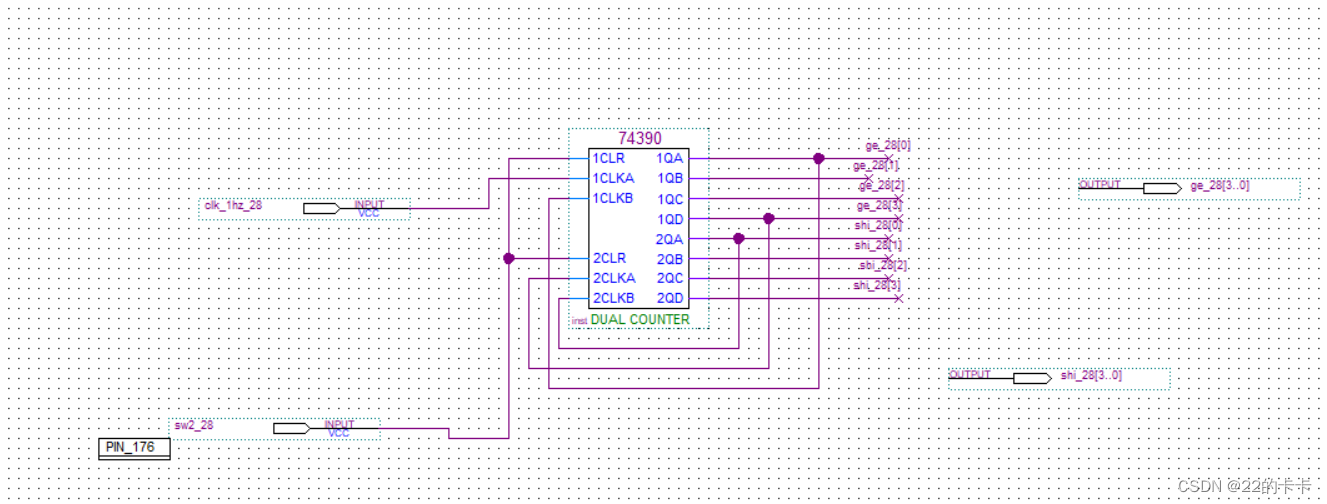

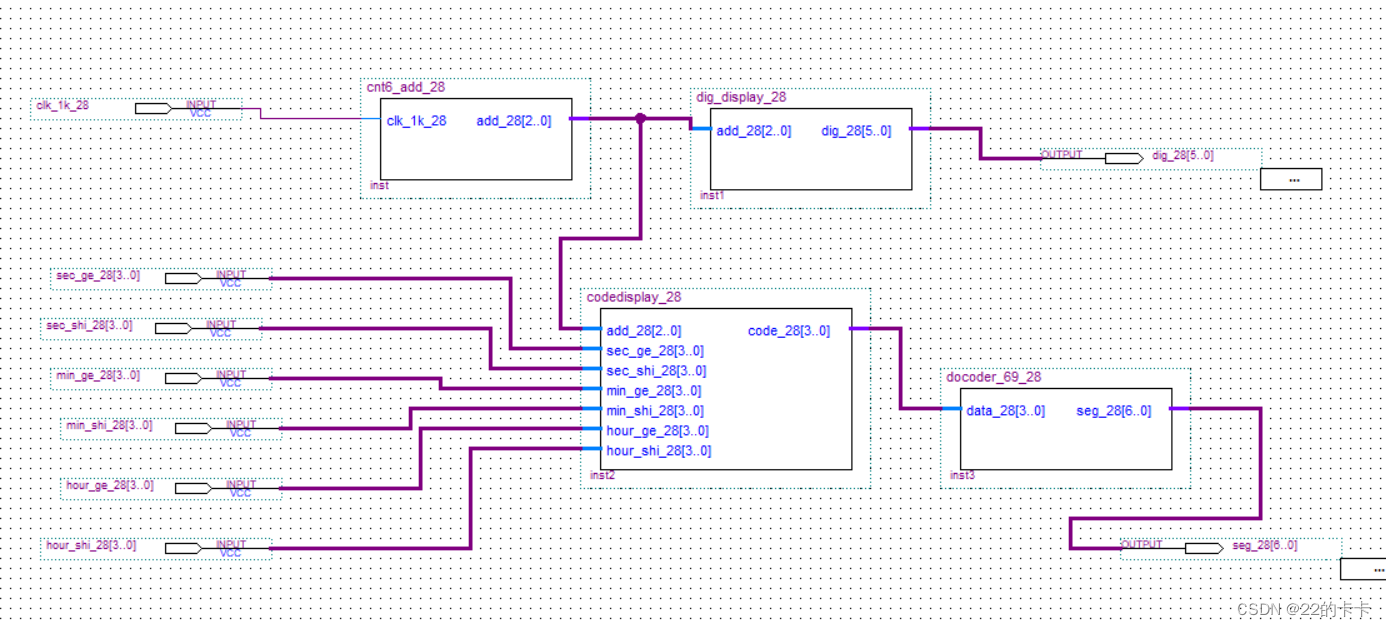

基本任务三:利用FPGA硬件平台上的6位数码管显示模100计数结果。

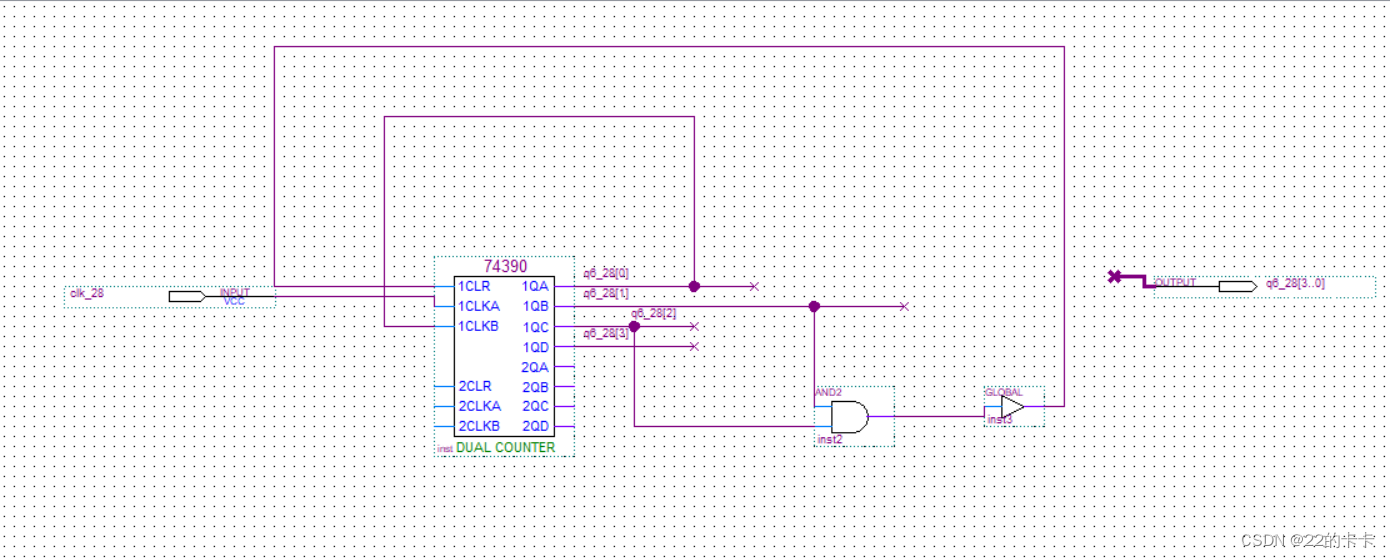

cnt6:

m100:

frediv:

decoder——69:

m100_2output:

dig_select:

code_select:

display_m100:

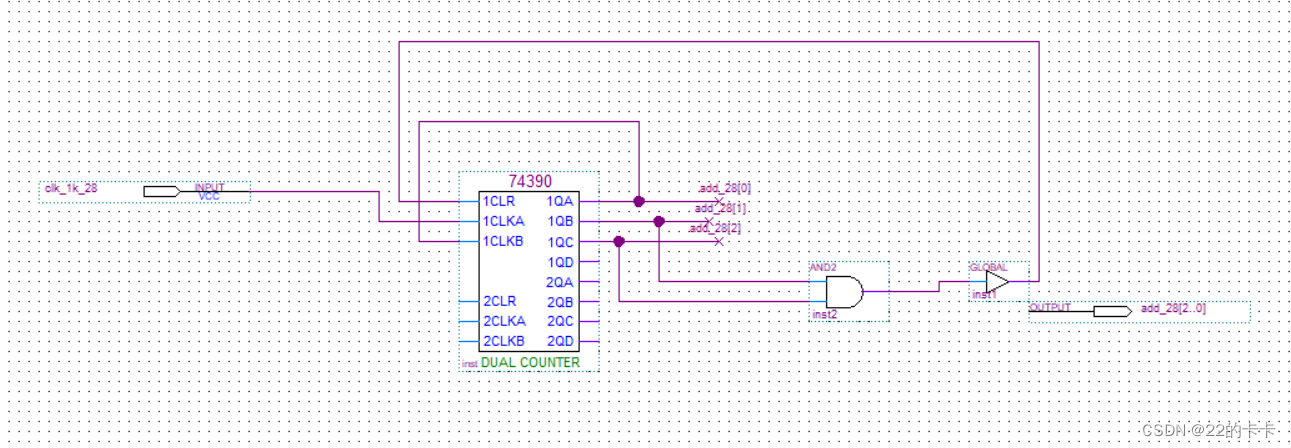

cnt6_add

这篇关于实验九 基于FPGA的计数译码显示电路设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![C#实战|大乐透选号器[6]:实现实时显示已选择的红蓝球数量](https://i-blog.csdnimg.cn/direct/cda2638386c64e8d80479ab11fcb14a9.png)