本文主要是介绍PCIe AER(一),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

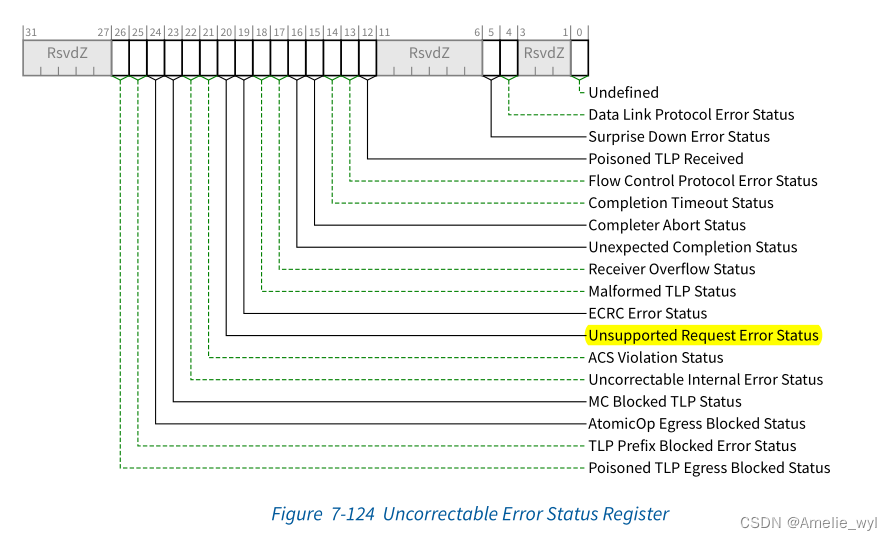

1、AER status register

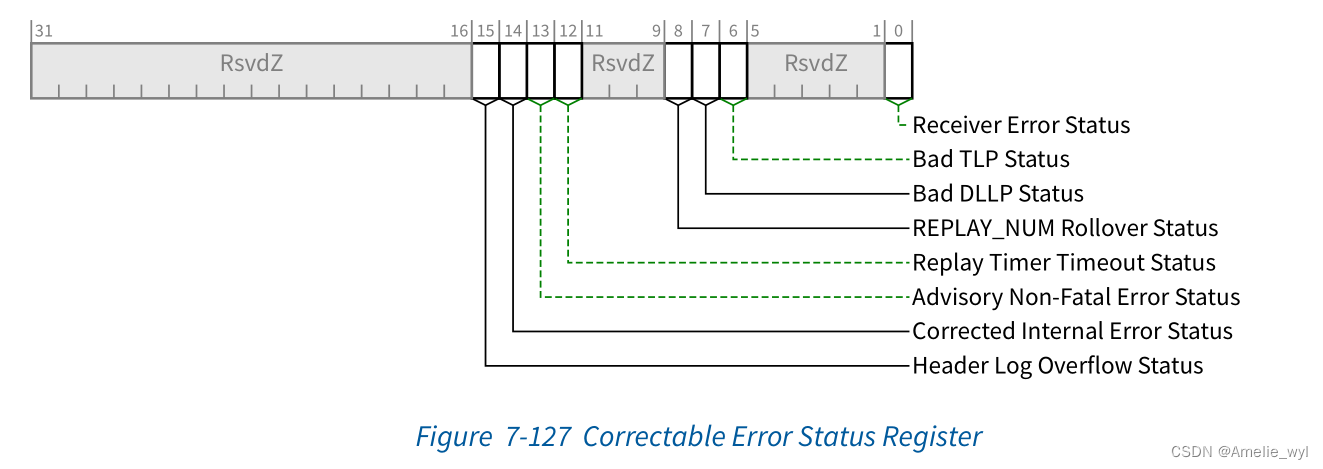

1.1 correct error每个bit的介绍(spec 6.2.7)

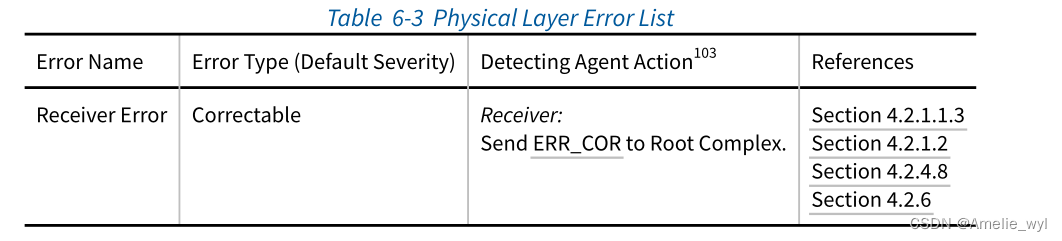

1.1.1 Receiver Error Status

表格后面的reference;

4.2.1.1.3

If a received Symbol is found in the column corresponding to the incorrect running disparity or if the Symbol does not correspond to either column, the Physical Layer must notify the Data Link Layer that the received Symbol is invalid. This is a Receiver Error, and is a reported error associated with the Port (see Section 6.2 )

4.2.1.2

4.2.4.8

4.2.6

总结:4.2.1.1.3指出如果8b/10b编码中出现symbol的disparity错误或者symbol本身错误,这是一种receiver error;

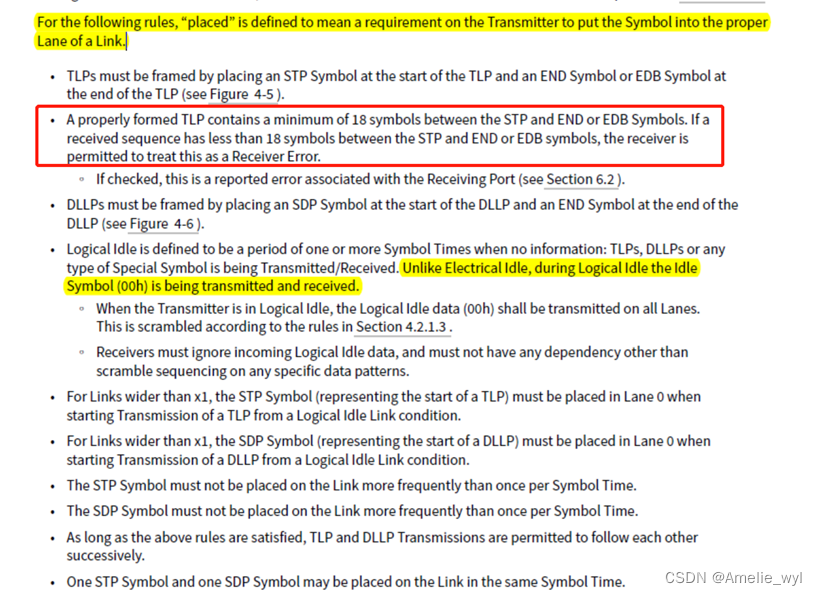

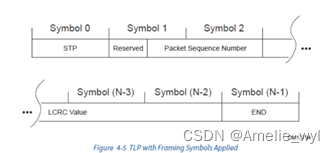

4.2.1.2指出,一条规则,一个正确的TLP 在STP symbol和 END/EBD中间至少有18个symbol(1DW = 4symbol,18symbol,如果TLP header是3DW,LCRC 4symbol,还剩下2symbol=1DW 的data; 如果header 是4DW,LCRC是2symbol,就没有data?3DW header 主要是32bit的memory/IO request,Config Request,这些都要携带data,completion呢??? )

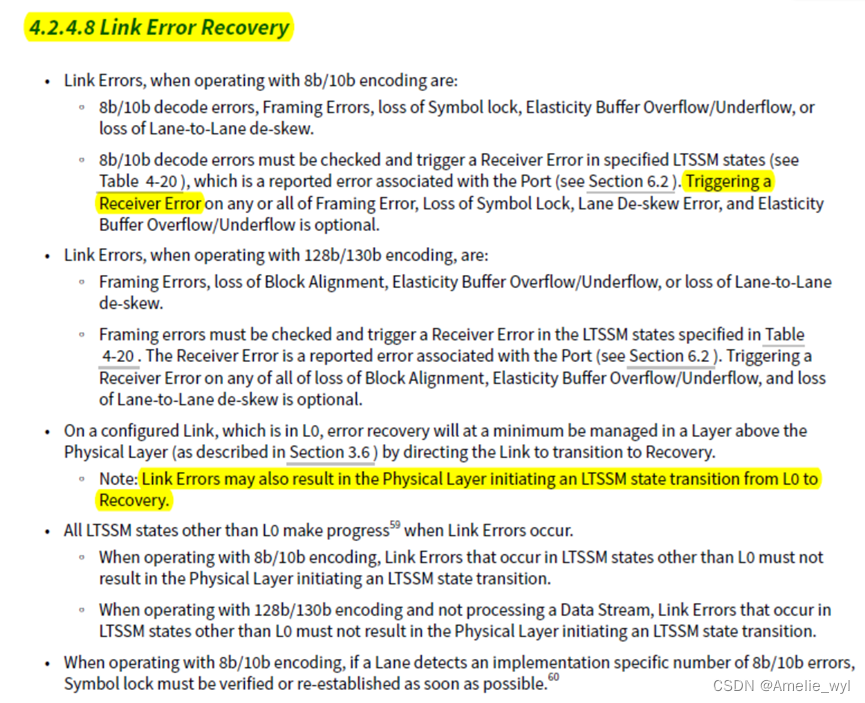

4.2.4.8 指出了8b/10b 中receiver error,128b/130b 中的receiver error(8b/10b decode errors, Framing Errors, loss of Symbol lock, Elasticity Buffer Overflow/Underflow, or loss of Lane-to-Lane de-skew. 128b/130b:Framing Errors, loss of Block Alignment, Elasticity Buffer Overflow/Underflow, or loss of Lane-to-Lane de-skew)

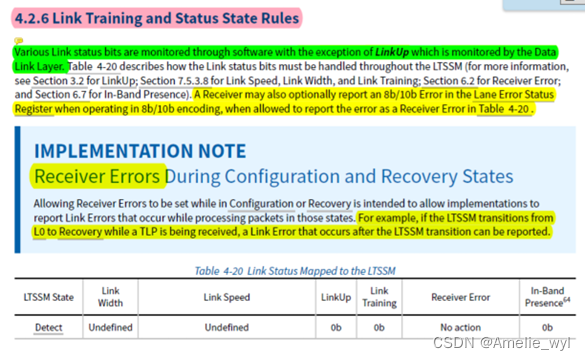

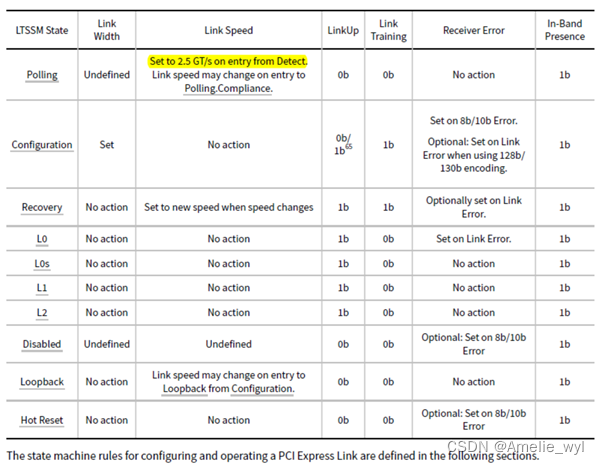

4.2.6 的重点是table 4-20,在LTSSM的哪个阶段会检查receiver error;

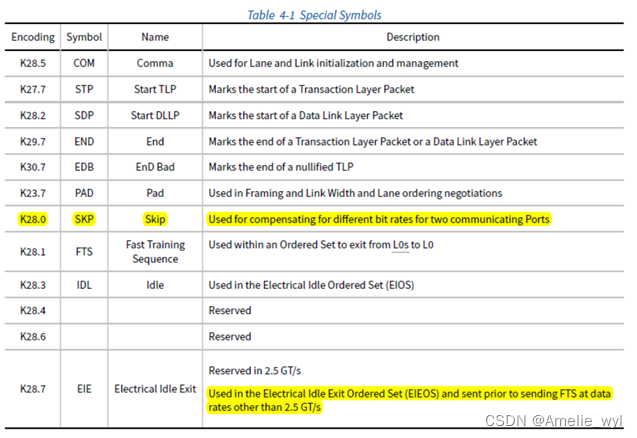

其中有一些概念:symbol,可以理解为固定格式的8bit数据,参考spec table 4-1,附录B,8b/10b编码后会有RD-/RD+(CRD: Current Running Disparity)两种10bit格式,为了保持均衡性,RD后面要跟相反的RD,学习链接:

(2条消息) #PCIe# 为什么引入编码机制?_pcie disparity_那么菜的博客-CSDN博客

还有receiver error中的其他概念也需要学习(Elasticity Buffer Overflow/Underflow, or loss of Lane-to-Lane de-skew),暂时还没找到具体资料

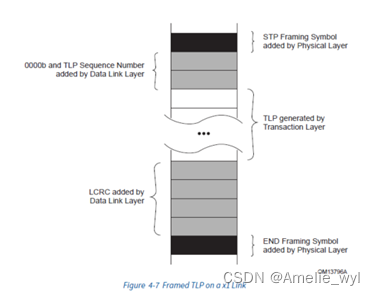

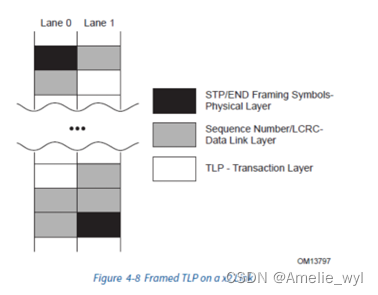

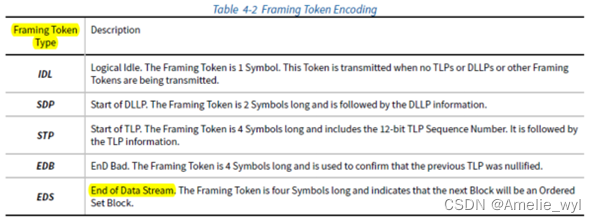

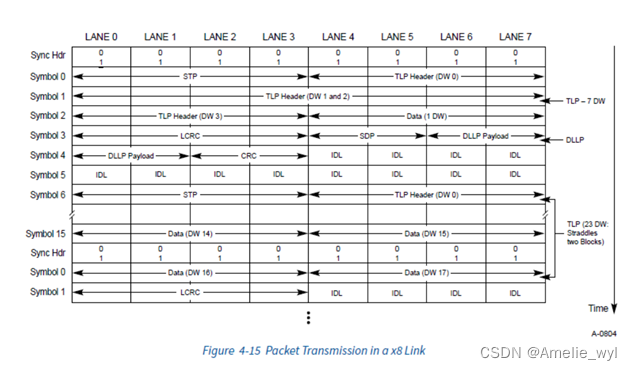

其中对于TLP在lane上的传输格式,要区分gen1/gen2和gen3/gen4,因为编码方式不一样,导致了差异性,其中gen1/gen2

TLP之前的STP&PSN 占3symbol, STP,PSN都是symbol,但是gen3/gen4DLLP或者TLP的开始不再是一个symbol,而是一个token(具体格式,spec fig 4-13),但是为什么gen3/gen4要这样呢,为了block更好对齐吗???

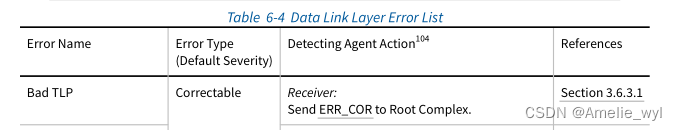

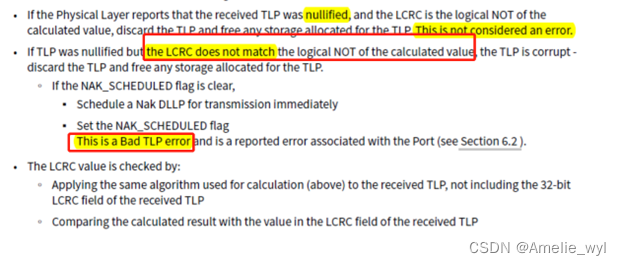

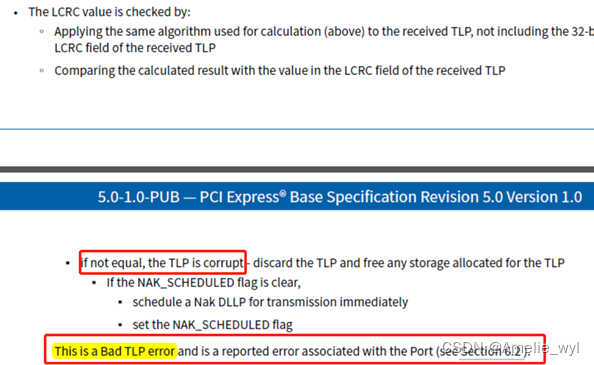

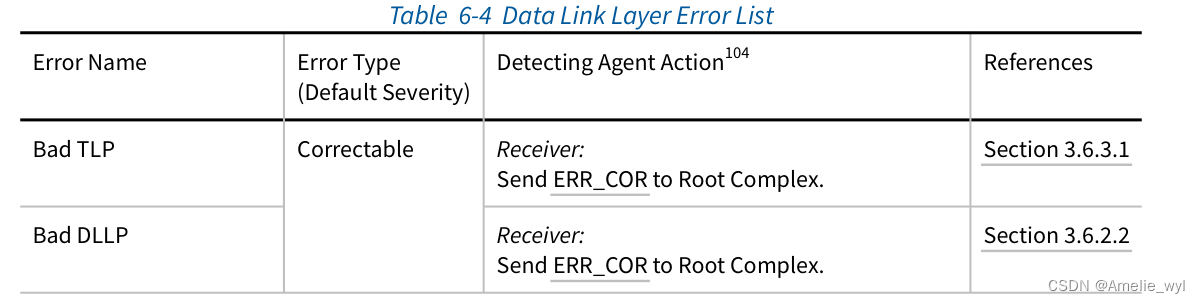

1.1.2 Bad TLP

总结:LCRC出错

实际系统测试中,如果链路有问题(phy),但是没有引起其他不可修复错误,这个时候也可能引起其他correctable error置位,比如出现Bad TLP(如果引起replay错误,除非逻辑有问题,不然链路就很差了)

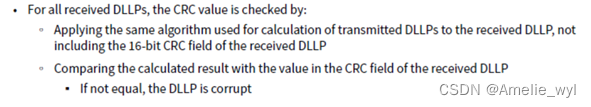

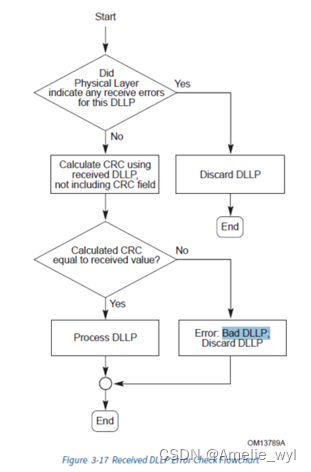

1.1.3 Bad DLLP

总结:CRC错误

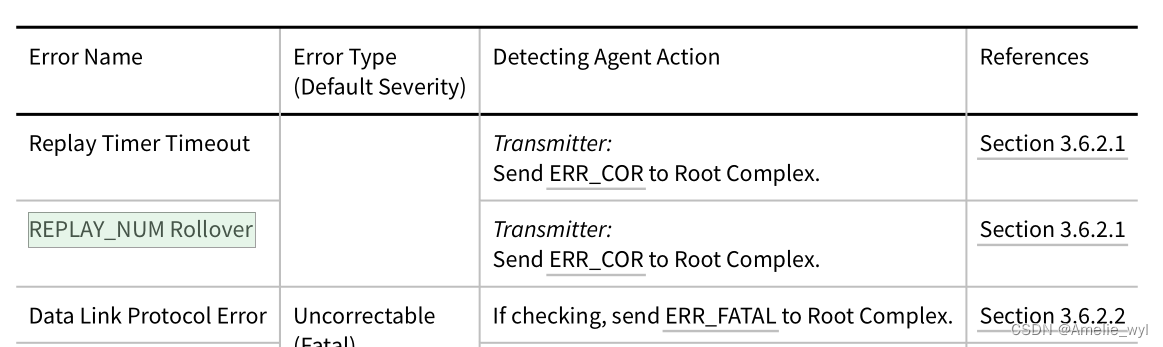

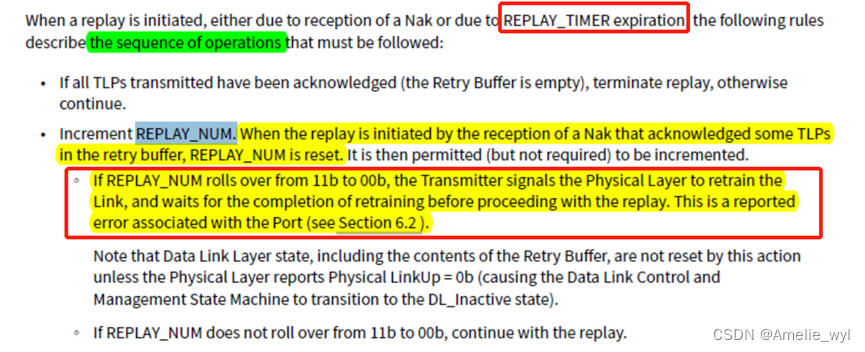

1.1.4 REPLAY_NUM Rollover

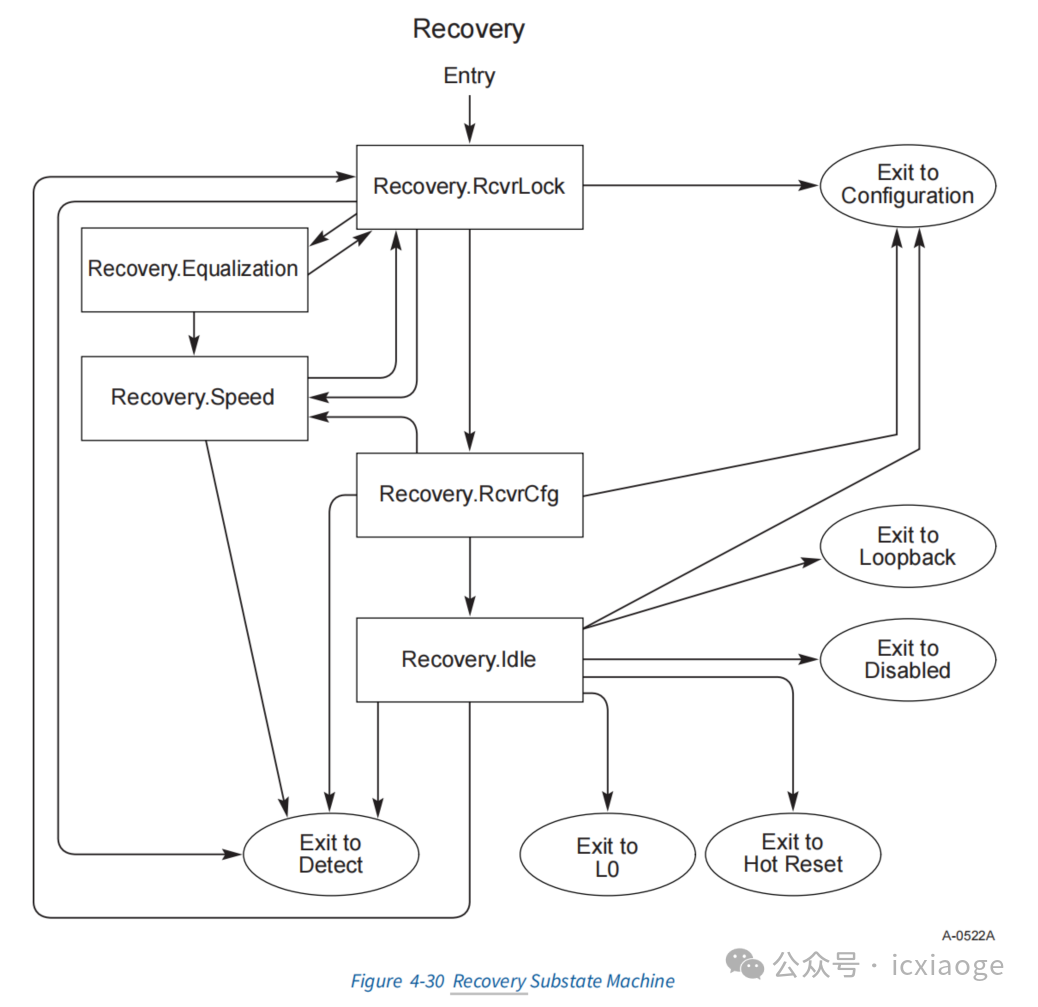

总结:发送一个TLP,对端回复了nak,这个时候buffer中的TLP会重传一次,acknak机制中有一个2bit的REPLAY_NUM,初始为00b,一般希望是重传后能够被对方接收并回复ack,如果重传4次还没收到ack,那么就链路层进入recovery重新训练一下到L0。重传一次REPLAY_NUM+1,当REPLAY_NUM从11b rolls over 到00b时说明传了第四次了,这个时候就会触发REPLAY_NUM Rollover置位

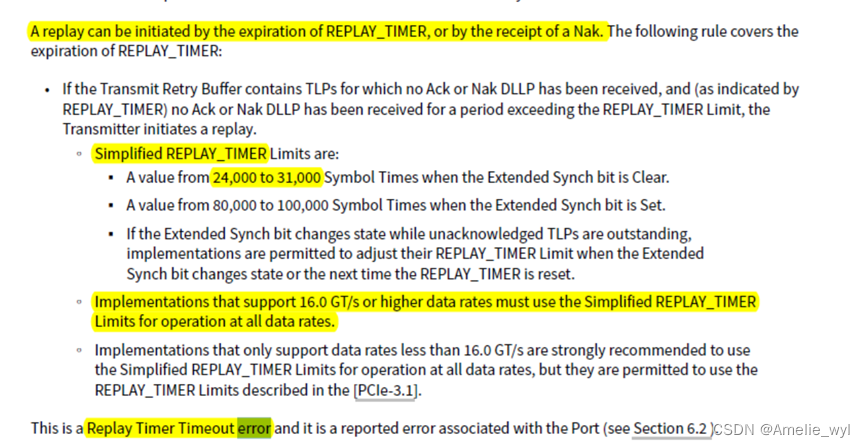

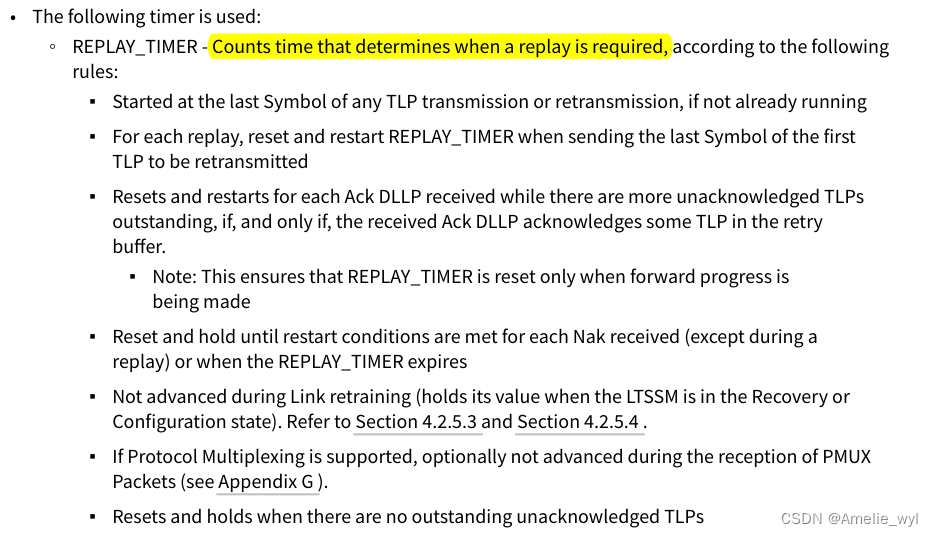

1.1.5 Replay Timer Timeout

总结:REPLAY_TIMER是传输的时候开始计时,收到ack/nak的时候reset,超时是因为对方没有回应,或者回应晚了(总之就是回应超时了)

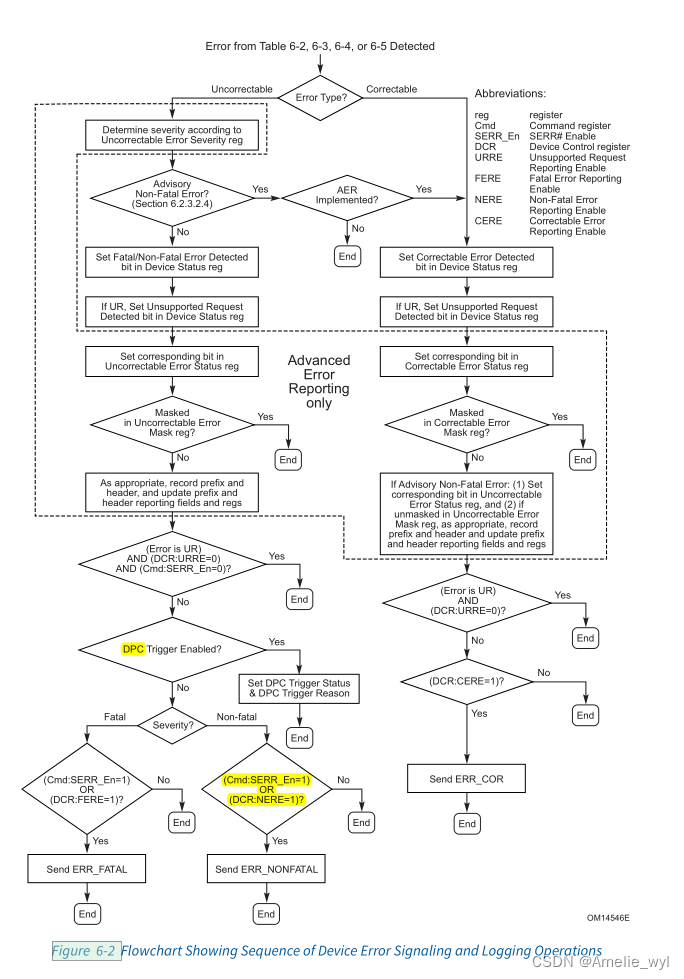

1.1.6 Correctable-Advisory Non-Fatal Error

这个不具体介绍了,因为涉及到uncorrectable error,简单来讲,就是uncor error可以设置为fatal 或者non-fatal,某几个uncor error发生这种错误时候不想引起host 宕机,默认初始设置为non-fatal error,这时候发生错误引起Advisory Non-fatal error置位;错误置位流程看spec fig 6-2(v、5.0r1.0)

具体由哪些case,可以具体看spec 6.2.3.2.4 Advisory Non-Fatal Error Cases

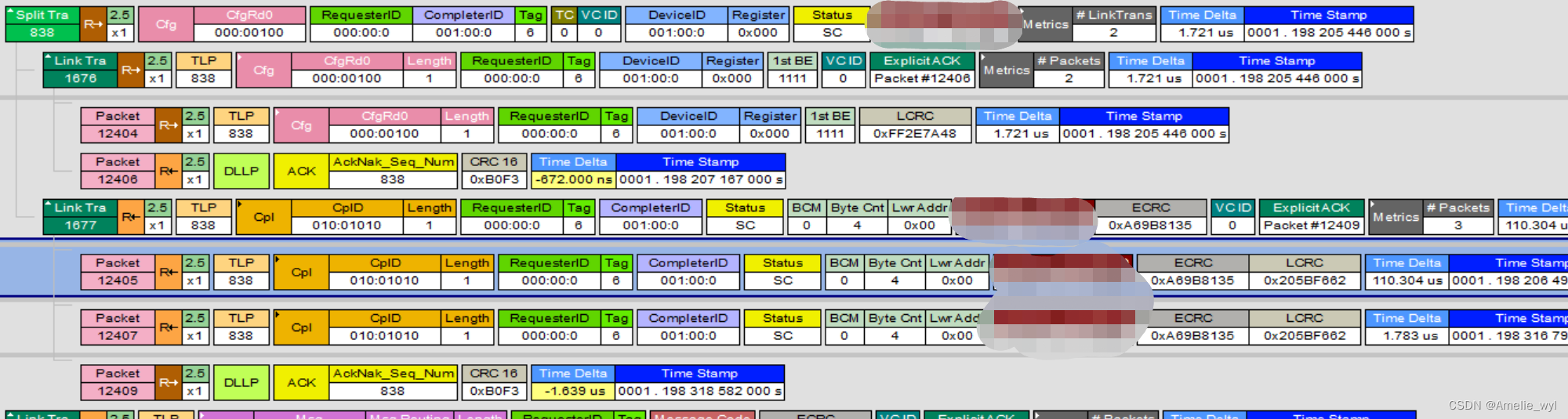

1.2、trace分析

分析一个简单的bad TLP ,根据流程图,需要检查的是框图触发error后需要set的寄存器,需要测试的是条件里面能够RW的寄存器;

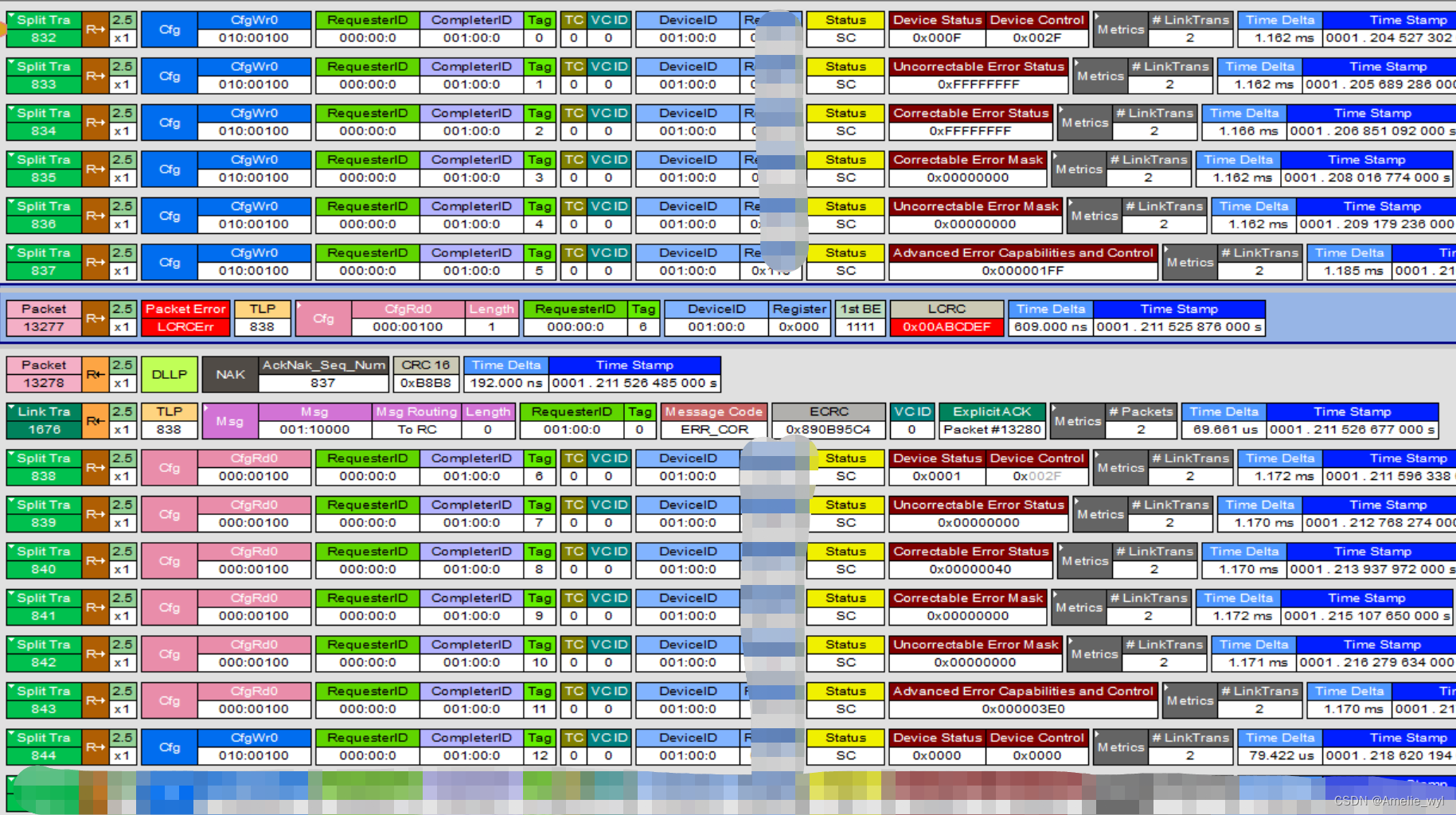

如上图所示,发生Bad TLP错误后(LCRC出错),检测到错误的设备会向rc 发送message(看spec Figure 6-3),后续device status 中相关bit会置位,检查AER status也会置位;对于uncorrectable error,也要检查一下header log(后续再学)

撒花,

这篇关于PCIe AER(一)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!