本文主要是介绍湖南大学-电路与电子学-2021期末A卷★(不含解析),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

【写在前面】

电路与电子学好像是从2020级开设的课程,故实际上目前只有2020与2021两个年级考过期末考试。

本份卷子的参考性很高,这是2020级的期末考卷。题目都是很典型的,每一道题都值得仔细研究透。

特别注意:看得懂答案跟写得出来不是一回事,复习时写出来和考场上写出来又不是一回事。

由于当时自己做的答案未及时整理,已经散佚不可考。故不附答案,读者可以自己试做,整理答案。

这张卷子有一道模拟电路的题目,根据老师划定考不考来决定做不做。

一、(5 分)

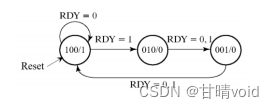

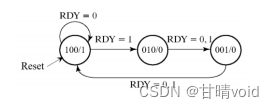

用 Verilog 三进程法设计一个同步时序电 路,该电路有两个输入 RDY 和 Reset ,一个输出 Z , 其状态图如右图所示。

二、(10 分)

用两个 4 位行波加法器和适当的逻辑门设

计一个 4 位十进制加法器。加数、被加数以及结果均用 8421 码表示。要求画出电路图,

并给出必要的说明。行波加法器可以用符号表示。(提示:可先考虑把加数和被加数直接

相加,然后再对结果进行修正)

三、(共 15 分)

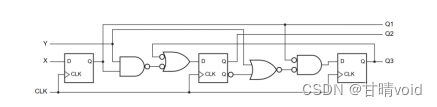

重新设计下图所示电路以减少成本。

1 、做出这个电路的状态表,并将每个状态编码用一个字母来表示。在原设计中状态

Y1Y2Y3 为 100 和 111 未被使用。( 5 分)

2 )检查并合并等价状态。( 5 分)

3 )对状态进行赋值(使得输出是某一个状态变量),并写出触发器激励方程和电路

输出方程。( 5 分)

四、(共 20 分)

两位输入 XY 按照“ 00, 01, 11, 10” 的顺序输入,其中任意一个组合可以重复任意

次,而且“ 10” 是最后出现的输入组合。设计一个 Moore 型序列检测器,当出现这样的输

入序列时,电路的输出 Z 为 1 。要求:

1 、做出电路的 状态机图 ;( 5 分)

2 、做出用 表达式表示 的状态表;( 9 分)

3 、使用 D 触发器,并采用单热点编码法进行状态分配(可以不考虑未用状态),写

出各个触发器的激励方程和电路的输出方程;( 6 分)

五、(共15 分)

针对下图所示的反相放大电路一般化模型,计算电压增益 v o / v s ,并求出当 R i → ∞、

R o → 0 、 A → ∞时,电压增益的简化形式。这个简化的表达式与理想反相放大电路的电压增

益表达式有何不同?

六、(共 10 分)

分析下图所示电路的同步问题。设电路当前状态 Q1Q2Q3 为 111 , XY 的当前值

为 10 。

1 、如果 XY 在远离时钟有效跳变时从 10 变为 01 ,电路的下一状态是什么?( 3 分)

2 、若 X 在远离时钟有效跳变时从 1 变为 0 , Y 在离时钟有效跳变很近时从 0 变为 1 ,

电路的下一状态可能出现什么异常?( 5 分)

3 、如何才能比较好地解决异常问题?( 2 分)

七、(共 15 分)

用迭代法设计一个比较两个 4 位无符号数 A 和 B 的组合逻辑电路。如果 A≥B ,

则输出 Z=1 ,否则 Z=0 。对两个 1 位数进行比较的单元电路由下图所示的一个 FPGA 逻辑

块实现。要求:

1 、列出单元电路的真值表;( 5 分)

2 、确定单元电路对应 FPGA 逻辑块各个控制位的值。 ( 6 分)

3 、画出整个电路的逻辑图,其中 FPGA 逻辑块仅用符号表示即可。( 4 分)

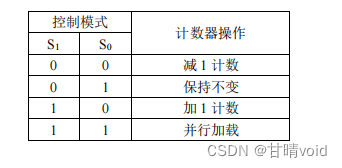

八、(共10 分)

用逻辑门、多路复用器和 D 触发器设计一个 4 位计数器,功能要求如下表所示。

要求画出计数器中某一级(某一位)的逻辑图。

这篇关于湖南大学-电路与电子学-2021期末A卷★(不含解析)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!