本文主要是介绍[⑦ADRV902x]: JESD204学习笔记,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

前言

JESD204B/C基于SERDES(SERialization/DESerialization)技术,也就是串化和解串,在发送端将多位并行的数据转换为1 bit的串行数据,在接收端将串行数据恢复成原始的并行数据。

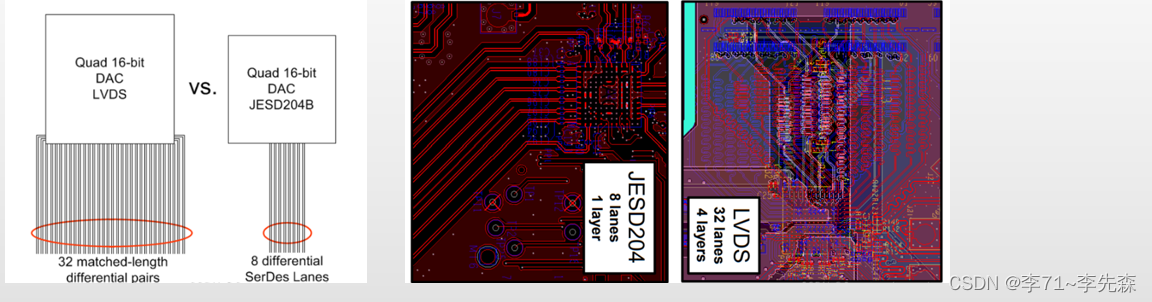

在JESD204接口出现以前,数模转换器的数字接口绝大多数是差分LVDS的接口,这就造成了布板的困难,当PCB的密度很大的时候就需要增加板层从而造成印制板的成本上升。 而JESD204接口是串行接口,能有效减少数据输出的差分对,能最大限度的简化Layout。 因此JESD204是高密度板不可或缺的接口。但因其需要进行严格的同步和以及时延的测量, 接口的逻辑会比LVDS接口复杂很多。

ADRV902x系列射频芯片支持JESD204B/C,用来在transceiver和baseband processor(FPGA)之间传输ADC和DAC的samples数据,最高serial lane rate可达24.33 Gbps。

ADRV902x系列射频芯片支持JESD204B/C,用来在transceiver和baseband processor(FPGA)之间传输ADC和DAC的samples数据,最高serial lane rate可达24.33 Gbps。

逻辑分层

JESD204是一种高速的串行接口协议,它规定了收发双方的同步机制,告警机制及其告警后处理机制。 任何 一种复杂的接口协议都将遵从逻辑架构分层来进行描述。 JESD204也是如此,遵从如下的逻辑分层:

-

Application Layer:通过应用层可以实现特殊用户配置,接收端和发送端必须以相同方式进行配置,以便正确传输和解读数据

-

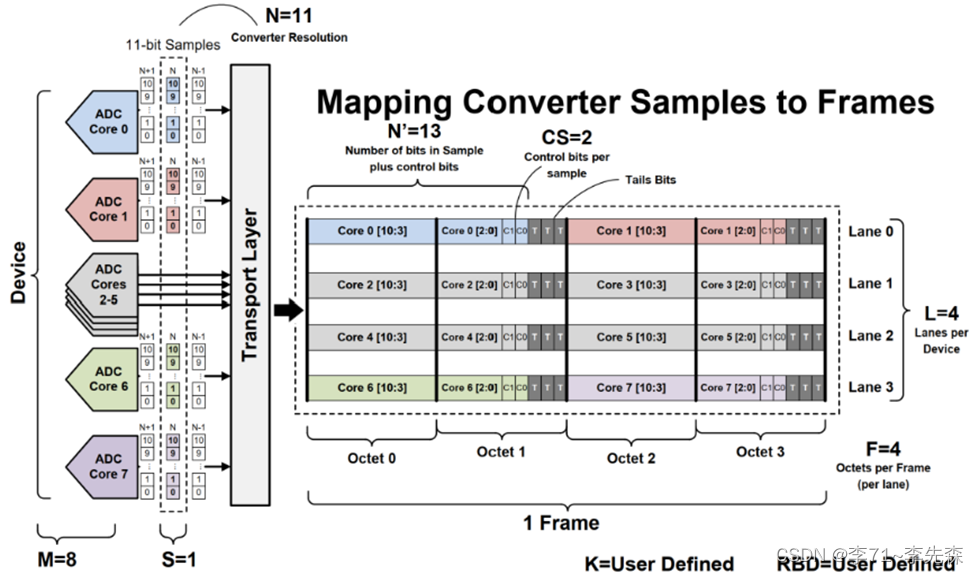

Transport Layer:传输层的功能是将ADC/DAC采集到的samples数据映射到非扰码的8-bit数据

映射模式:

1 . a single converter to a single-lane link

2 . multiple converters in the same device to a single-lane link

3 . a single converter to a multi-lane link

4 . multiple converters in the same device to a multi-lane link

上述的四种模式是两个对象(converter,link)的几种组合,一个是数据转换器(converter)的个数,另外一个是对应的link的个数。 数据转换器就是对应的I/Q的数据组,例如无线系统中都是采用complex数据,有16-bit 的I和16-bit的Q,那么对应的转换器个数就是2,就类似I数据需要一个转换器来完成,Q数据需要另一个转换器来完成(注意这里的转换器的个数和我们通常所说的物理的ADC/DAC个数有区别,可以抽象为一个吞吐数据器件)。 通常情况下转换器的个数都是多个(多通道),这些转换器的数据可以一起来建链称之为single-lane link,也可以分组建链称之为multi-lane link。

例:一个ADC可以映射到一个单通道链路,或者映射到一个多通道链路,采样速率决定是否使用多个通道,以便符合对通道速率的限制。

-

Scrambling Layer:按照实际的运用可以选择对8-bit数据数据加扰或者不加扰,加扰的主要目的是去除数据相关性。

-

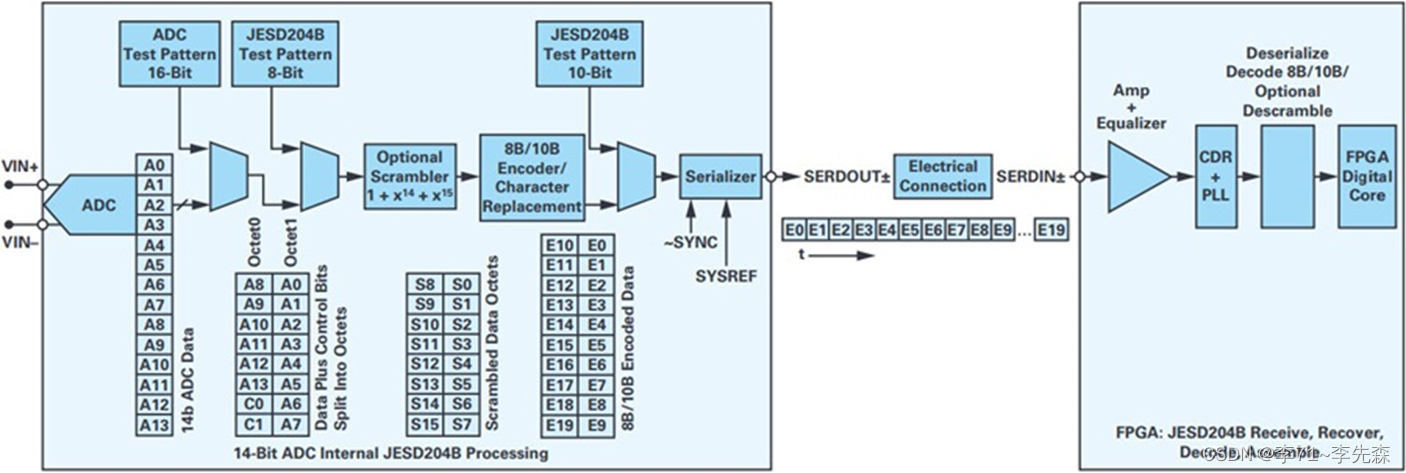

Data Link Layer:链接层在再整个JESD204中占有及其重要核心的地位。 它包含了 8-bit/10-bit JESD204B的编码过程 (64-bit/66-bit JESD204C), Tx和 Rx link的建立,同步和维护。

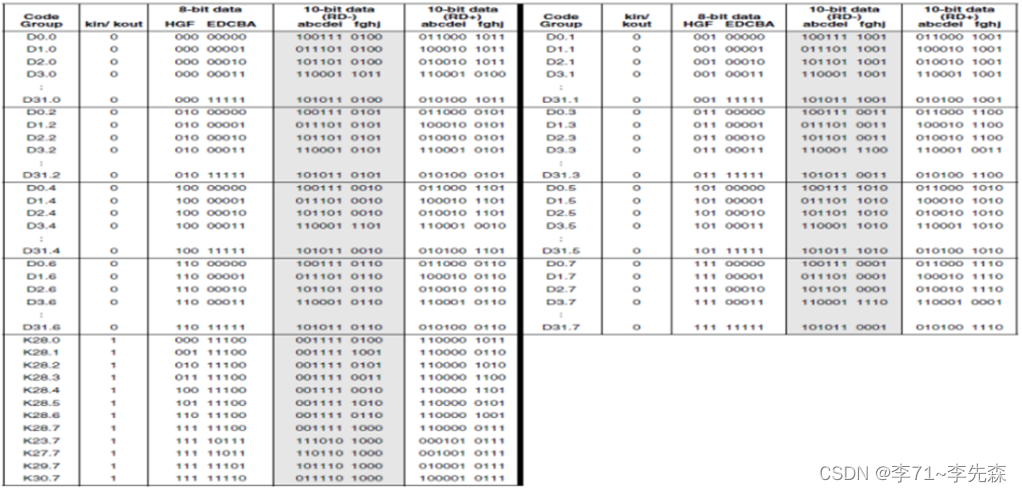

8B/10B编码的状态机和码表如下图所示。 编码的目的就是去除数据中的DC-unbalance(CML电平中会增加直流偏置,利用8B/10B编码,可以实现平均而言包含等量1和0的平衡序列),8-bit变为10-bit。 例如我们通常所说的 K28.5, 8-bit的时候为10111100,编码后变成 0011111010。

-

Physical Layer:物理层包含了完成高速并/串转换的SDRDES模块, 时钟及时钟数据恢复模块(CDR) 。物理层也规定了接口的物理电器特性。

下图为ADRV902x中JESD204发射/接收逻辑分层框图:

下图显示了从发射器件(ADC)到接收器件(FPGA)的简化JESD204B链路,数据从一个ADC经由一个通道传输:

下图显示了从发射器件(ADC)到接收器件(FPGA)的简化JESD204B链路,数据从一个ADC经由一个通道传输:

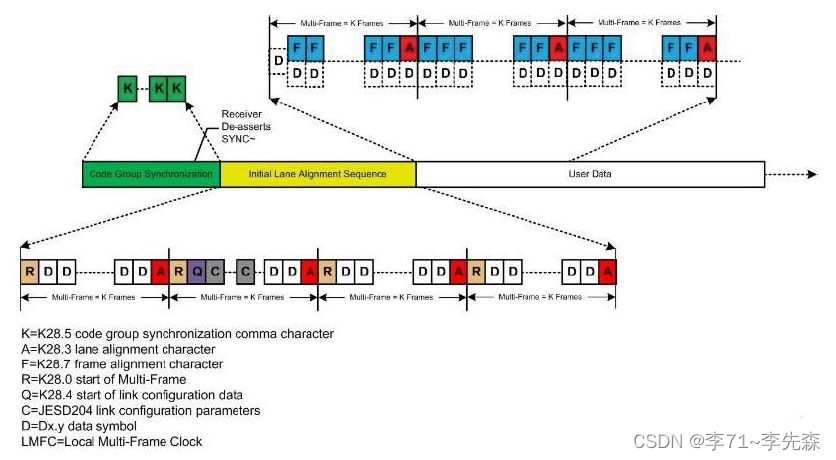

JESD204链路建立

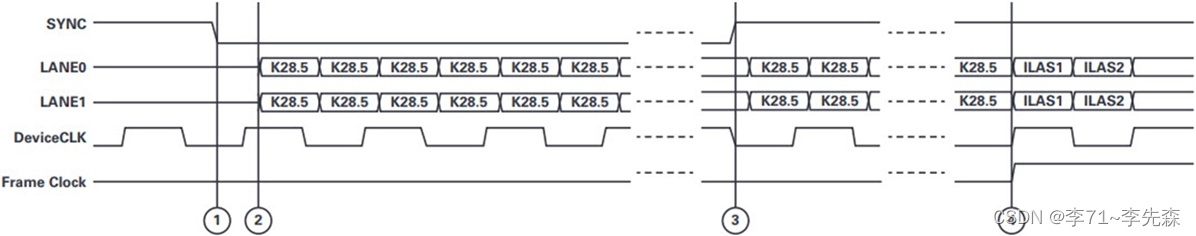

JESD204链路建立包括三个阶段(CGS,ILAS和用户数据),下面简单介绍下:

- 代码组同步(Code Group Synchronization):

1 . 接收器通过拉低SYNC~引脚,发出一个同步请求。

2 . 发送器发送未加扰的K28.5符号(标准中称为K字符)。

3 . 当接收器收到至少4个无错误的连续K28.5符号时同步,然后将SYNC~引脚拉高,CGS阶段结束,ILAS阶段开始,否则同步将失败,链路留在CGS阶段。

- 初始通道对齐序列(Initial Lane Alignment Sequence):ILAS的主要作用是对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。ILAS由4个或更多多帧组成,无论启用加扰链路参数与否,ILAS始终是无加扰传输。

Multi-frame 1:以R字符K28.0开始,以A字符K28.3结束。

Multi-frame 2:以R字符K28.0开始,后接Q字符K28.4,然后是14个链路的配置参数,最后以A字符K28.3结束。

Multi-frame 3:与Multi-frame 1相同。

Multi-frame 4:与Multi-frame 1相同。 - 用户数据:CGS和ILAS阶段完成后,发送器开始送出ADC数据。在这一阶段,用户数据根据链路参数的定义,以流形式从发送器传输到接收器。

Transceiver接收端

下面是ADRV902x transceiver接收端,SERDES framer(成帧器)的框图:

3个framer,最多4 lanes。

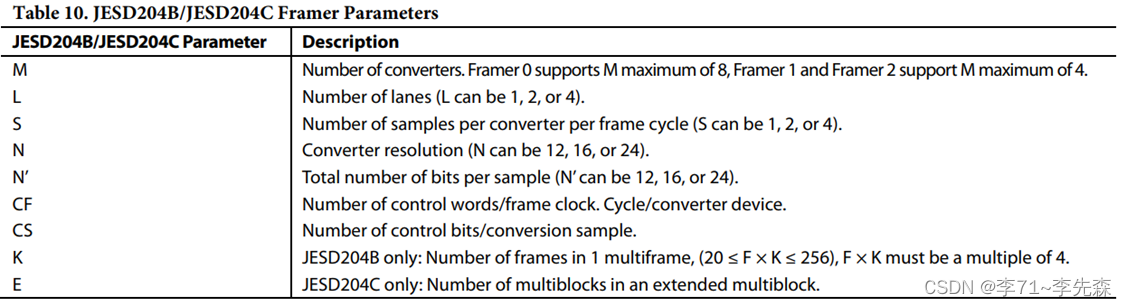

下面是JESD204的参数介绍,Desscription中参数的大小是针对ADRV902x的,意义具有通用性:

F:number of octets per frame

在ADRV902x中,为了让JESD204配置有效,lane rate(seial bit rate for one lane)必须在 3684.4 Mbps 到 16220.16 Mbps之间。lane rate的计算公式如下:

每个framer可以接收本地converter的samples数据然后将它们映射到high speed serial lanes. 映射关系取决于JESD204的配置,特别是lane的数量,converter的数量和samples per converter。

下面是AD给出的M = 2,L = 1,S =1的一个例子:

其中关于NG跟word的概念可以参考如下:

NGs (nibble groups):contain N’ bits

words:words padded with tail bits

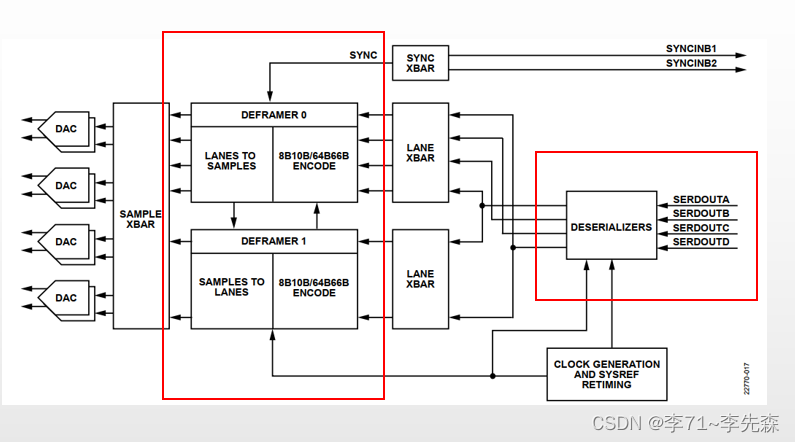

Transceiver发射端

下面是ADRV902x transceiver发射端,SERDES deframer(解帧器)的框图:

2个deframer,最多4 lanes。

deframer接收来自deserializer的8B10B/64B66B encoded data,然后解码成converter的samples数据。下面是AD给出的M = 4,L = 2,S =1的一个例子:

ADRV902x JESD配置样例

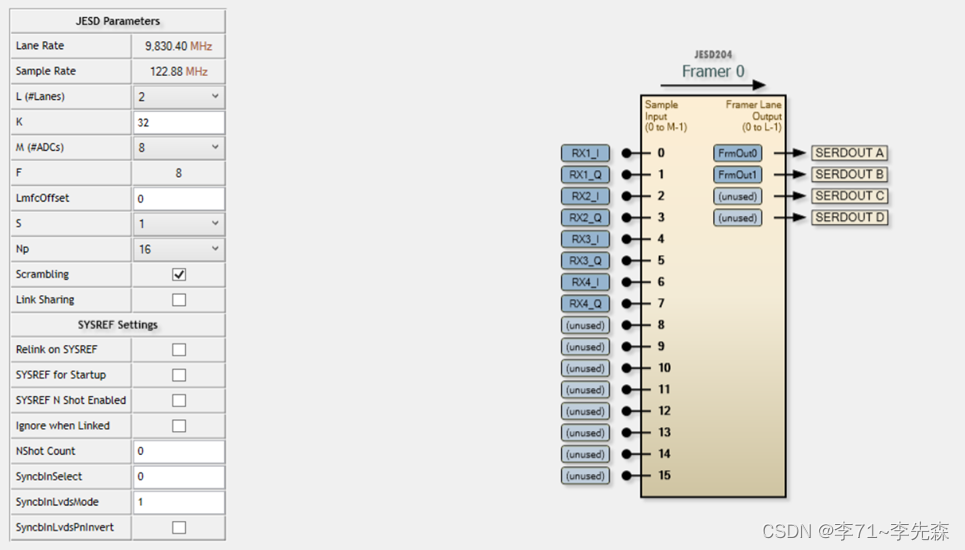

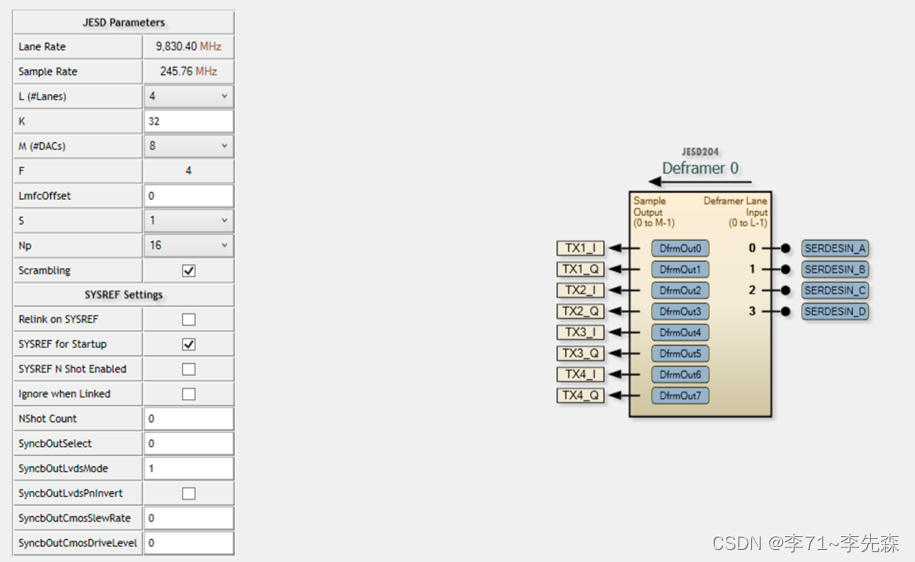

下面是AD给出的JESD204B的配置样例,UseCase 13 for non-link sharing (non-link sharing的意思就是ORx和Rx的samples数据不在一个framer里)。其中使用了2个framer(framer0,framer1)和一个deframer(deframer0)。

这篇关于[⑦ADRV902x]: JESD204学习笔记的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!