本文主要是介绍一种快速设计射频功放IC流程分享,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

No.1设计目标

在功率放大器PA中,输出级以及输出匹配决定了该功放的线性度、效率等关键性能指标,通常被优先考虑。在这个项目中输出级功放关键性能指标如下:

带宽:12-13 GHz

OP1dB>13dBm

输出级 Power gain>5dB

DE_P1dB>45%

S11<-12dB

Kf>1,B1f>0

Zin/Zout: 50/50

No.2 电路架构

其中PA的线性度、效率主要由有源区尺寸、栅端偏置以及负载阻抗决定。在输出级的设计中,需要重点关注的也就是功率输出能力以及效率,而如果对增益有额外的需求,可通过级联的方式提高增益。同时对PA模块来说,Kf,B1f稳定性系数达到要求相当重要,否则PA会出现震荡的风险。

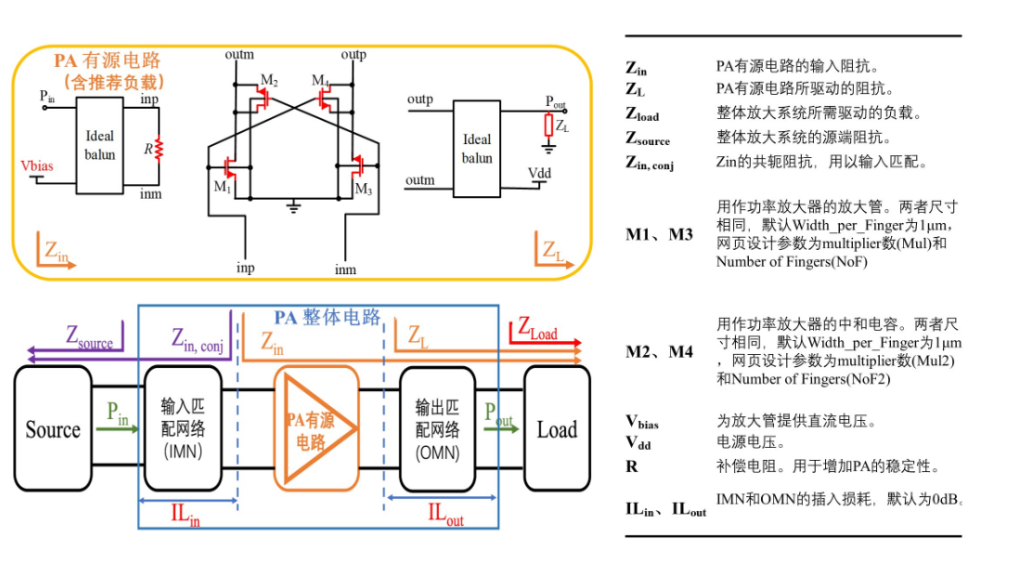

我们在这个设计中用了线上生成射频电路的工具来完成设计。下图是该线上工具提供的原理图,也是本次PA模块设计的参考原理图,其中有源区采用的是基于中和电容的共源放大架构,无源匹配网络采用基于变压器的匹配电路。

整个射频PA由有源电路,输入匹配和输出匹配 三个部分组成。

No.2 设计流程

第一步,有源模块设计

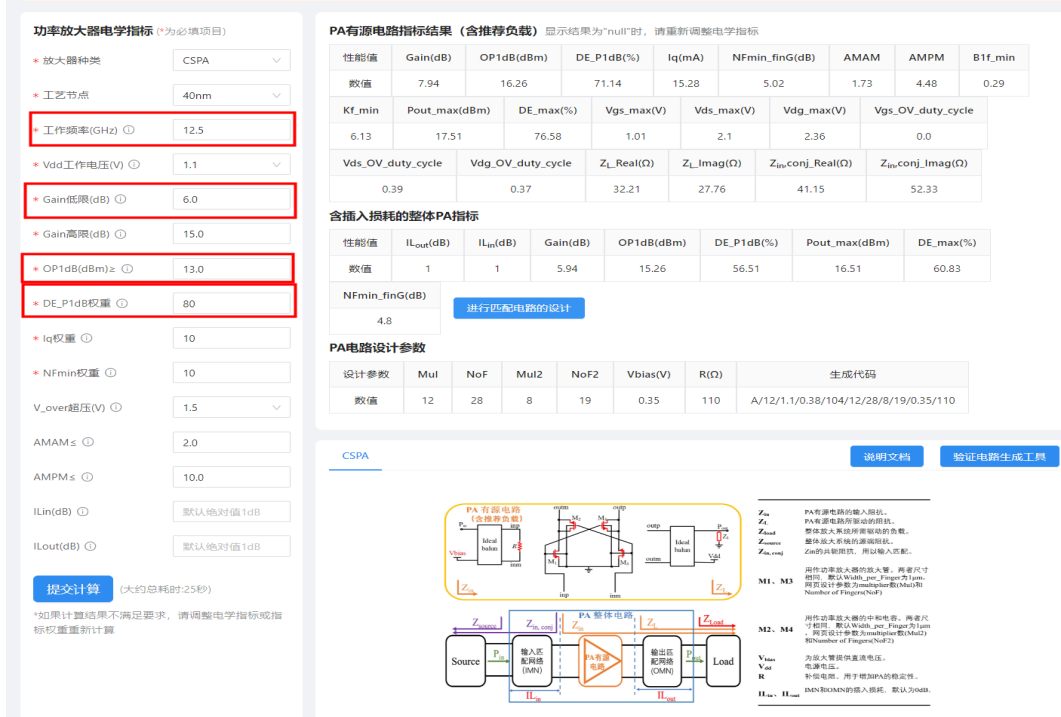

有源部分设计用了RFIC-GPT的“功率放大器有源电路生成工具”网页模块。在网页左侧填入我们需要的指标,工作频点选择中间频点。

设计关键指标中的线性度(OP1dB)和效率(DE_P1dB)主要由输出级有源区+无源区设计决定。此处设置有源模块OP1dB>13dBm,同时DE_P1dB的权重设置为80,占较大权重,增益下限设置为6dB。

点击“计算”后,不到 1分钟就完成了运行,设计计算结果显示其设计的PA的OP1dB为15.26dBm,这为加入实际的有损匹配网络留出了设计裕量。

本次设计限制的AM-AM为2dB,在功率上升的过程中出现了较大的gain boost,如若设计指标对PA的AM-AM有限制,也可以在左侧加入相应的限制条件。

在给出性能表现后,网页结果也提供了相应的MOS管、中和电容、输入电阻相关设计参数以及目标匹配阻抗,非常方便。

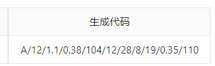

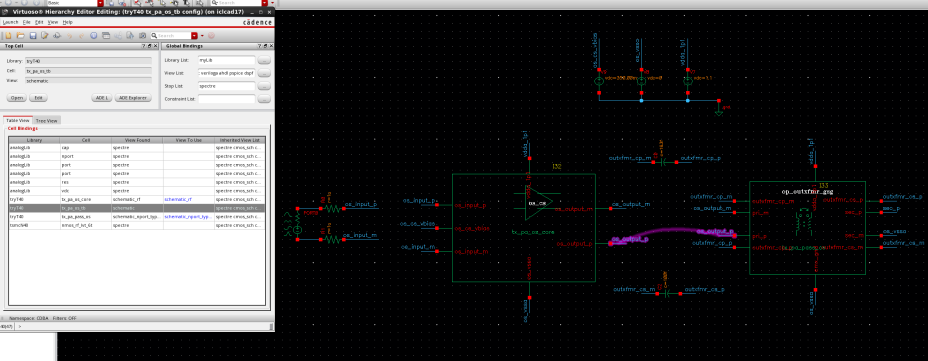

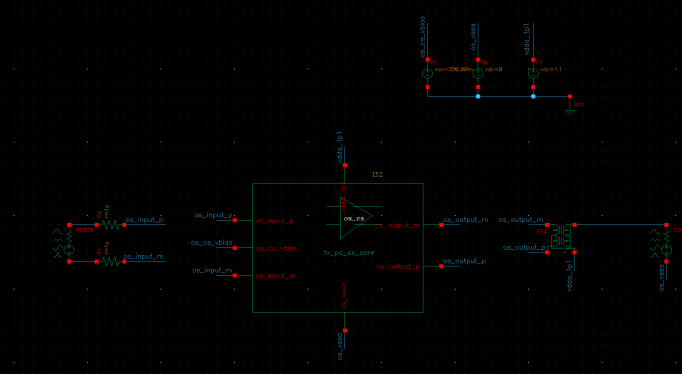

下一步,我们下载并安装了该网页上的“验证电路生成工具” Prophet_tools,这个工具一次安装就可以集成在Cadence virtuoso中。然后根据网页显示的生成代码填入这个设计小程序中(图4),就可以自动生成相应的电路原理图和对应的测试TestBench(图5).

具体小程序安装参考网页安装说明,对应生成的设计TB如下:

可生成对应的测试原理图与相应的spectre,该原理图中包括了输入输出port,输入电阻,输入差分对管,中和电容,以及各类偏置。并使用portAdapter仿真史密斯圆图上负载阻抗,从而得到不同负载情况下PA的各类性能参数。

第二步,输出匹配网络设计

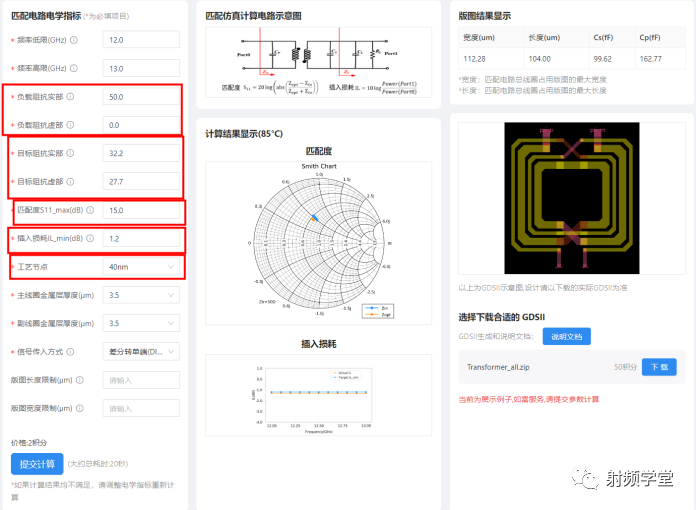

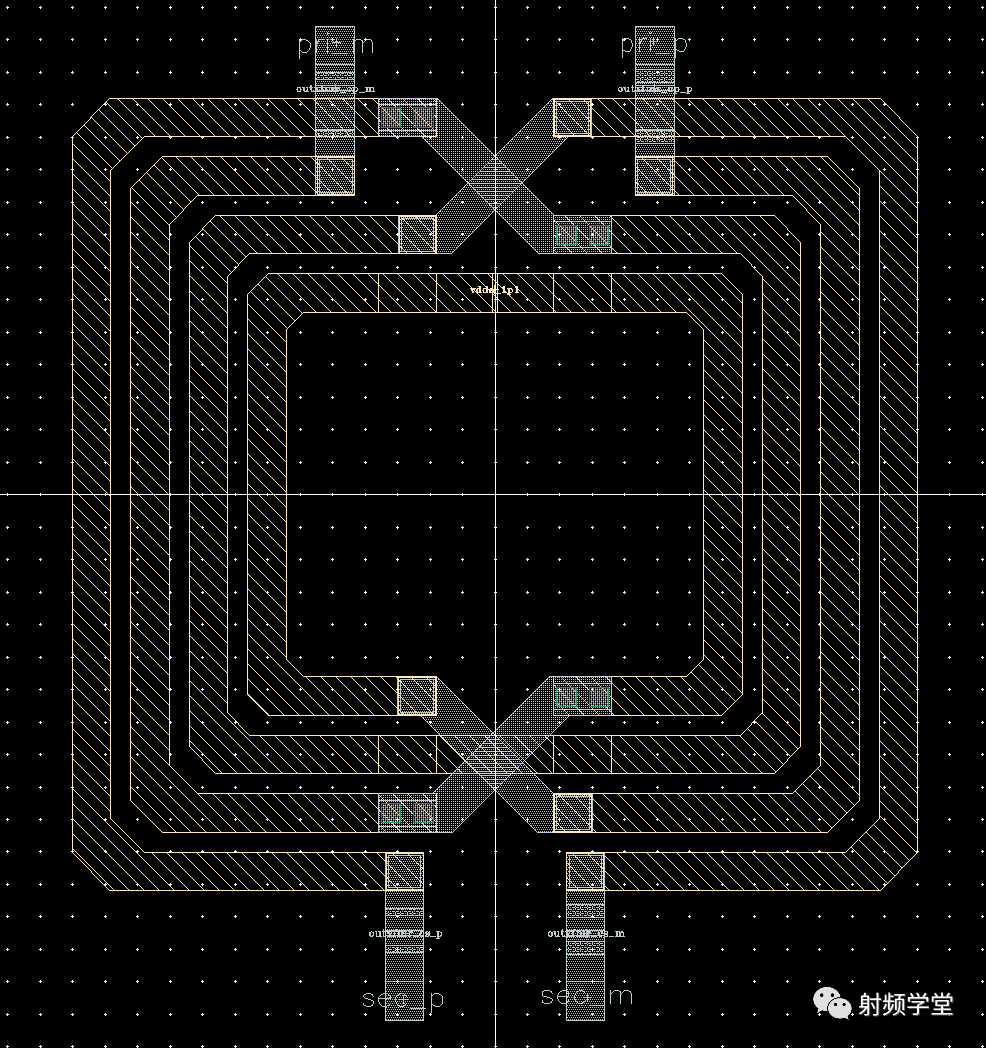

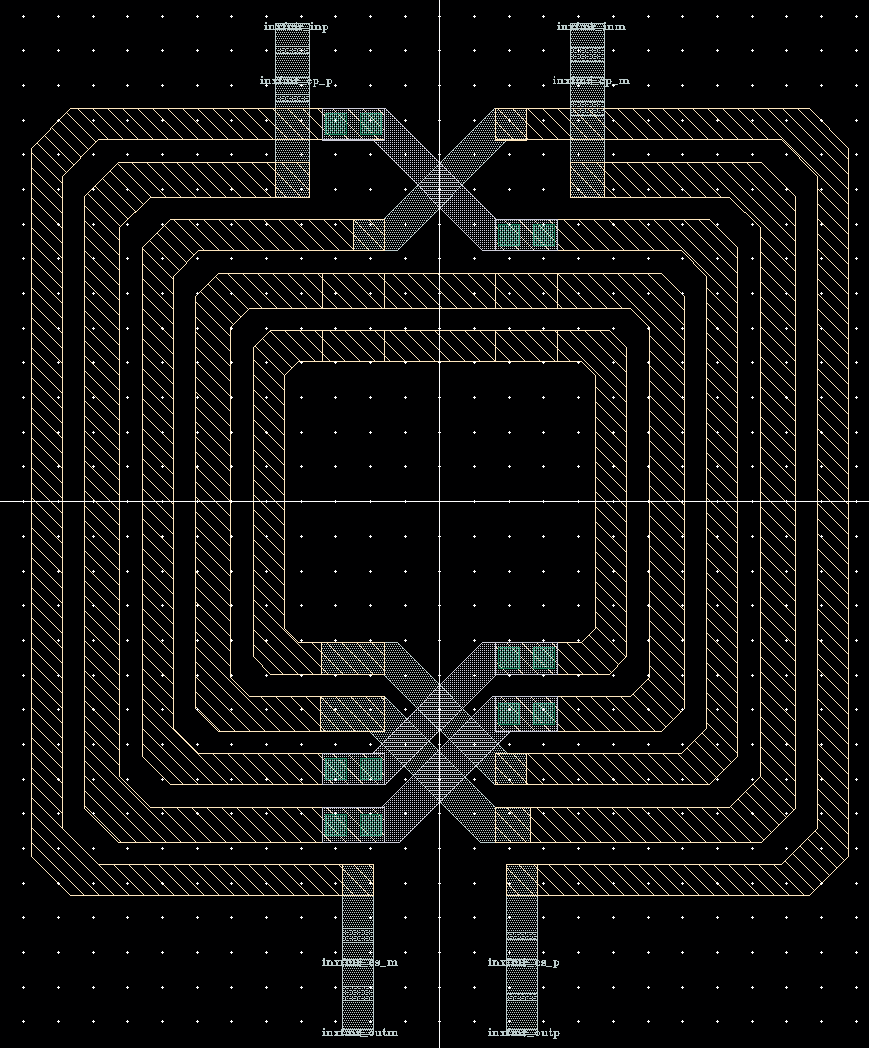

接下来要设计输出匹配网络,我只用将上一步有源模块设计中的最优阻抗填入同一网页无源设计模块“匹配电路”中,就可以直接生成无源版图及性能效果。整个过程仅用了1-2分钟。

在将生成的文件导入设计环境后,便可以自动生成有源网络的版图并基于该版图完成无源网路的电磁仿真。

将有源区与输出匹配网络分别创建模块并建立仿真设计的testbench,验证输出级的关键参数

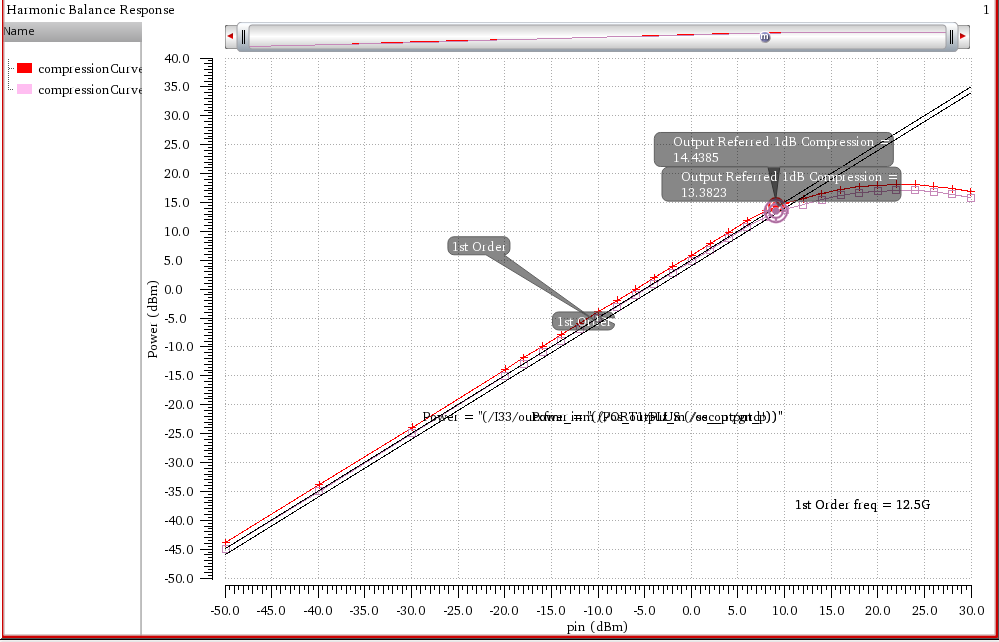

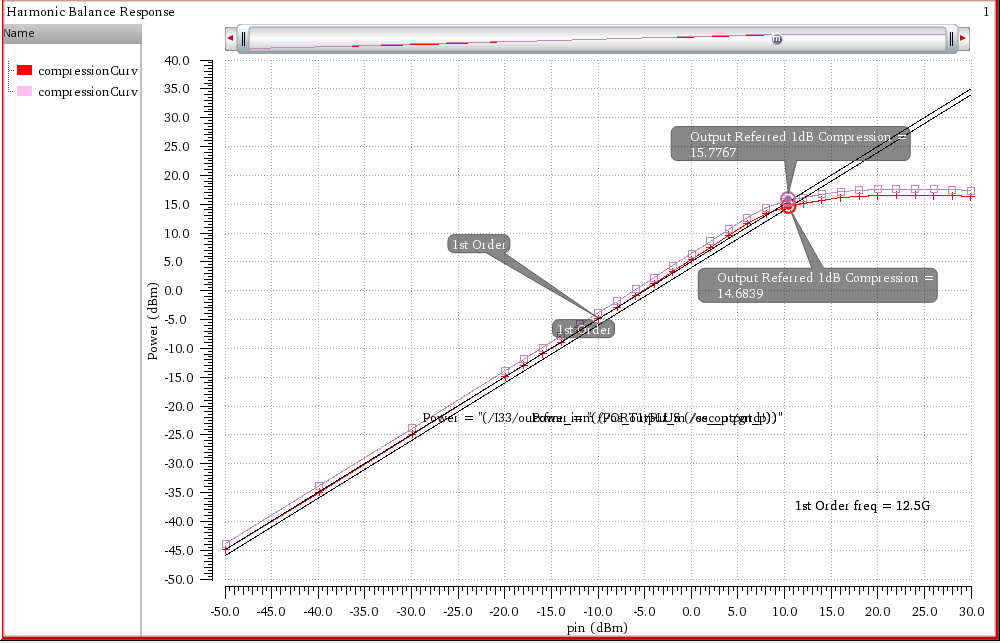

OP1dB:

在加入实际的电磁仿真结果后,OP1dB相比于本身设计的有源区OP1dB下降2dB。在与同学交流后,我们猜想应该是二次谐波导致线性度的下降。

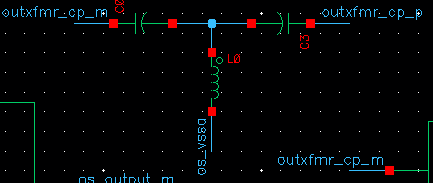

我们搭建了一个较为理想的二次谐波消除网络进行验证,电路如下:

加入谐波消除网络后,OP1dB为15.8dBm,与Prophet软件预测的16.2dBm接近,因此验证了上述OP1dB与Prophet工具预测出现不匹配是由二次谐波带来的。

Power Gain:

和Prophet软件预测结果相比,增益相差较小,仅为0.3dB。

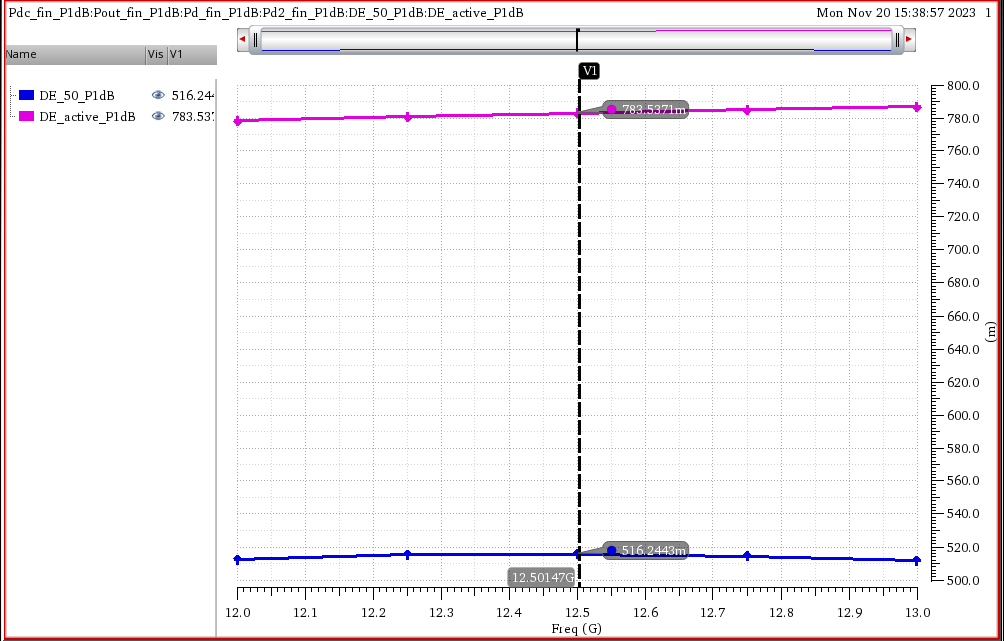

DE_OP1dB:

有源区效率大于50%,无源区效率与软件预测结果一致。

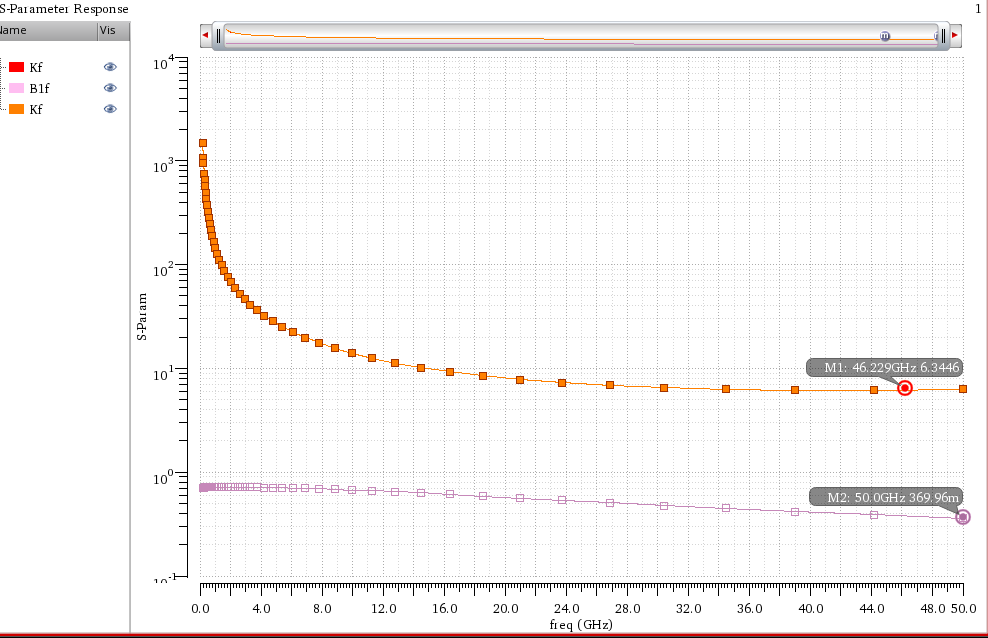

Kf&&B1f:搭建TB如下:

结果显示有源区直到50GHz都是无条件稳定。

第三步,输入匹配网络设计

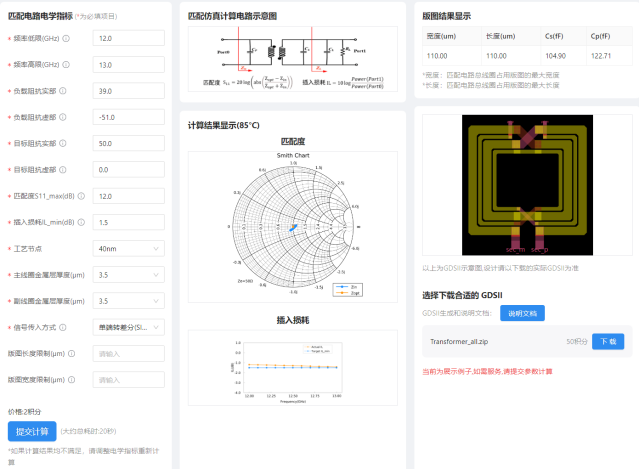

最后我们设计输入匹配网络。与输出匹配网络类似,再次借助RFIC-GPT无源设计模块“匹配电路”,我很快完成了输入匹配网络设计。此处PA输入阻抗为39 – 51j,S11<-12dB,损耗限制小于1.5dB,匹配网络网页设计如下

导出GDS后,可以直接生成无源版图并进行电磁仿真提参。

仿真S11<-15.5dB,甚至好于预期,仿真结果如下所示:

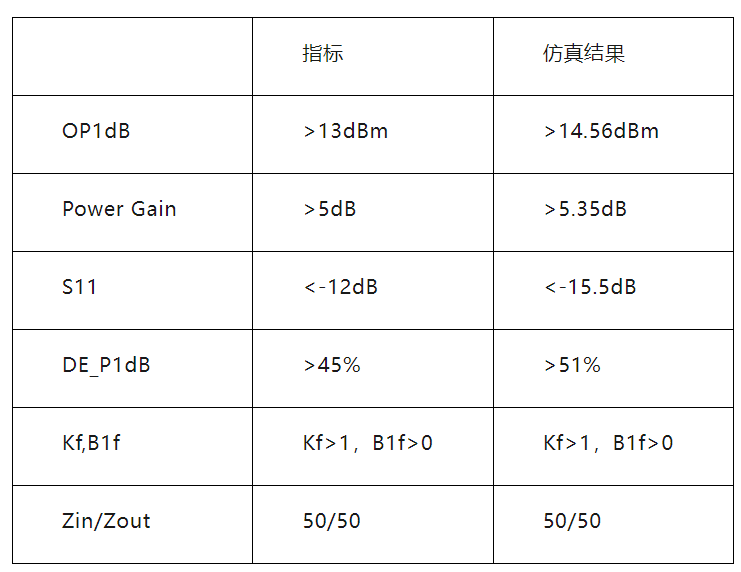

No.3 设计结果与总结

这次设计的射频功放管的性能总结如下:

本设计中无源网络的版图,有源网络的前仿设计都由RFIC-GPT计算完成设计自动生成,大大缩减了设计时间,目前有源部分给的是原理图,如果也能一键出版图,那就更方便了,期待有源区版图自动生成后仿结果测评。

【以上信息由艾博检测整理发布,如有出入请及时指正,如有引用请注明出处,欢迎一起讨论,我们一直在关注其发展!专注:CCC/SRRC/CTA/运营商入库】

这篇关于一种快速设计射频功放IC流程分享的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!