本文主要是介绍arm gic 中断控制器工作原理概述,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

linux pinctrl 里面有个gpio抽象的中断控制器与系统的gic中断控制器级联cascade

阅读arm generic interrupter controller architecture specification,总结下

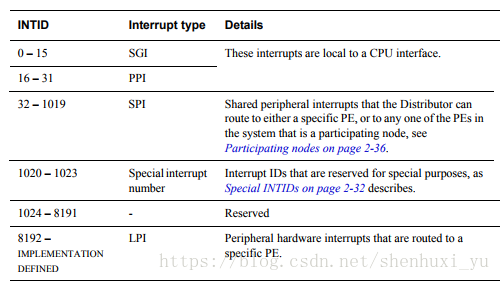

支持的中断类型

平常工作接触到的是ppi,sgi和spi,ppi和sgi是对某一个核的,spi是对所有核的,sgi一般是用来核间通信

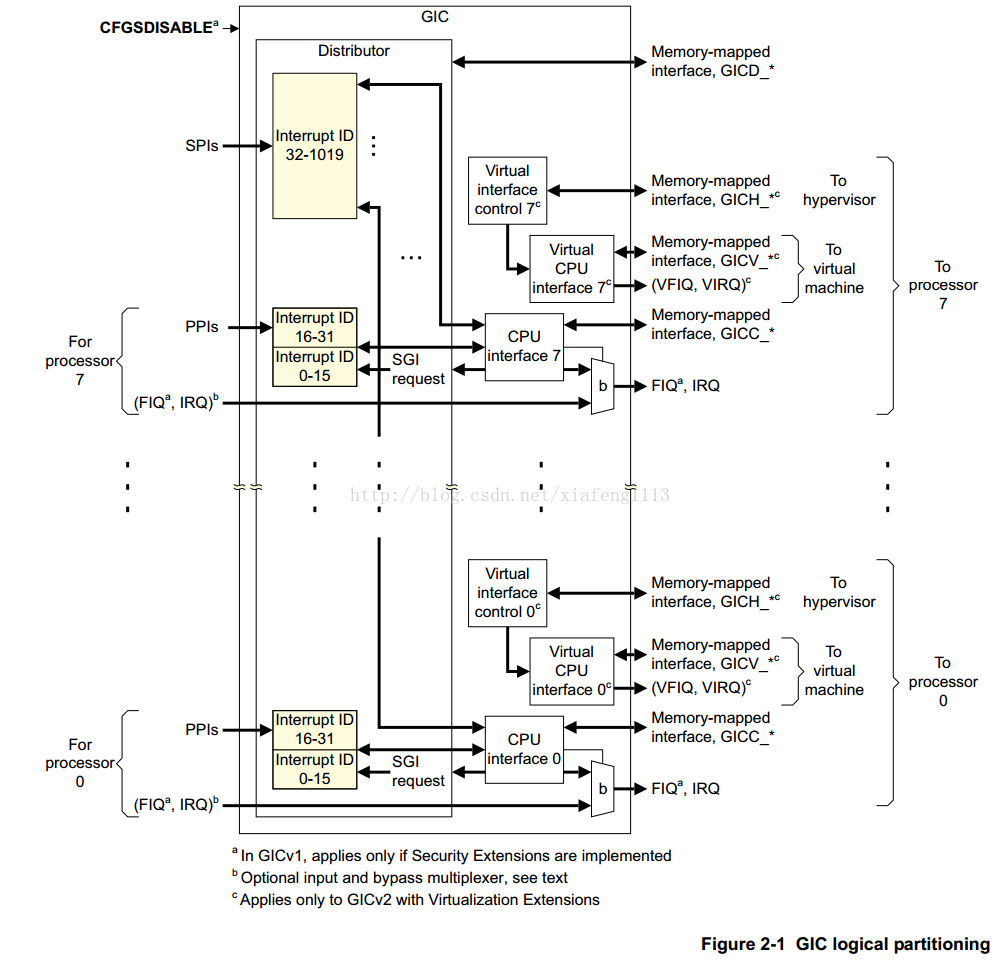

gic 的hw 分为简单两部分distributor和cpu interface(实际上还有int service 和 redistributor),下图以是gic工作原理的简化图,distributor是只有一个,cpu interface 每个核有一个,每个核可以通过一个private bus去访问gic的寄存器

distributor 的功能包括(针对不同类型中断可能支持的功能不同,如下只描述spi):

.中断的优先级控制(group0 group1)

.中断的security 配置(secure non-secure)

.中断的affinity配置(亲核性 )

.中断的level-edge sensitive

.对中断active或者pending(state machine)

cpu interface的功能包括:

.中断的ACK

.中断的priority drop

.中断在对应的security状态执行(secure non-secure)

.中断的deavtive

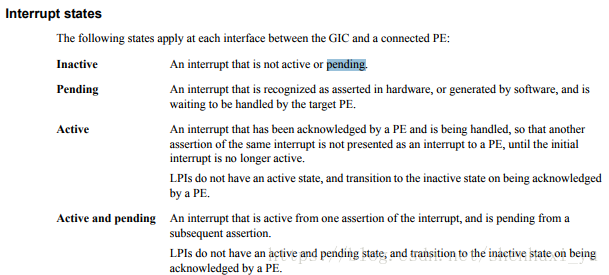

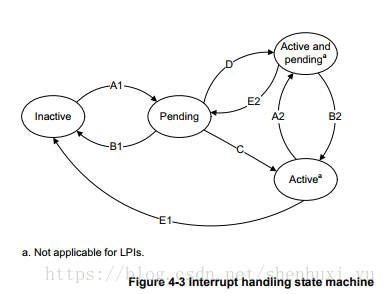

gic state machine

一般的中断处理流程: 中断的初始状态是inactive,device assert 中断后状态变为pending如果这个时候priority security 条件都满足的话cpu interface会ack to this interrupter,中断的状态变为active,系统读取中断号然后执行中断,如果之后该device没有再assert中断的话,中断的状态就变为了inactive

device assert 中断对于level-edge sensitive(配置在distributor)的中断是不一样的,这次想翻看gic文档的目的是想知道level sensitive的中断gic会不会有device已经关掉中断,gic还记录着该中断是pending的状态,答案是不会

这篇关于arm gic 中断控制器工作原理概述的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!