本文主要是介绍DDR颗粒辨识,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

V2.0版本更新内容如下

1.加入新颗粒

2.加入南亚、力晶颗粒判断方法

3.修正部分已知错误

4.对美光核心代号、海力士角标判断重新编辑

一:三星

三星官方命名文件如下:

(https://www.samsung.com/semiconductor/global.semi/file/resource/2018/06/DDR4_Product_guide_May.18.pdf)

实列:

第一行:“SEC 843”重要信息为843代表内存颗粒生产日期

第二行:“K4A4G08”重要信息为4G08代表内存颗粒容量和位宽——4Gb 8位颗粒(AG代表容量为16Gb)

第三行:“5WT BCTD”重要信息为T、TD,T代表颗粒版本我这个就是T-DIE。TD代表内存频率和时序,TD为 2666 C19、RC为2400 C17、PB为2133 C15、 第四行:角标 目前不知道有何定义

三星目前个人已知的颗粒(有些颗粒我都没有见到实物): A-DIE(16Gb、32Gb)、B-DIE(8Gb、16Gb)、C-DIE(8Gb)、D-DIE(4Gb、8Gb)、E-DIE(4Gb)、F-DIE(4Gb)、M-DIE(16Gb)、S-DIE(4Gb、8Gb)、T-DIE(4Gb) 三星也有ett颗粒,不过少见。

二:美光

美光颗粒打标官方定义:

(https://www.micron.com/-/media/client/global/documents/products/customer-service-note/csn11.pdf?la=en)

实列:

第一行:“7UE75”,7U代表颗粒生产事件7代表17年U代表42周(实际是U在26个英文字母是21位21*2=42),E代表颗粒版本即为E-DIE,75分别代表颗粒生产地和封装地,7为台湾5为中国大陆。第二行:“D9VPP”美光的FBGA码里面含有更多的颗粒信息需通过美光查询系统来解码,网址:https://www.micron.com/support/tools-and-utilities/fbga

美光颗粒命名规则:

(https://www.micron.com/-/media/client/global/documents/products/part-numbering-guide/numdram.pdf)

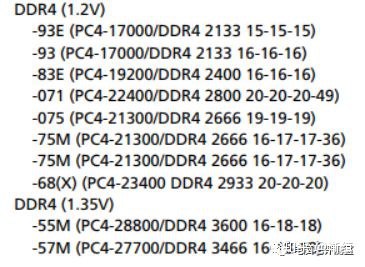

实例:MT40A1G8SA-075:E FBGA码:D9VPP 重要信息:40代表为DDR4,A为电压,1G8代表颗粒容量和位宽1G8是8Gb 8bit、512M16是8Gb 16bit,075代表频率和时序 075为2666 C19、083为2400 C17、093E为2133 C15,E颗粒版本E-DIE 美光编号和频率时序对应表:

美光颗粒及核心代号对应表:

美光的白片——spectek判断方法

一般的spectek(大S)颗粒上面也有些编码

实例:

编号:PS029-093 TP PS029

这个编码和美光FBGA码类似也可以在官网查询得知信息

网址:https://www.spectek.com/menus/mark_code.aspx

Spectek颗粒命名规则

(https://www.spectek.com/pdfs/SpecTek_pns_Components.pdf)

例子:SUU512M16Z11BD8LY

重要信息:512M16和美光一样代表颗粒容量和位宽,Z11B核心代号(见上面)可通过核心代号来确认颗粒版本

Spectek编号与频率时序表

TP代表颗粒质量等级

三:海力士

海力士官方命名文件:

实例:

第二行编号:“H5AN8G8NCJR”重要信息8G8代表颗粒容量8Gb和位宽8bit,C代表颗粒版本C-DIE

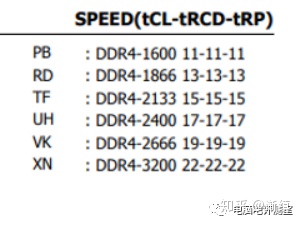

第三行编号:”VKC 829A”重要信息VK代表频率和时序。829代表生产日期。海力士编号和频率时序对应表:

第四行:角标 可能有某些关系

实际上我们常说的AFR、CJR、MFR不严谨实际上只有第一位代表颗粒版本,第二位代表的是封装类型,第三位也没啥有意义的东西。

海力士白片判断方法——角标判断法

很多的海力士白片颗粒的内存都打上内存品牌的logo无法看出是什么颗粒,只能依靠台风软件识别,不过很可惜台风软件识别是有问题的。在研究海力士颗粒的角标时我发现海力士颗粒角标可能有部分代表了颗粒版本。研究了几百颗海力士颗粒后我总结出了一些规律,不过还是强调下这只是个人总结官方并没有说明有这个方法!

海力士角标在颗粒最下面一行:

角标:DTBMJTS0W93

研究发现海力士角标前四位极有可能代表颗粒版本:

四:南亚

南亚官方命名文件:

(https://www.nanya.com/en/Support/50/Standard%20DRAM)

实例:

第一行:”NANYA 1804” 重要信息1804代表颗粒生产日期

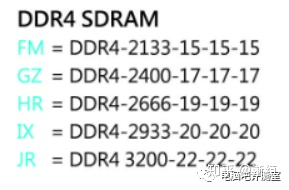

第二行:“NT5AD1024M8A3-GZ”重要信息1024M8代表8Gb 8Bit颗粒,A代表A-DIE,GZ代表2400 C17

美光编号和频率时序对应表:

南亚的白片:

南亚的白片特点在于颗粒右下角的标

实例:

目前未能研究出南亚白片角标完全的定义

五:力晶

力晶几乎没有原厂颗粒,所以常见的力晶颗粒是ett颗粒。

实例:

因为力晶官网也没有任何的颗粒命名规则。按照惯例,称为“C3G-T”

好看的文章记得多支持一下哦

http://weixin.qq.com/r/ijquttPECY52rZfV92_Y (二维码自动识别)

欢迎加入电脑吧个人二手交易群:829132489

关注B站@电脑吧评测室,@翼王或微博@渐缜JZ,@DDAA117

发布于 2020-03-07 11:05

这篇关于DDR颗粒辨识的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!