本文主要是介绍ARM V8 特殊寄存器之SPSR、ELR和SP,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

ELR (exception link register) 保存exception返回地址;

SPSR (saved processor state register) 执行exception前保存当前的processor state

PSTATE

在ARMv8架构中,使用PSTATE用来描述当前处理器的状态信息。PSTATE不是一个寄存器,它表示的是保存当前 process 状态信息的一组寄存器或者一些标志位信息的统称,它包含以下状态:

type ProcState is ( bits (1) N, // Negative condition flag bits (1) Z, // Zero condition flag bits (1) C, // Carry condition flag bits (1) V, // Overflow condition flag bits (1) D, // Debug mask bit [AArch64 only] bits (1) A, // SError interrupt mask bit bits (1) I, // IRQ mask bit bits (1) F, // FIQ mask bit bits (1) PAN, // Privileged Access Never Bit [v8.1] bits (1) UAO, // User Access Override [v8.2] bits (1) DIT, // Data Independent Timing [v8.4] bits (1) TCO, // Tag Check Override [v8.5, AArch64 only] bits (2) BTYPE, // Branch Type [v8.5] bits (1) ZA, // Accumulation array enabled [SME] bits (1) SM, // Streaming SVE mode enabled [SME] bits (1) ALLINT, // Interrupt mask bit bits (1) SS, // Software step bit bits (1) IL, // Illegal Execution state bit bits (2) EL, // Exception level bits (1) nRW, // not Register Width: 0=64, 1=32 bits (1) SP, // Stack pointer select: 0=SP0, 1=SPx [AArch64 only] bits (1) SSBS, // Speculative Store Bypass Safe )

这些状态在异常时会存入对应的SPSR_ELn寄存器中。SPSR_EL1 寄存器 保存 异常切换目标等级为 EL1 的 ,程序切换前的状态。相应的,SPSR_EL2 SPSR_EL3 保存,异常切换目标等级位 EL2 EL3 的,程序切换前的状态。

在异常发生前,程序可能在 32 位模式 或者 64 位模式。 通过 SPSR_EL1n 的 bit[4] 来确定, bit[4] == 1, 则异常发生前,程序是 32 位模式, bit[4]==0,则异常发生前,程序是 64位模式。根据 bit[4] 为 0 或 1 的不同, SPSR_ELn 的其他 字段也有差异。

异常发生前处于AArch64状态时

异常发生前处于AArch32状态时

PSTATE读写方式

由于SPSR_ELn不能直接读取,要读写异常发生的状态,需要读写专用寄存器。

下面这些字段 可以使用 MSR 指令直接读写

PSTATE.{D, A, I, F, SP, PAN, UAO, SSBS, TCO}

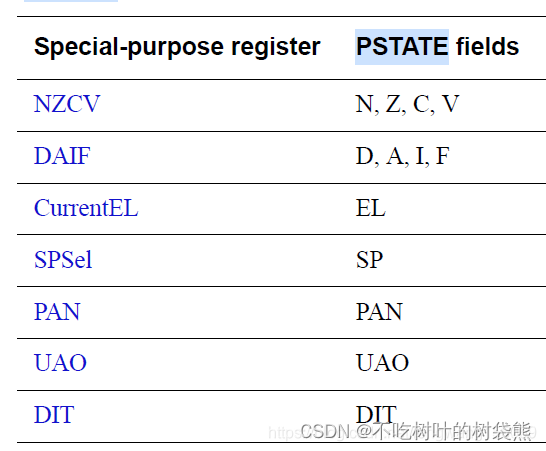

对应的寄存器如下图,其读写可以使用MRS和MSR指令

NZCV

MRS <Xt>, NZCV #读寄存器

MSR NZCV, <Xt> #写寄存器

DAIF

MRS <Xt>, DAIF #读寄存器

MSR DAIF, <Xt> #写寄存器

CurrentEL

MRS <Xt>, CurrentEL

SPSel

MRS , SPSel

MSR SPSel,

PAN

MRS , PAN

MSR PAN,

UAO

MRS , UAO

MSR UAO,

DIT

MRS , DIT

MSR DIT,

这篇关于ARM V8 特殊寄存器之SPSR、ELR和SP的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!