本文主要是介绍接上篇 SSI技术及调试中的BUFMR和BUFR布局布线问题,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一.概述

本篇讲解的问题如下:

(1)为什么有的FPGA有128个BUFG?可是UG472官方文档写的是32个BUFG(详情见前一篇博客,关于时钟资源的介绍),以下是一个1140T的FPGA,有着128BUFG。

(2)BUFMR和BUFR的布局布线问题,该问题由第一个产生。

二.问题解析

1.问题一

首先要了解什么是SSI技术,SSI是Stacked Silicon Interconnect的缩写,即硅堆叠互联技术。Xilinx构建了带宽和容量等于或超过最大单片FPGA芯片的一种FPGA芯片,即具有SSI技术的FPGA。SSI技术使用带有微泵的无源硅插入器和通过硅通孔(TSV)将多个高度可制造的FPGA芯片(称为超级逻辑区(SLR))组合在一个封装中。该技术还允许不同类型的芯片或硅工艺在插入器上互连,这种结构称为异构FPGA。

所以很明了,128个BUFG其实是该FPGA具有SSI硅叠加互连技术,将多个SLR组合在一个封装的结果,而UG472的32个BUFG说法是针对没有SSI技术的单片FPGA芯片。

Note:

每个SLR有3个时钟区高。

SLR之间有interposer clock backbone(插入器时钟主干道),32条全局时钟线能够穿过插入器时钟主干道,从而使一个SLR中的BUFG能够对FPGA中其他SLR进行驱动。

从一个SLR通过interposer clock backbone到相邻SLR的时钟比工作在单个SLR内的时钟会有更多的偏斜。

2.问题二

在项目中用到了117quad和118quad(如图一)的共8个GTH高速收发器,所用mac子系统使能了1588的功能。

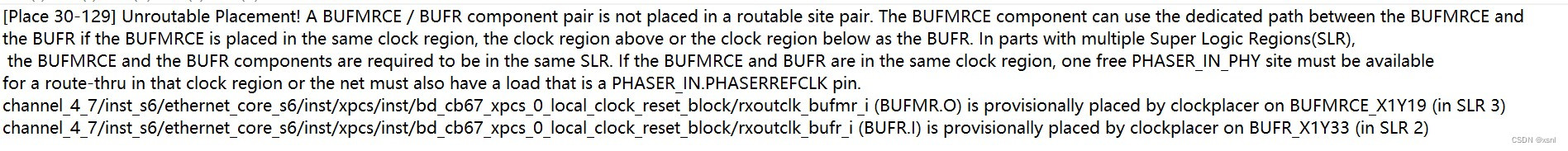

报错第六个和第七个mac子系统的BUFMR和BUFR布局布线通过不了。

查阅官方文档发现,对于SSI的FPGA,BUFMR和BUFR只能置放在同一个SLR中(如图一),图一有4个SLR。

问题解析:一个quad有4个BUFR和2个BUFMR,而使能1588的mac默认用的BUFMR驱动BUFR,BUFR驱动每个端口的RXOUTCLK,而对于一个quad有四个端口,BUFR是够用的,但是BUFMR不够用了。对于117quad,该quad会利用CMT backbone借用116quad的两个BUFMR去驱动BUFR,于是117quad的4个mac子系统(0到3)没有报错,而对于118quad,它的BUFMR不够用,它去借用119quad的BUFMR,但是119quad位于SLR3,118quad位于SLR2,所以违反了BUFMR和BUFR只能置放在同一个SLR中的规则,就会对6-7的mac子系统报错,因为4-5的mac子系统正好有BUFMR给他用(118quad本身有两个BUFMR)。

Note:

CC IO引脚无法在另一个SLR中驱动CMT或BUFG。

BUFMR不能驱动相邻SLR中的BUFR和BUFIO,即BUFMR和BUFR只能置放在同一个SLR中。

BUFG和CMT不能跨越SLR进行连接,即BUFG不能驱动位于其他SLR的CMT。

这篇关于接上篇 SSI技术及调试中的BUFMR和BUFR布局布线问题的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!