本文主要是介绍高速串行总线—PCIE简介,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

PCIE简介

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准。属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽。PCIe有两种存在形式M.2接口通道形式和PCIe标准插槽。

PCIE所支持的速率

PCIe接口的总线带宽是按长度划分的PCIe X1、PCIe X2、PCIe X4、PCIe X8、PCIe X16。

带宽不同,支持的速度也是不一样的。

| X1 | X2 | X4 | X8 | X16 | |

| pcie1.0 | 250MB/S | 500MB/S | 1GB/S | 2GB/S | 4GB/S |

| pcie2.0 | 500MB/S | 1GB/S | 2GB/S | 4GB/S | 8GB/S |

| pcie3.0 | 1GB/S | 2GB/S | 4GB/S | 8GB/S | 16GB/S |

| pcie4.0 | 2GB/S | 4GB/S | 8GB/S | 16GB/S | 32GB/S |

| pcie5.0 | 4GB/S | 8GB/S | 16GB/S | 32GB/S | 64GB/S |

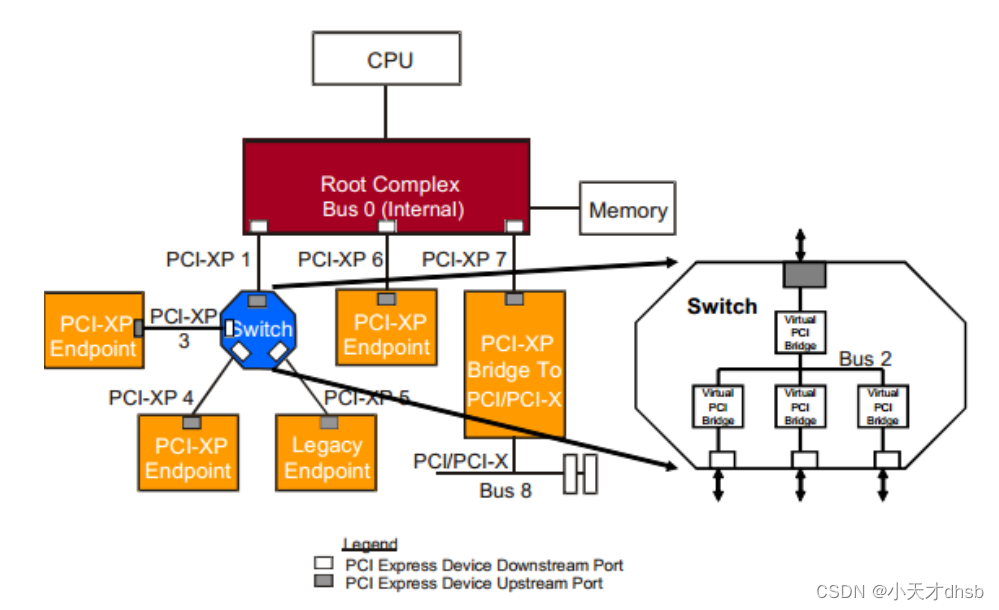

PCIE拓扑模型

pcie设备有两大类,一种是root port,另一种Endpoint。root port相当于一个根节点,将多个endpoint设备连接在一个节点,同时它完成数据的路由。 Endpoint就是最终数据的接受者,命令的执行者。

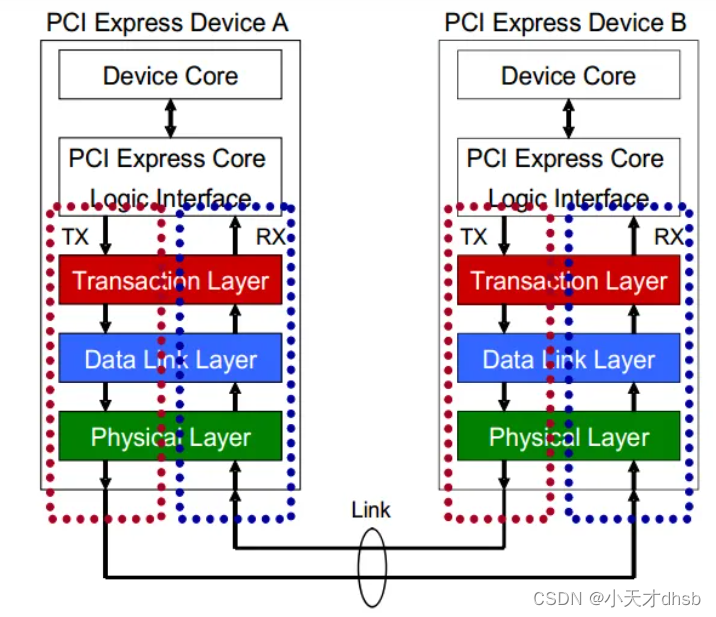

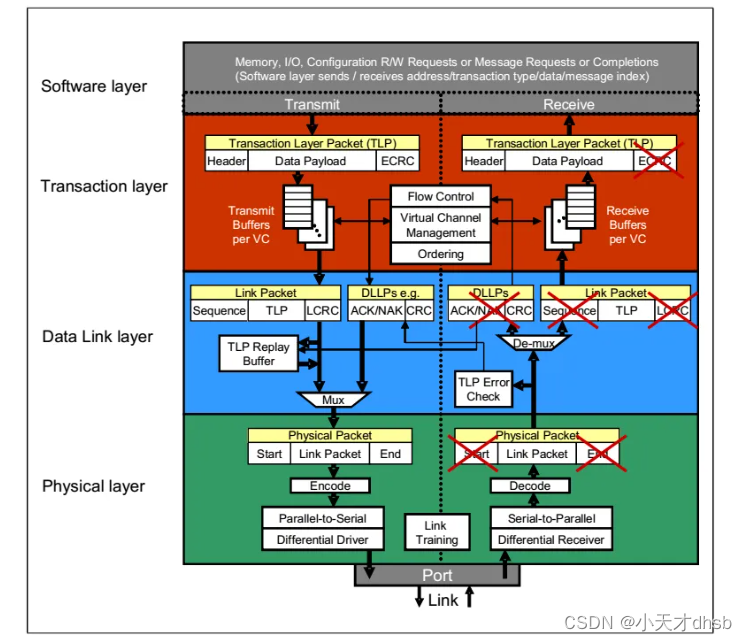

PCIE协议栈模型

在发送端,应用程序(设备核A)在事务层形成事务层包(TLP——Transaction Layer Package),储存在发送缓冲器里,等待推向下层。在数据链路层,在TLP 包上再串接一些附加信息,这些信息是对方接收TLP 包时进行错误检查要用到的,形成数据链路层包(DLLP——Data Link Layer Package);在物理层,对DLLP 包进行编码,占用链路中的可用通道,从发送器发送出去。在接收端,实际上是发送端的“逆”过程。

PCIE实现方式——基于Xilinx IP核

在使用Xilinx IP时三层已经封装好,链路层和物理层对事务层不透明,用户关注事务层,需要实现从上层输出的数据格式到事务层可以接受的数据格式的转换。即用户按照要求的IP核总线协议与之进行数据交换。

PCIE接口的特点

PCIE用于片外高速连接,供电能力更强;稳定性更强;PCIE网卡安装后,不易被外力触碰,更安全可靠;但是PCIE适用性不强,只能在台式机使用;安装拆卸不便,部分型号不支持带电插拔。

这篇关于高速串行总线—PCIE简介的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!