本文主要是介绍MIPI DSI协议解析,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

要学习MIPI协议,不学习DSI协议是不能深刻理解的!

今天我们一起来学习一下MIPI DSI协议;

1:Overview

DSI 全称Display Serial Interface,是由MIPI联盟定义的处理器与外设之间的移动设备接口规范,该规范建立在现有的标准的基础上,并采用了MIPI联盟DBI,DPI,DCS标准中定义的像素格式和命令集,DSI是主要用于显示传输的接口。

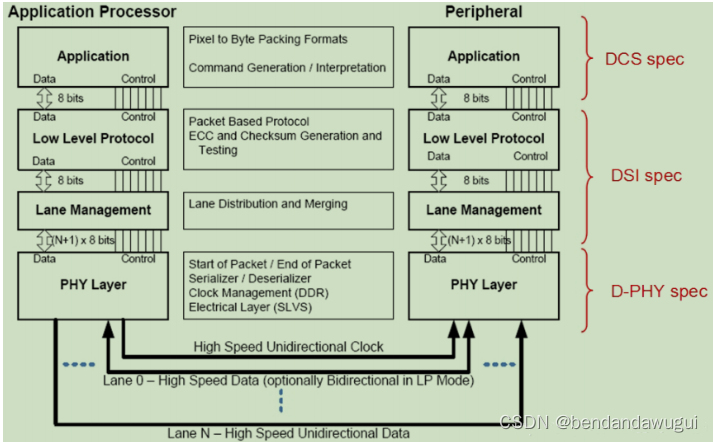

一般而言,完整的的DSI传输如下图所示,从上到下依次为(本文主要关注第二层与第三层)

1:Application:描述了数据流中包含的数据的更高层的编码和解释,根据显示子系统架构,他可能由具有规定格式的像素组成,或者由显示模块的命令组成,可以参考DSC/DPI/DBI spec;

2:Low Level Protocal:该协议规定了通过接口的位和字节的顺序和值,它定义如何将字节组织成定义的组,即数据包,该协议以数据包为最小集合,并为每隔数据包定义了所需要的包头,以及如何生成和解释包头信息,后续发送端将包头和错误检查信息附加到正在传输的数据中;

3:Lane Managment:通道管理,DSI可进行通道扩展以提高性能,根据应用的带宽要求,Data Lane的数量可以是1,2,3,4;

4:PHY Layer:物理层

操作模式:

DPHY有三种操作模式: Escape mode, High-Speed(Burst) mode,及 Control mode。

• MIPI的HS模式(0.2V),传送图像数据,速度为80Mbps ~ 1000Mbps;

• MIPI的LP模式(1.2V),可以用于传送控制命令,最高速度为10Mbps;

• MIPI规定,任一个MIPI设备必须具有Escape Mode,此为LP模式(低功耗模式)中的一种,此模式下可低速传输图像或其他数据。

2.1 从控制模式的停止状态开始的可能事件有:

• Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)

• High-Speed mode request (LP-11→LP-01→LP-00)

• Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)

2.2 Escape mode是数据Lane在LP状态下的一种特殊操作

• 在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger

• 数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00

• 一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作,0x87(LPDT),0x78(ULPS), 0x45(Trigger)。

• Escape mode 使用Spaced-One-Hot Encoding

2.3 超低功耗状态(ULPS, Ultra-Low Power State)

•这个状态下,lines处于空状态 (LP-00)

• 时钟Lane的超低功耗状态

•时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态

•通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms

2.4 高速数据传输 (High-Speed(Burst) mode)

•发送高速串行数据的行为称为高速数据传输或触发(burst)

•全部Lanes门同步开始,结束的时间可能不同。

•时钟应该处于高速模式

2. 5 各模操作式下的传输过程

•进入Escape模式的过程 :LP-11→LP-10→LP-00→LP-01→LP-00→Entry Code → LPD (10MHz)

•退出Escape模式的过程:LP-10→LP-11•进入高速模式的过程:LP-11→LP-01→LP-00→SoT(00011101) → HSD (80Mbps ~ 1Gbps)

•退出高速模式的过程:EoT→LP-11•控制模式 - BTA 传输过程:LP-11→LP-10→LP-00→LP-10→LP-00

•控制模式 - BTA 接收过程:LP-00→LP-10→LP-11

PS:(1)BTA(Bus turn around):总线控制权可在主机端与从机端之间交换,发送端发送放弃总线请求,接收端接收请求之后

控制总线发起应答,总的过程为BTA(bus turn around)操作。(2)Escape mode 和 High-Speed(Burst)

mode之间的状态转换,必须经过stop state状态,不可直接转换。(3)每个字节都是低位先传,多字节元素(16位计数值、 16位CRC)也是低字节低位先传。

2:DSI Mode

DSI 定义了两种基本操作模式,Video模式和Command模式,使用那种模式取决于外设的架构,功能与应用的目标。

2.1 Video模式

Video模式是指从主机处理器到外围设备的传输采用实时像素流形式的操作,一般而言,显示模块依靠主机处理器以足够的带宽提供图像数据,以避免显示图像中的闪烁或其他可见伪影,而一些视频模式架构可能包括一个简单的时序控制器和部分帧缓冲区,用于在待机或者低功耗下保持部分屏幕或较低分辨率的图像,这允许关闭接口以降低功耗,当然为了降低复杂性和成本,仅在Video模式下运行的系统是单向的Data Lane。

# 视频信息只能使用高速模式传输

2.2 Command 模式

Command模式是指其中事务主要采取将命令和数据发送到外设(例如显示模块)的形式的操作,显示控制器需要有本地寄存器和帧缓冲器,处理器通过向显示控制器发送命令,参数和数据来间接控制其显示行为,同时还可以读取显示模块状态信息或帧存储器的内容,故command模式操作需要一个双向的Data Lane。

# 某些显示器仅能在LP模式下初始化

3:DSI Physical Layer

本节简要概述DSI中使用的物理层,有关详细信息可以参考D-PHY——MIPI 系列之 D-PHY_爱洋葱的博客-CSDN博客

DSI使用一个或者多个串行数据信号和一个串行时钟在主机处理器和外围设备之间传输信息,通过总线发送高速串行数据的动作称为HS传输或者Burst,在高速传输之间,差分数据信号或者通道进入低功耗状态(LPS),且接口在不主动发送或者接收高速数据时也应该处于低功耗状态LPS。

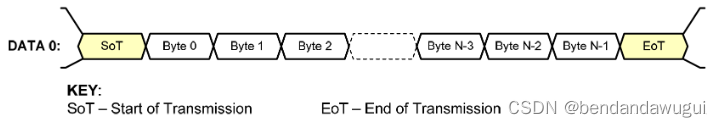

下图为HS模式下的数据传输:

协议规定了一个字节即最小数据单元,一次传输包含N个字节。

3.1:数据流控

由前面的结构可知,底层为协议层将数据发给PHY层,但是协议层和PHY层之间没有握手,一旦传输开始,协议层就可以限制进出PHY层的数据传输,而数据包一共完整无间断的发送和接收,则需要链路两端的协议层和数据缓冲应始终具有等于或者大于PHY层电路的带宽,一个实际的结果是系统实现者应该确保接收器的带宽能力等于或者大于发射器的带宽能力。

3.2 双向性

DSI实现的物理层由一到四个数据通道和一个时钟通道组成,其中:

Command Mode:data lane0应该是双向的;额外的Data lane应是单向的。

Video Mode:Data Lane0可以是双向的或单向的;额外的Data Lane应是单向的。

Note:Clock lane应该由Master驱动,而不能由外设驱动;

LP传输应仅使用Data Lane0;

PHY和协议层之间的接口有几个控制总线方向的信号,当master需要外设的响应时使用,例如返回READ数据或状态信息,它有如下流程:

1:Master在传输的最后一个数据包期间向其PHY断言TurnRequest;

2:PHY层拿到TurnRequest后在Eot序列之后发送BTA(bus turn around)命令;

3:当外设接收到BTA命令时,其PHY层将TurnRequest置为协议层的输入;

4:外设拿到TurnRequest通知其接收协议层准备向master发送响应;

5:外设发送响应后,外设同样使用TurnRequest将总线控制权交换给Master;

BTA机制时需要在LP下实现的

下图为测试过程中抓的一个BTA波形:

3.3 Video Mode Interface

在 Video 模式下运行的 DSI TX 的最低 PHY 要求是:

• Data Lane Module:CIL-MUNN(HS-TX、LP-TX)

• Clock Lane Module:CIL-MCNN(HS-TX、LP-TX)

在 Video 模式下运行的 DSI RX 的最低 PHY 要求是:

• Data Lane Module: CIL-SUNN (HS-RX, LP-RX)

• Clock Lane Module: CIL-SCNN (HS-RX, LP-RX)

3.4 Command Mode Interface

在 Command 模式下运行的 DSI TX 的最低 PHY 要求是:

• Data Lane Module: CIL-MUYY (HS-TX, LP-TX, LP-RX, and LP-CD)

•Clock Lane Module: CIL-MCNN (HS-TX, LP-TX)

在 Command 模式下运行的 DSI RX 的最低PHY要求是:

• Data Lane Module: CIL-SUYY (HS-RX, LP-RX, LP-TX, and LP-CD)

•Clock Lane Module: CIL-SCNN (HS-RX, LP-RX)

3.5 Clock

DSI时钟是从Master到Slave的信号,它可能具有多种功能:

1:Bit Clock:在整个链路上,DSI时钟用作源同步时钟,用于捕获接收器PHY中的串行数据位;

2:Byte Clock:分频后,DSI时钟用于在协议层和应用层之间的概念接口生成Lane Byte Clock

3:Esc Clock:分频后,DSI时钟用于LP模式;

4:Application Clock:DSI位时钟的分频版本可用于其他时钟功能;

所有DSI TX/RX都

这篇关于MIPI DSI协议解析的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!