本文主要是介绍ARM —— CPSR与SPSR,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

CPSR简介

SPSR简介

CPSR简介

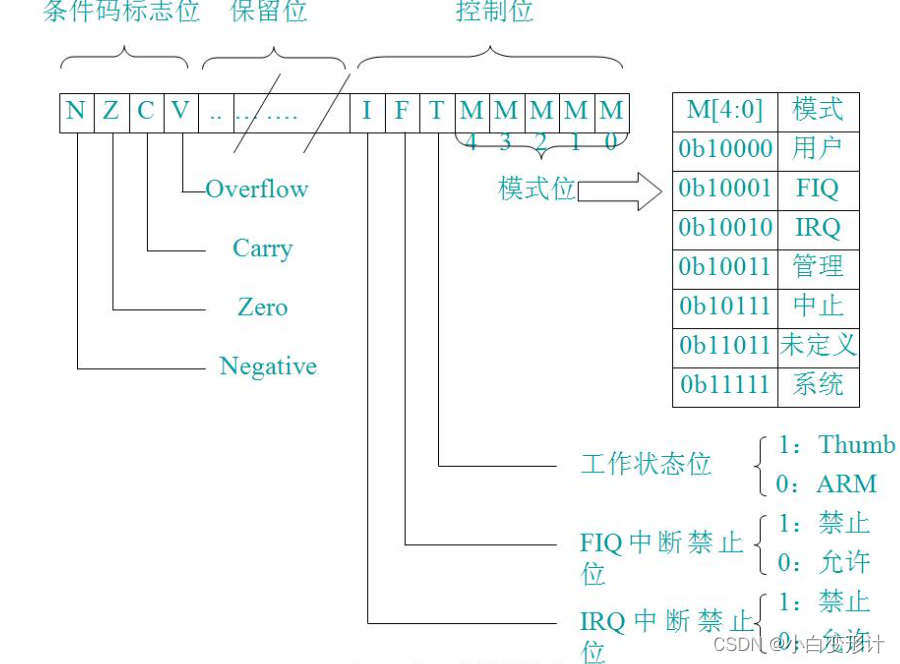

- 全称:程序状态寄存器(current program status register)

- 用户级编程时用于存储条件码

- 任何处理器模式下被访问

- 两种运行状态:ARM状态(32位)、Thumb状态(16位),两种状态之间可任意切换

- 七种运行模式:usr(用户)、fiq(快速中断)、irq(外部中断)、svc(管理)、sys(系统)、abt(数据访问中止)、und(未定义指令中止)

- 寄存器组织(ARM状态):

R0~R14 通用寄存器

R0~R7 未分组寄存器,所有7种运行模式下指向同一物理寄存器,在中断或异常处理等模式转换时,需防止寄存器中数据的破坏。

R8~R14 分组 根据不同的运行模式访问不同的物理寄存器

R8~R12 除fiq外,其余同usr模式

R13~R14 除usr、sys外,其余有各自分组模式

R15 PC 程序计数器

R16 状态寄存器

注:CPSR通用 SPSR 除usr、sys外,用于异常保护的CPSR的备份,异常时,保存CPSR值,异常退出时,将该值恢复到CPSR

SPSR简介

- 全称:程序状态保存寄存器(saved program status register)

- 每一种处理器模式下都有一个状态寄存器SPSR,用于保存CPSR的状态,以便异常返回后恢复异常发生时的工作状态。

- 当特定的异常中断发生时,这个寄存器存放CPSR的内容。

- 在异常中断退出时,可以用SPSR来恢复CPSR。

- 由于用户模式和系统模式不是异常中断模式,所以他没有SPSR。

注:当用户在用户模式或系统模式访问SPSR,将产生不可预知的后果。

这篇关于ARM —— CPSR与SPSR的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!