本文主要是介绍PCI Express学习篇---物理层电气特性(二)Transmitter and Receiver Specificaton,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

声明:此文章为原创,转载请注明 转自https://blog.csdn.net/weixin_48180416/article/details/115979933

此篇为介绍Base Spec中的Transmitter和Receiver电气特性的标准。

Transmitter Specification在Base Spec中有两个表格:Data Rate Dependent Parameters和Data Rate Independent Tx Parameters。

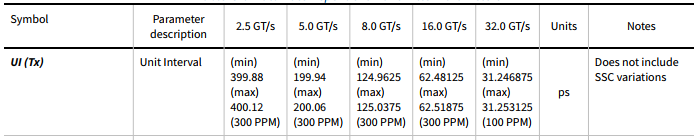

以下为Data Rate Dependent Parameters电压相关参数

不同速率UI不同,1PPM=(1/10^6)*UI, 300PPM=(300/10^6)*UI

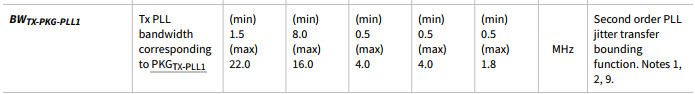

定义了Tx PLL(Rx PLL) bandwidth和peaking,是为了控制refclk的jitter传播到发送的数据(或CDR)

BWtx-pkg-pll1对应的是PKGtx-pll1, BWtx-pkg-pll2对应的是PKGtx-pll2, 可以在lower peaking和lower bandwidth之间权衡,2.5GT/s只有一种。

PKG未给出最小值的时候,non-zero lower limit是0.01dB,比如5GT/s PKGtx-pll1为0.01~3dB

规定正常工作模式下Full Swing differential peak-to-peak 800-1200(GEN3及以上是1300) mVPP

规定正常工作模式下Reduced Swing differential peak-to-peak 400-1200(GEN3及以上是1300) mVPP

规定EIEOS(用于退出EI,block alignment)时 Full Swing和Reduced Swing要求

1)注意Differential peak voltage和differential peak-to-peak voltage的区别。

2)注意Full Swing和Reduced Swing的区别。

当Channel很长或损失严重时可以用Full-Swing全摆幅的电压,但是当Channel很短损失很小,可以用Reduced Swing节约power.

2.5GT/s, 5GT/s时电压下降一半,8GT/s及以上时将TX均衡系数的maximum boost直接限制在3.5dB(1/2)。

Spec中package loss的特别说明:

例如16GT/s Non-Root Package(例如EP)Device does not support captive channels(非受限信道,例如CEM,System board+Add-in Card)

上表的Package loss是Informative(提供信息,不是强制规范)

再比如,16GT/s Non-Root Package(例如EP) Device support captive channels(受限信道,Base Spec中规定的,都在一个PCB板上)

上表的Package loss是Normative(规范)

概括一下就是,上面的package loss是captive channel的规范,为non-captive channel提供参考。

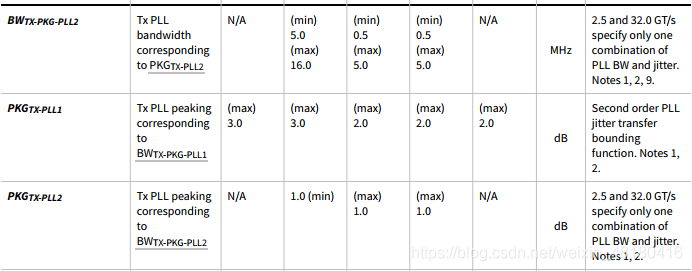

规定了均衡的最大boost电压,均衡的系数调整的分辨率。

Tx de-emphasis去加重,2.5GT/s为2.5-4.5dB通常为3.5dB, 5GT/s可选择 2.5-4.5dB或4.5-7.5dB,通常选择3.5dB或6dB。

以下为Data Rate Dependent Parameters Jitter相关参数

Jitter分为两大类:Data Dependent Jitter和Uncorrelated Jitter.

Data Dependent Jitter,缩写为DDJ,是由于Package loss和reflection产生的,Spec没有明确规定其值范围,

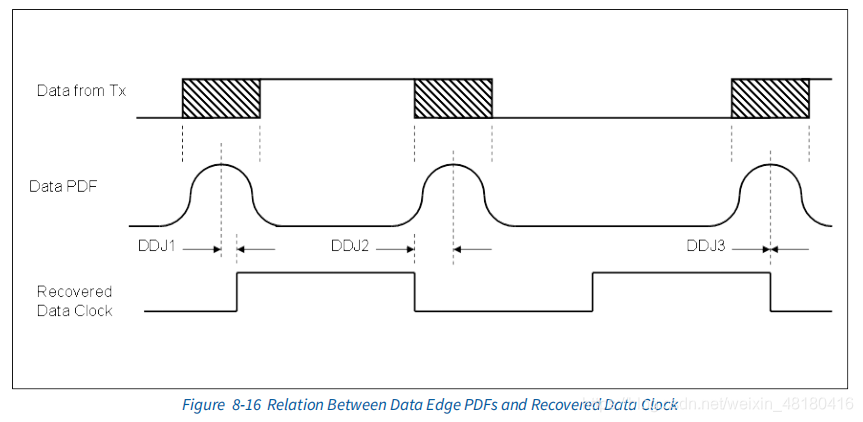

下图为Tx data, recovered clock和data PDF。PDF是概率密度函数。

DDJ是指每一个zero crossing point(0,1跳变的中间点)的概率密度函数均值和恢复时钟之间的偏差。必须有充足的repeat pattern积累来获得稳定的PDF的均值。

Uncorrelated Jitter,是PLL jitter, power supply noise, and crosstalk产生的。

Uncorrelated Total Jitter (UTJ)又包含Dj (Deterministic jitter,确定的Jitter)和Rj (random jitter, 随机的Jitter).

- Dj一般用Dual Dirac Model(双狄拉克模型)来建模,缩写为UDJ-DD。

- Rj为随机抖动,用高斯分布来建模。

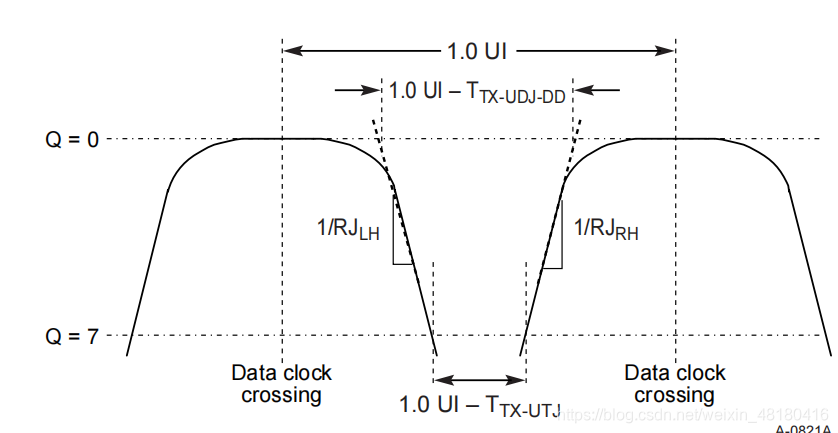

上图是Spec中的图,斜率是1/RJ,UTJ/2 = (Q/2)*RJ + UDJDD/2,BER=10^-12时Q=14

Pulse width jitter(>=5GT/s时),即脉冲宽度的Jitter。

Uncorrelated pulse width total jitter(UPW-TJ)也分为Uncorrelated pulse width Dj(UPW-DJDD, Dual Dirac Model)和Rj

上图是Spec中的图,斜率是1/RJ,UPW-TJ/2 = (Q/2)*RJ + UPW-DJDD/2,BER=10^-12时Q=14

上图中定义了上面提到的各种Jitter的标准。Jitter将在后面的章节详细介绍。

以下为Data Rate Dependent Parameters其他参数

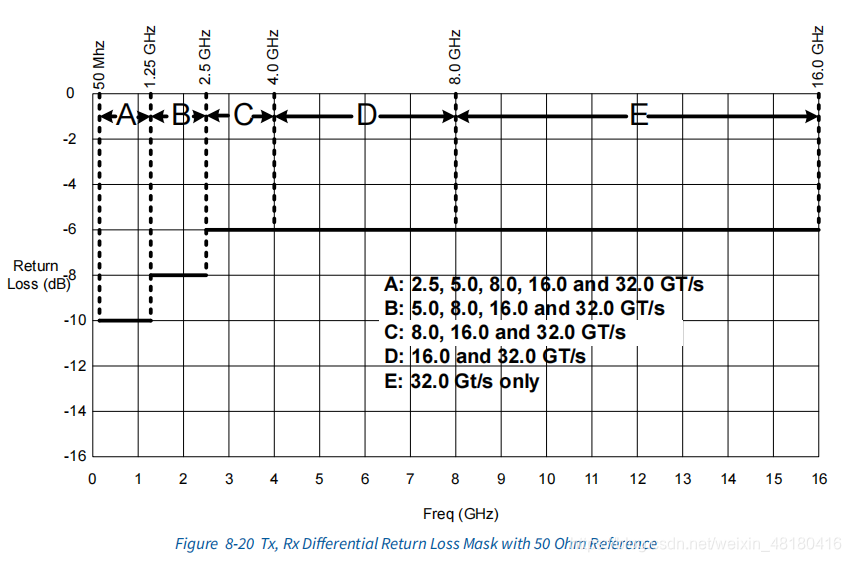

Tx package+die return loss如下图, RX package+die return loss是相同的。下图测量时阻抗为50ohm(差分阻抗是100ohm)

可以用探针直接在package处(Microprobing the package)测量Return Loss。

差分信号RL:(单端RL见Base Spec手册)

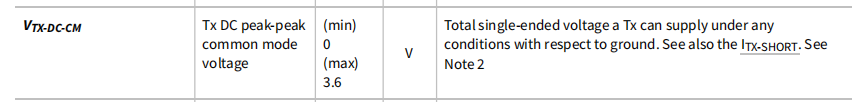

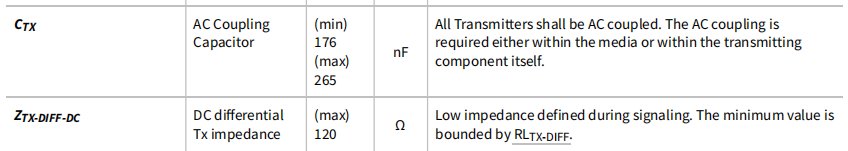

以下为Data Rate Independent Tx Parameters的参数

共模电压范围是0-3.6V

AC耦合电容范围是176-265nF, 靠近发送端,作用是隔直流,使发送和接收的device可以有独立的power和ground, 简化设计。

DC差分阻抗最大值是120ohm。

上面介绍的是部分参数,其他参数见Base Spec。

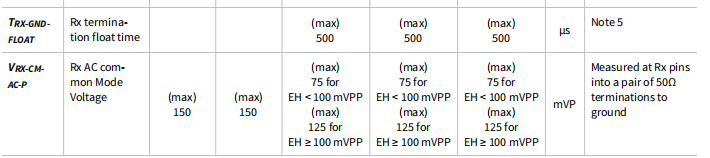

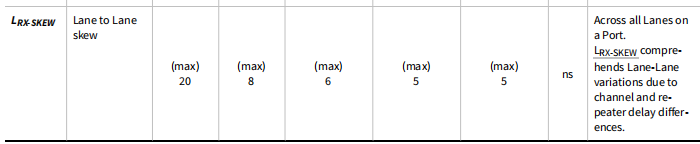

Receiver Specification:Base Spec中定义了一些与压力眼图测试无关的参数。

上面参数的含义和发送端的是一致的,不再赘述。

Trx-gnd-float是指从2.5GT/s 5GT/s过渡到8GT/s 16GT/s 32GT/s common-mode电压改变,receiver input pad "settle new common-mode"的时间。

Vrx-cm-ac-p是需要可靠接收数据时AC峰值电压。

上图为有Receiver时的低阻抗和无Receiver时的高阻抗的一些阻抗标准。

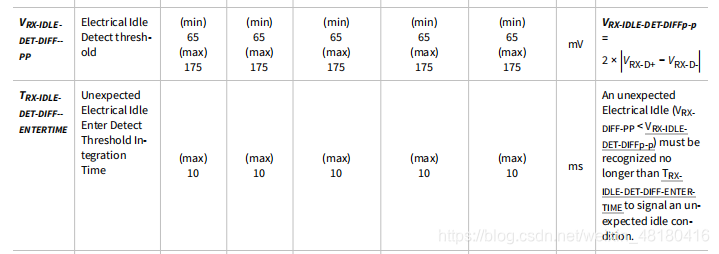

EI的阈值电压,2.5GT/s大于阈值电压表示退出EI,其他速率是检测EIEOS。

Unexpected Electrical Idle是指电压小于Electrical idle detect阈值65-175mV,这个时间不能长于10ms。

这篇关于PCI Express学习篇---物理层电气特性(二)Transmitter and Receiver Specificaton的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!