本文主要是介绍006 跨时钟域(Clock Domain Crossing),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

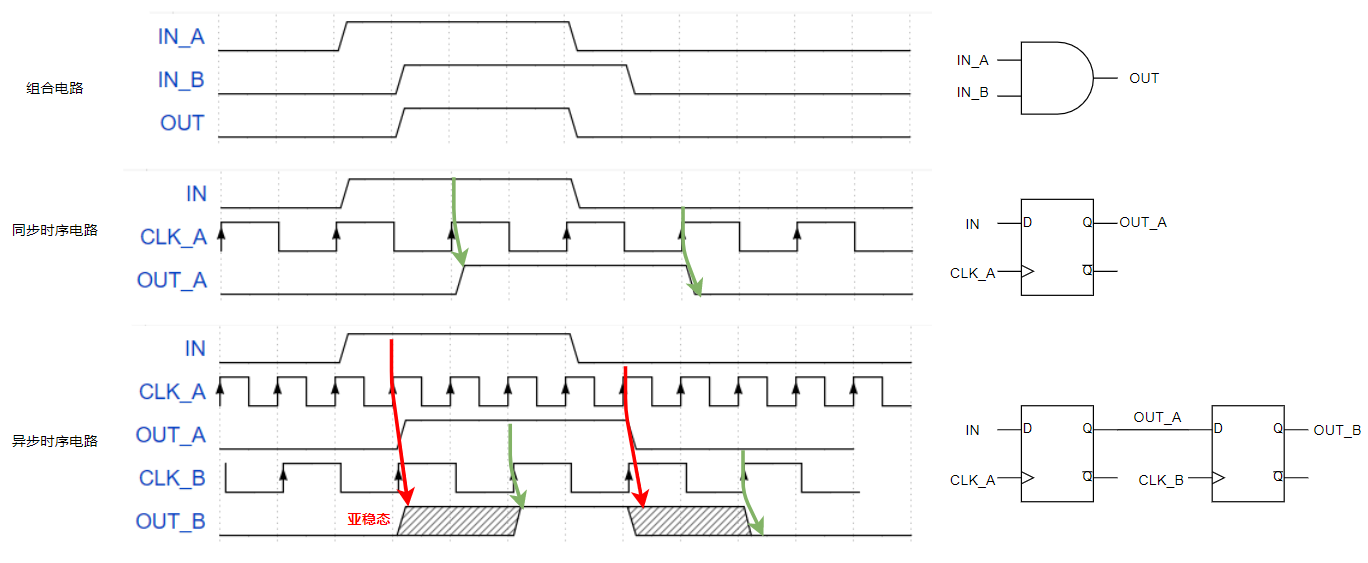

组合电路、时序电路

组合电路

- 任意时刻的输出仅仅取决于该时刻的输入

时序电路

- 任意时刻的输出不仅取决于当前时刻的输入,而且还取决于数字电路原来的状态

同步时序电路

- 利用统一时钟脉冲使其子系统同步运作,在时钟有效沿触发动作

优点

- 设计简单

缺点

- 时钟信号必须要分布到电路上的每一个触发器,功耗高

- 最高频率由最慢路径(关键路径)决定,限制了工作频率

异步时序电路

- 电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件

- 电路中没有统一的时钟

- 电路状态的改变由外部输入的变化直接引起

优点

- 无时钟歪斜抖动(skew,jitter)问题

- 平均能耗低,可复用性好

缺点

- 无统一时钟,状态变化易受影响,抗干扰能力差

- 容易出现冒险竞争

建立时间(setup time)、保持时间(hold time)

- 建立时间(setup time):触发器有效沿到来之前,数据需要保持稳定的最小时间

- 保持时间(hold time):触发器有效沿到来之后,数据需要保持稳定的最小时间

跨时钟域中的亚稳态(metastable)问题

跨时钟域

将控制信号或数据从一个时钟域同步到另一个时钟域

亚稳态(Metastable)

跨时钟域时,原本满足触发器建立和保持条件的信号在新的时钟域中变为异步,可能违背建立和保持条件。在新时钟域中直接对信号采样时,可能采样到非0非1的不稳定状态,使得电路出现错误,因此需要对跨时钟域信号进行同步处理

MTBF(Mean Time Between Failures)

触发器采样失败的时间间隔,可以用来描述触发器进入亚稳态的时间,公式描述如下

M T B F = e t r / T T 0 f t n f c l o c k MTBF={e^{t_r/T} \over T_0f_{tn}f_{clock}} MTBF=T0ftnfclocketr/T

- t r t_r tr:亚稳态分辨时间,输出保持亚稳态但不引起同步器错误的最长时间

- T 、 T 0 T、T_0 T、T0:常数,依赖于触发器的电学特性、工艺及内部设计

- f t n f_{tn} ftn:异步输入频率

- f c l o c k f_{clock} fclock:采样时钟频率

电路工作频率越高,MTBF越小,触发器采样失败的时间间隔越小,越容易发生错误。

引用参考资料中的数据:

一个触发器采样失败的MTBF

t r = 2.3 n s , T = 0.31 n s , T 0 = 9.6 a s , f t h = 100 M H z , f c l o c k = 10 M H z , M T B F = 2.01 d a y s t_r = 2.3 ns, T = 0.31 ns, T_0 = 9.6 as, f_{th}=100 MHz, f_{clock} = 10MHz, MTBF = 2.01 days tr=2.3ns,T=0.31ns,T0=9.6as,fth=100MHz,fclock=10MHz,MTBF=2.01days

信号经过两个触发器任然采样失败的MTBF

M T B F 2 = M T B F × M T B F = 9.57 ∗ 190 y e a r s MTBF_2=MTBF \times MTBF=9.57*190years MTBF2=MTBF×MTBF=9.57∗190years

所以当第一次采到上升沿时,会出现亚稳态,但第二次采样亚稳态时,亚稳态出现的概率基本可以忽略不计

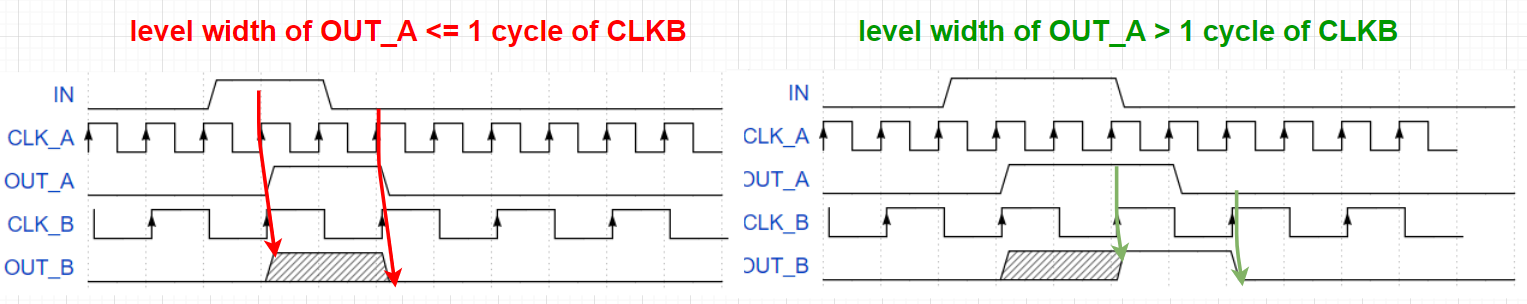

异步信号在新时钟域中的采样

当异步输入信号的宽度 <= 1个新时钟域时钟周期的时候,可能存在采样不到异步输入信号的情况,一般异步输入信号的宽度 >= 1.5个新时钟域时钟周期的时候,新时钟域可以对其进行至少一次采样。

而对于同步后的信号,因为边沿对齐,不存在亚稳态的情况,1个时钟周期的信号至少可以被采样一次

跨时钟域处理

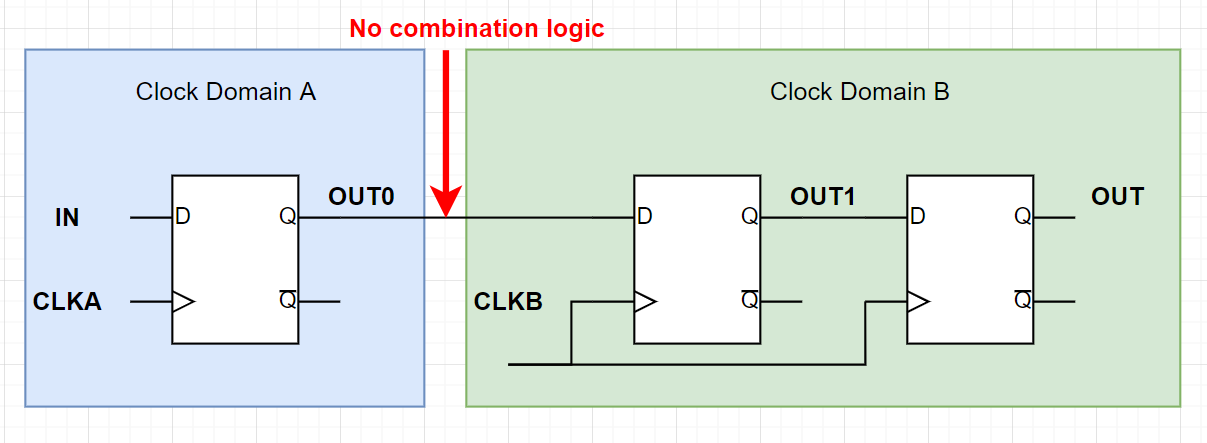

单bit电平同步器(Level Synchronizer)(慢 -> 快)

慢 -> 快:输入的异步信号宽度大于1个新时钟域周期,保证其在新时钟域至少被采样一次

特点

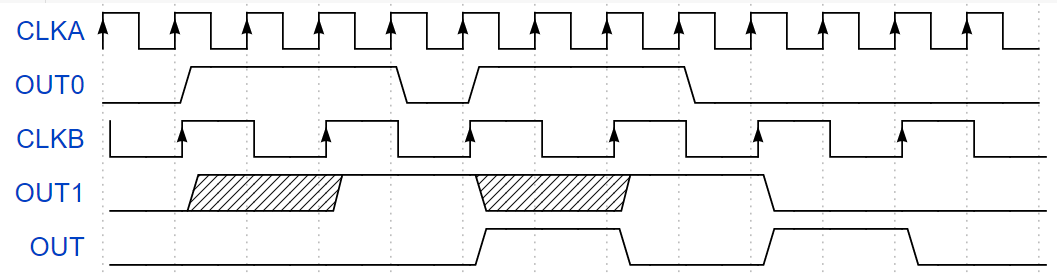

- 0/1 level width of OUT0 > 1 cycle of CLKB

- level interval of OUT0 > 1 cycle of CLKB(存疑)

- No combination login in output of CLKA and input of CLKB(因为会引入组合延迟)

- 1 cycle of CLKB < Delay of signal after sync in CLKB <= 2 cycles of CLKB

异步输入信号的电平间隔是否要大于1个新时钟域周期?

我认为黄框中CLKB并没有采样到稳定的0,所以黄色箭头位置的亚稳态再次取样时应该是1,但如果和第一个电平一样,虽然没有采样到稳定的0,但再次采样会为0,那么黄色箭头的地方就是0,时间间隔的限制就不存在了,如下图所示

从波形上看,OUT0两个1中间的0被同步过来了,但我认为这是错误的,因为,OUT0的0的level width < 1 cycle of CLKB,是不应该被同步过来的,所以我倾向于时间间隔显示是存在的,如果要同步两个level,它们之间的 电平间隔 >1 cycle of CLKB

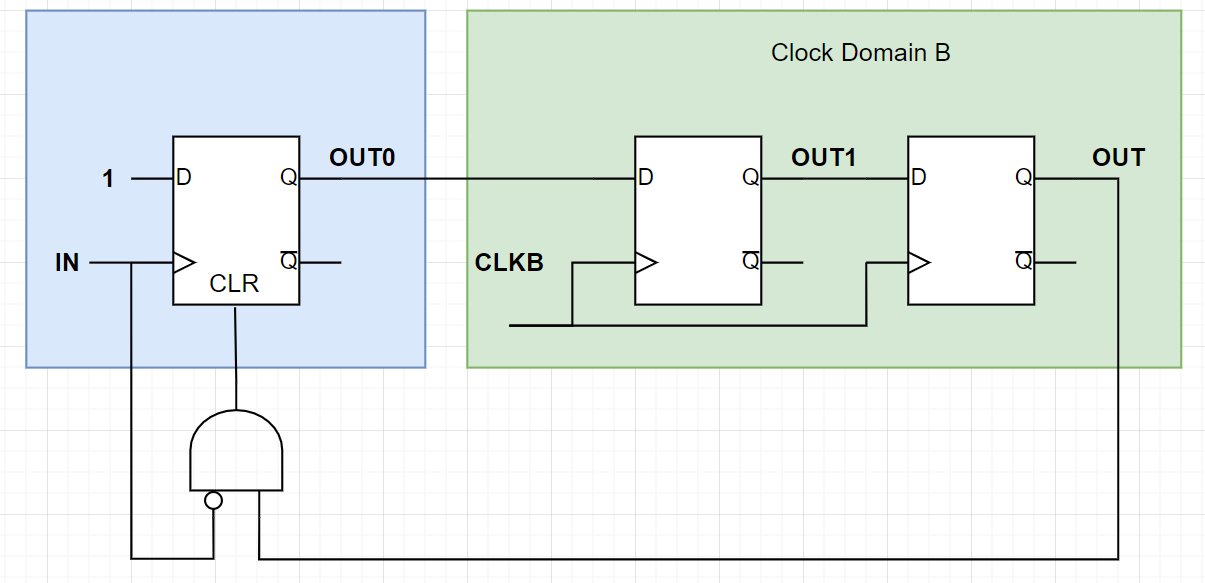

实现

module SYNC_2P(output OUT,input CLKA,input CLKB,input IN

);reg OUT0, OUT1, OUT2;always@(posedge CLKA) beginOUT0 <= IN;

endalways@(posedge CLKB) begin{OUT2, OUT1} <= {OUT1, OUT0};

endwire OUT = OUT2;endmodule

单bit电平同步器(Level Synchronizer)(快 -> 慢)

展宽异步信号(开环)

将异步信号展宽到 > 1个新时钟域时钟周期,一般展宽到1.5-2个新时钟域时钟周期

反馈(闭环)

新时钟域接收到信号后反馈给原时钟域

复位反馈

如果用同样的方法对OUT1的触发器进行复位,就可以得到一个周期长的OUT

缺陷

- 将信号作为时钟,会消耗额外的时钟资源

- 信号的毛刺会导致不可预知的错误

- 不推荐

握手

详见后面

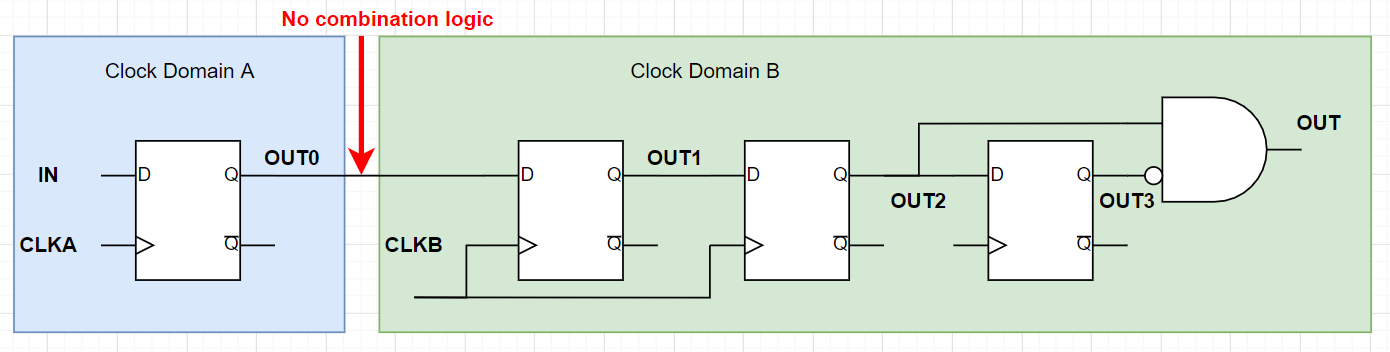

单bit边沿检测同步器(Edge-detecting Synchronizer)

特点

- 0/1 level width of OUT0 > 1 cycle of CLKB

- level interval of OUT0 > 1 cycle of CLKB(存疑)

- No combination login in output of CLKA and input of CLKB(因为会引入组合延迟)

- 1 cycle of CLKB < Delay of signal after sync in CLKB <= 2 cycles of CLKB

此时电平间隔限制与上面的相反,如果亚稳态被采样成1时,是不存在电平间隔限制的,反之,采样后的两个pulse连在了一起,成了一个长pulse,最稳妥的做法还是令*level interval of OUT0 > 1 cycle of CLKB*,给一个缓冲

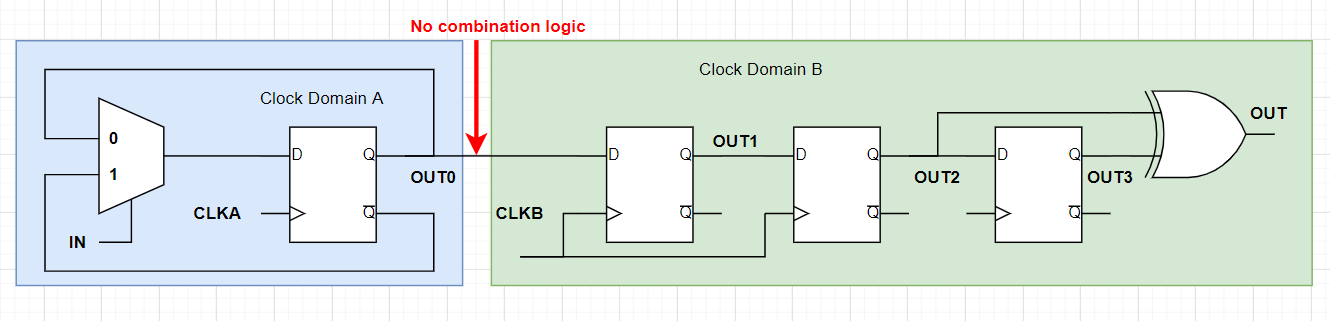

单bit脉冲检测同步器(Pulse Synchronizer)

特点

- 0/1pulse width of IN = 1 cycle of CLKA

- pulse interval of IN > 1 cycle of CLKB(存疑)

- No combination login in output of CLKA and input of CLKB(因为会引入组合延迟)

- 1 cycle of CLKB < Delay of signal after sync in CLKB <= 2 cycles of CLKB

此时电平间隔限制与上面的相同,如果亚稳态被采样成1时,是不存在脉冲间隔限制的,反之,采样后的两个pulse连在了一起,成了一个长pulse,最稳妥的做法还是令*level interval of OUT0 > 1 cycle of CLKB*,给一个缓冲,上图只给了亚稳态被采样成0时的情况,被采样为1时和右下角的图相同,会区分出两个pulse

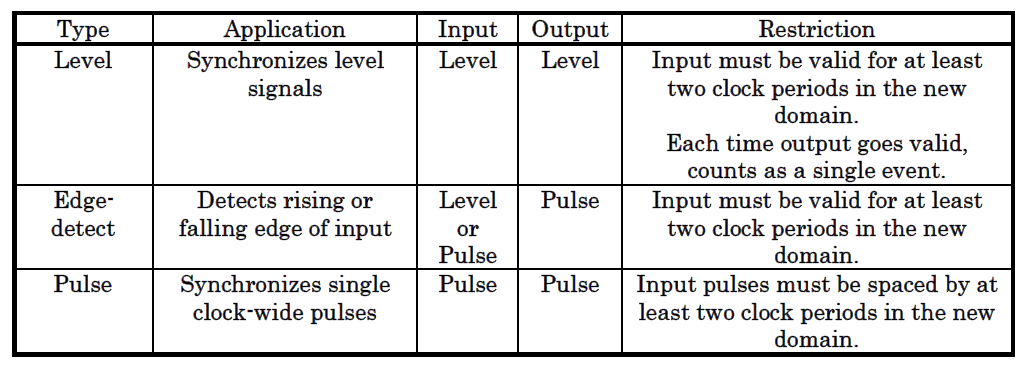

电平、边沿、脉冲对比

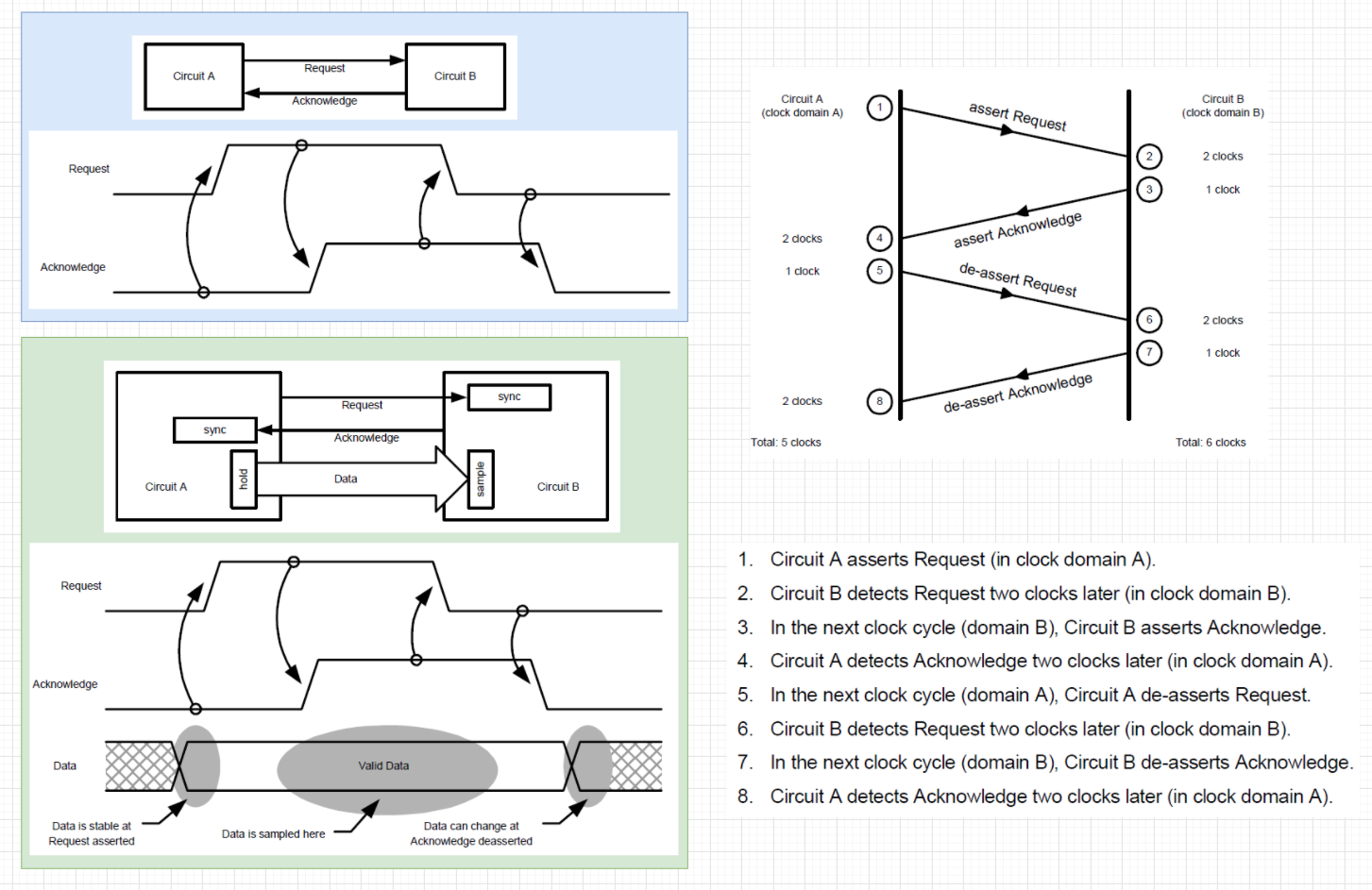

握手(慢 <-> 快,单|多比特)

《Crossing the abyss: asynchronous signals in a synchronous world》写的很详细了

全握手(Full Hanshake)

握手信号要求

- 数据在发送时钟域内稳定至少2个时钟上升沿

- xreq的宽度超过2个时钟上升沿,否则从高速向低速时钟域传递可能无法捕获

缺点 - 传输单bit数据延迟比FIFO大的多

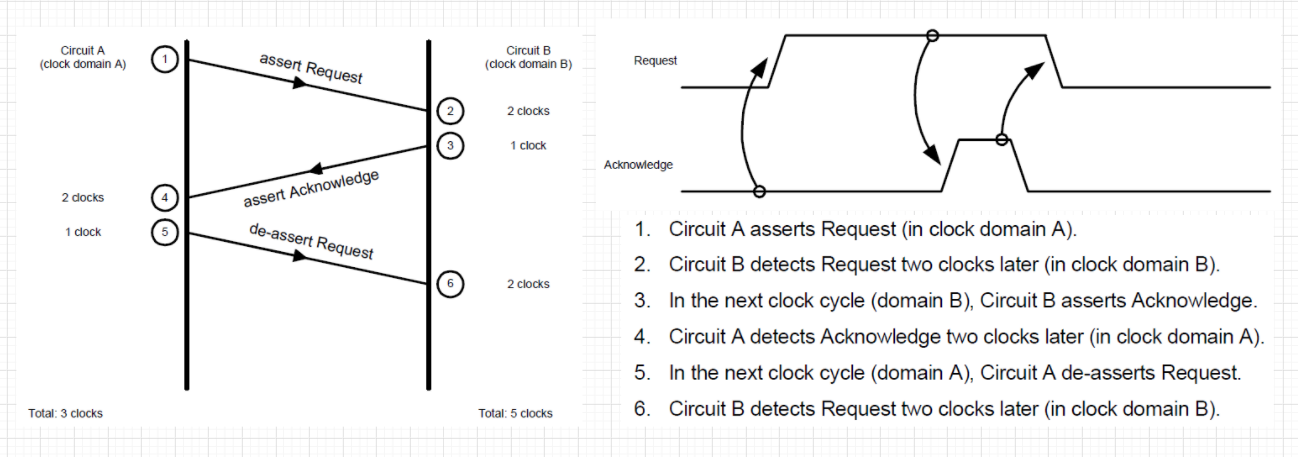

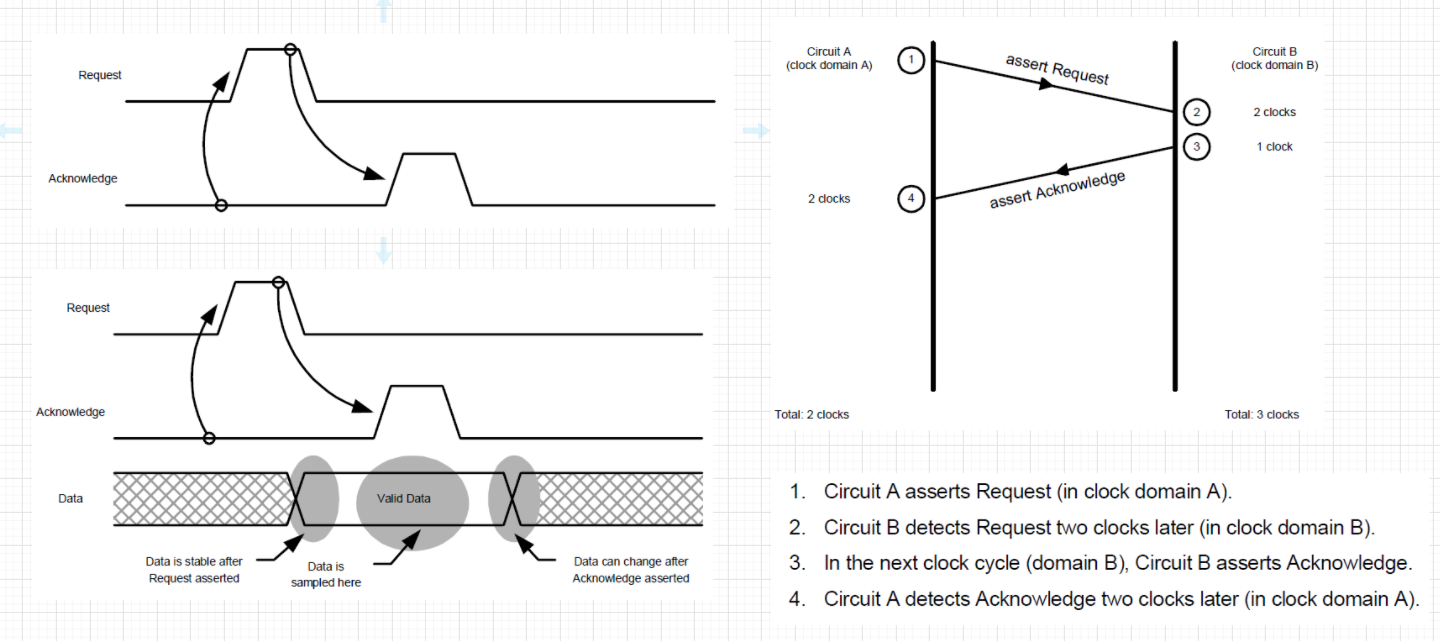

部分握手1(Partial Handshake 1)

部分握手2(Partial Handshake 2)

握手对比

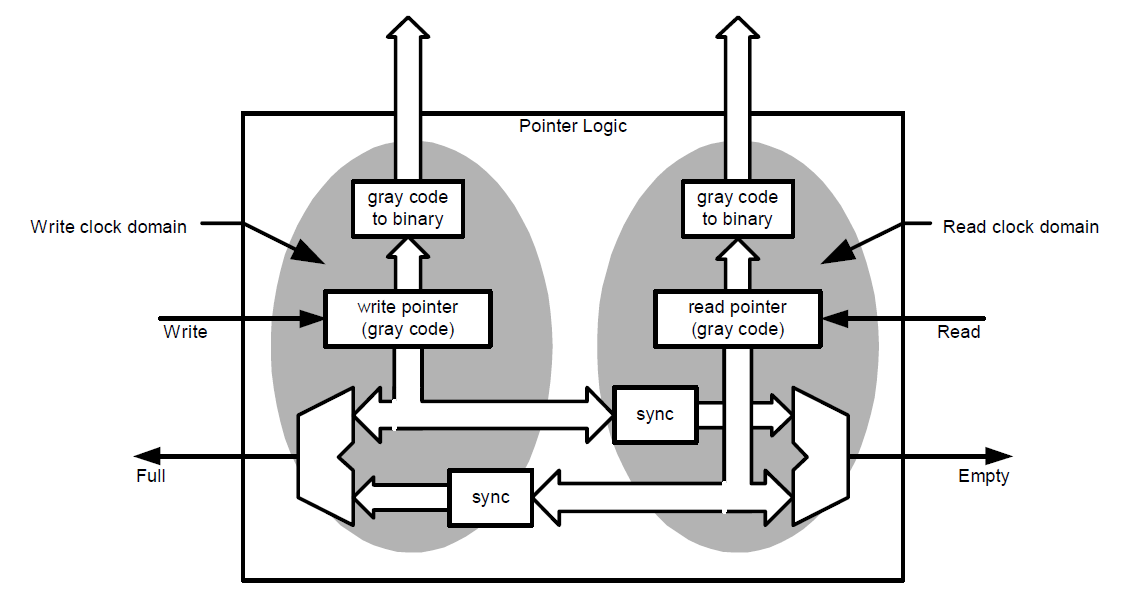

FIFO+格雷码多bit同步

多bit信号,各个bit间可能有时延或者skew,造成数据同步错误,可用异步双口ram或者fifo进行同步。

比如写的频率是80MHz,读的频率是50MHz,突发长度为120,在突发传输过程中,数据都是连续读写的,用一个depth 为45的fifo,可以满足在低速下的异步数据同步。参见FIFO深度计算

高速时可用格雷码,格雷码每次只有1bit翻转,将写地址转换成格雷码,打两拍,在读时钟域解码,相当于单bit。

在线绘图

Wavedrom Editor

同步时序逻辑电路

异步时序电路

FPGA之组合逻辑与时序逻辑、同步逻辑与异步逻辑的概念

静态时序分析

Crossing the abyss: asynchronous signals in a synchronous world

Clock Domain Crossing (CDC) Design & Verification Techniques Using SystemVerilog

Advanced Logic Design and Switching Theory: Metastability

这篇关于006 跨时钟域(Clock Domain Crossing)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!