本文主要是介绍大二下学期个人学习笔记(2)——单周期cpu的设计(37条指令,trace下板,外设下板),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

这篇文章是单周期cpu设计的trace比对版的延续,主要介绍了trace比对通过后,单周期cpu如何进行下板验证,以及如何进行外设的设计,让cpu能跑自己写的汇编代码。

还是那句话,看懂后要自己设计,千万不要照抄!!!

首先介绍trace比对的下板验证。

对于我所设计的37条指令的单周期cpu,下板验证的现象是数码管上的数字(16进制)由25000000逐次加1,最后变成25000025。其前面两位表示需要验证的指令数,最后两位表示验证通过的指令数。

与trace验证不同,trace下板验证是需要导入IP核并实例化IP核的(在vivado软件中进行)。

其需要用到的IP核有三个,分别是时钟IP核、程序ROM的IP核与数据RAM的IP核。

其中,时钟IP核的导入按照指导书上来就行。另外两个IP核则是导入老师给的,里面存放着与trace验证相关的东西。

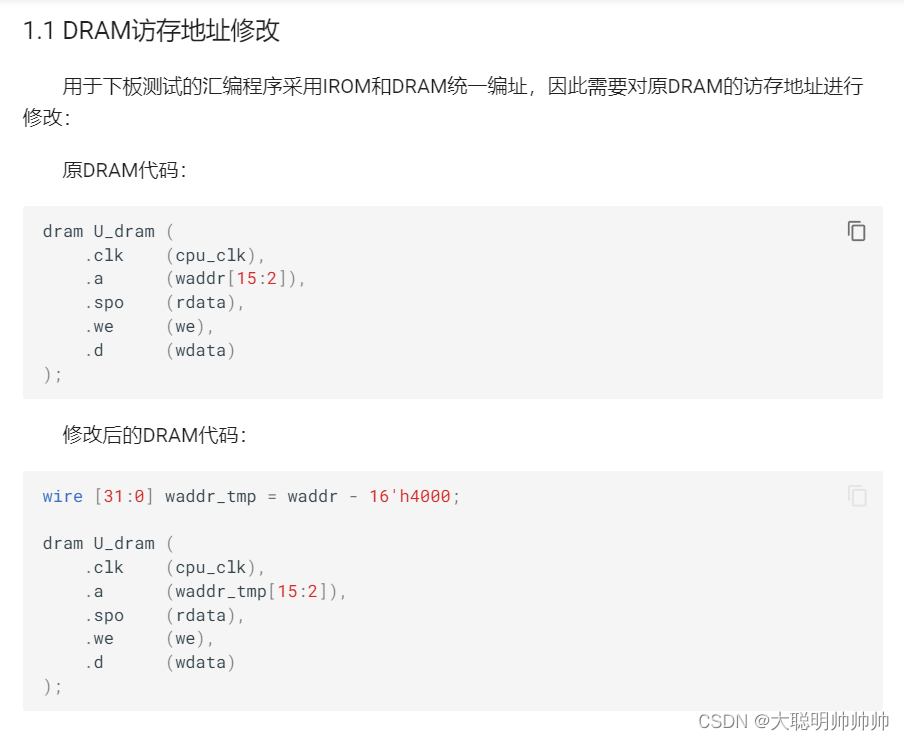

然后要注意的是,DRAM访存地址需要修改,如图:

有人可能会疑惑,那我输入到板子上的数据是从哪来的?怎么验证自己cpu可以通过多少条指令?

其实这些老师已经给我们做好了,只要导入之前所说的、老师给的那两个IP核就行。至于板子上的数据,老师给的验证代码中,就包含了这个数据,存放在x19寄存器里面。所以我们只需要用线把x19寄存器连到板子上就行。

至于板子上的数码管是怎么亮的,约束文件怎么写,我们在上学期的相关的verilog课程中已经学过以及写过了。

看到这,有能力的小伙伴已经可以做出来了。下面是我给的参考代码,仅供参考,不要抄袭!!!

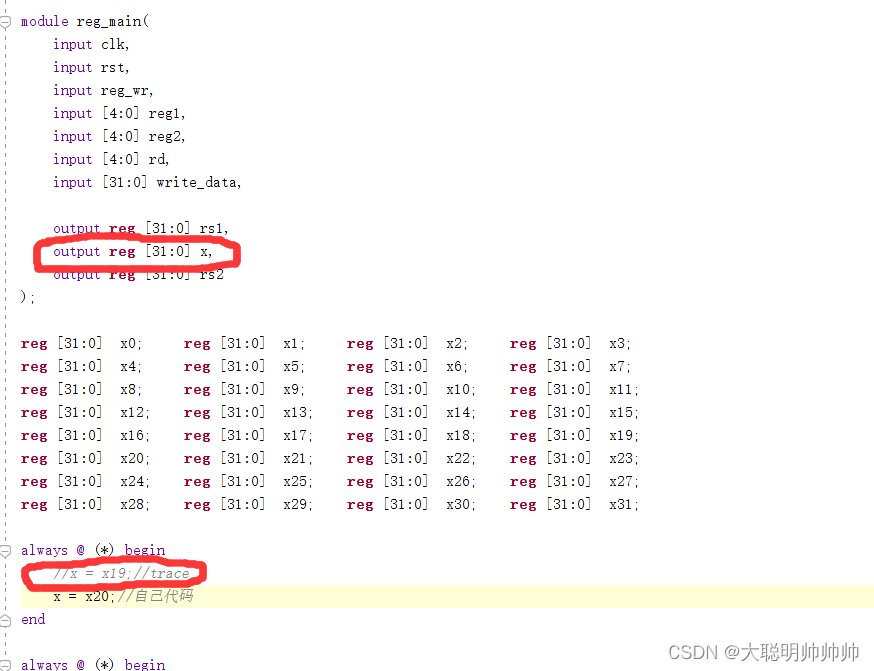

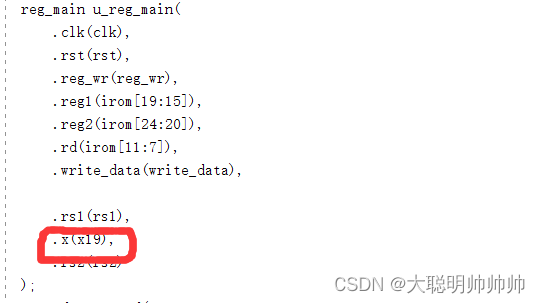

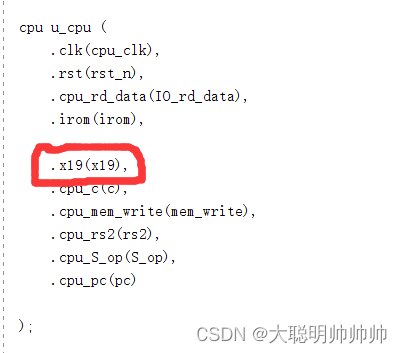

寄存器模块用一根线引出寄存器x19的值(红色圈出的部分):

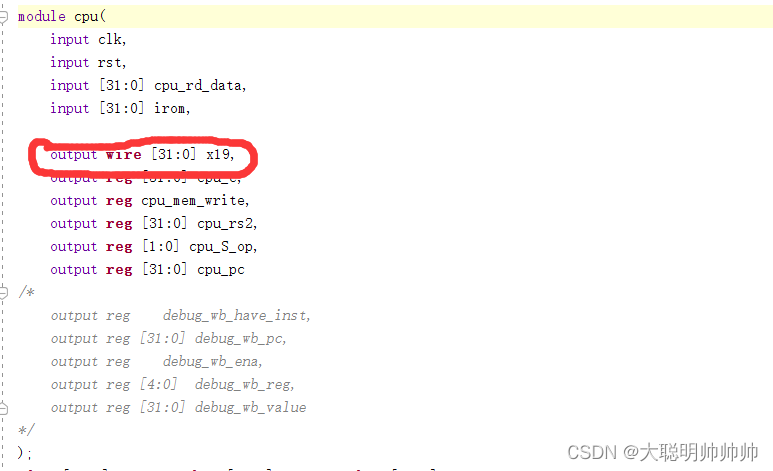

然后就需要把这个值传给顶层文件top,因为寄存器模块是在cpu模块实例化的,而cpu模块才是在top模块实例化,所以我们传数时要经过cpu模块来传数。

cpu模块:

在此一提,那些debug信号对于下板是没有用的,可以注释掉。

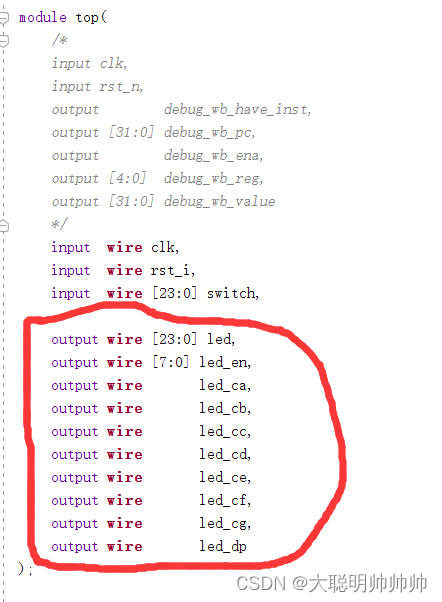

cpu模块取得x19的值后,再传给top模块。

top模块:

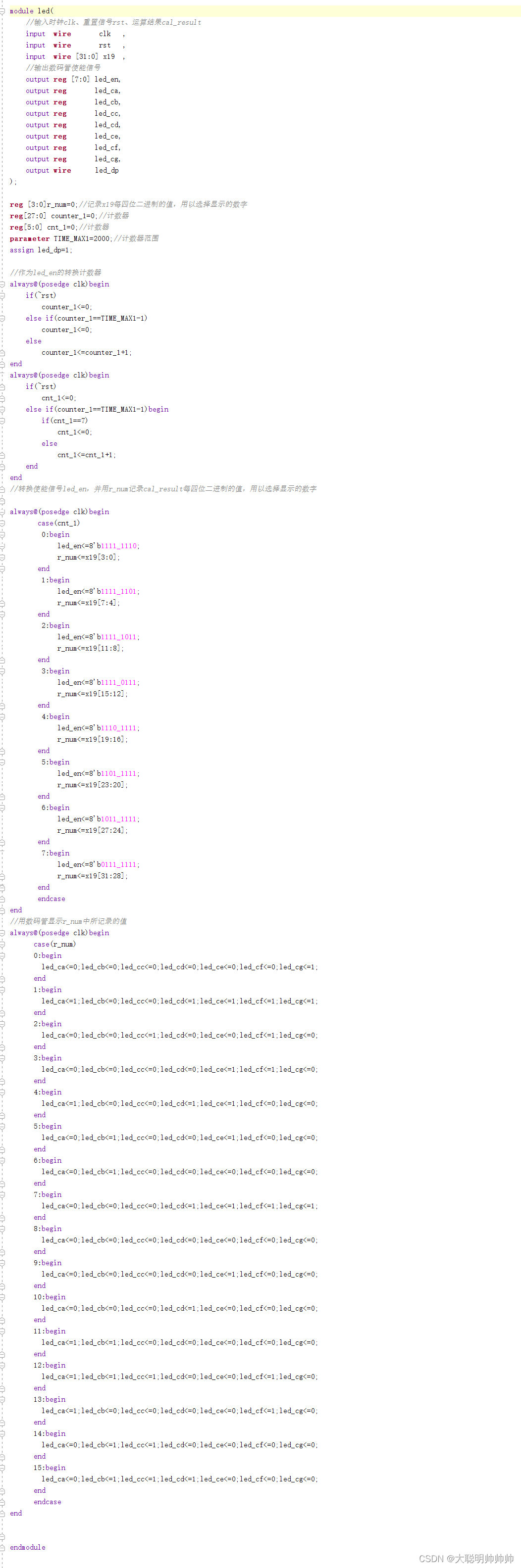

最后就是怎么在板子上显示数据的问题了,这在我们以前做的相关实验中有说,因此我在这就不多说了,直接上码。

数码管显示模块:

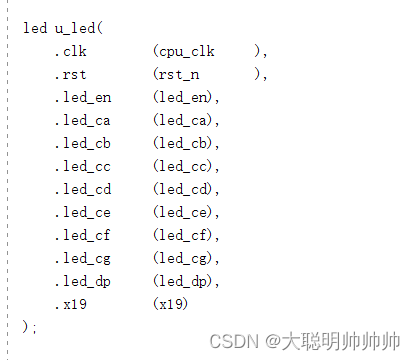

在 top模块将led模块实例化:

再然后,就可以开始写约束文件了。

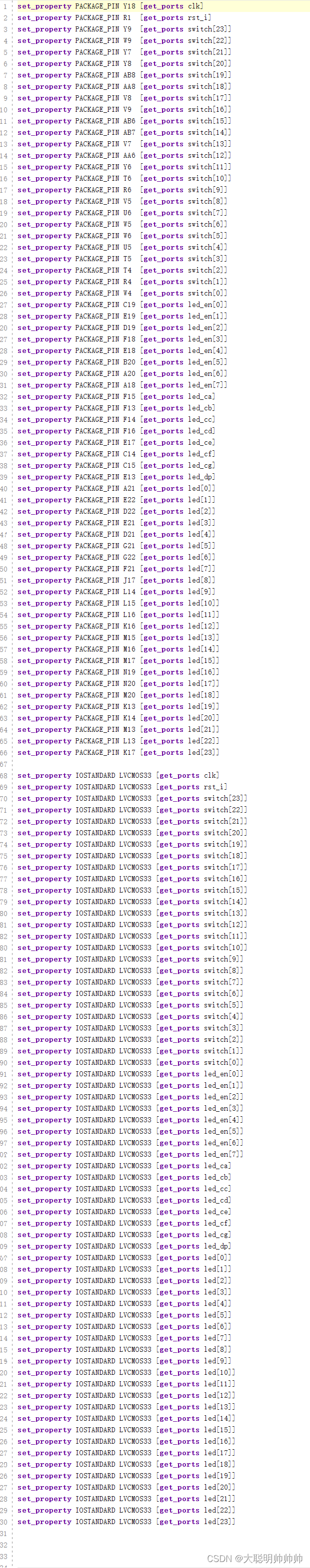

约束文件(外设也是这个,switch信号就是外设的,下面会讲):

好了,trace比对下板验证到这就结束了,一定要理解,然后自己写!不要照抄!!!

下面就说一下关于外设部分如何设计。

其实,外设部分的主要问题应该就是不懂怎么在板子和cpu之间传送数据,这就和我们汇编时写的lw和sw指令有关。

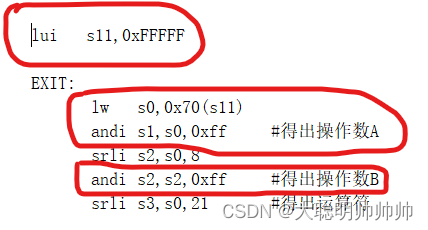

这是我的一部分汇编代码:

结合外设基地址来看:

相信大家已经找到这之中的联系了吧。

然后,我们要思考的就是怎么传数,这就和上面说的switch信号有关了,下面也是直接上码,结合我之前所说以及实验指导书来思考。

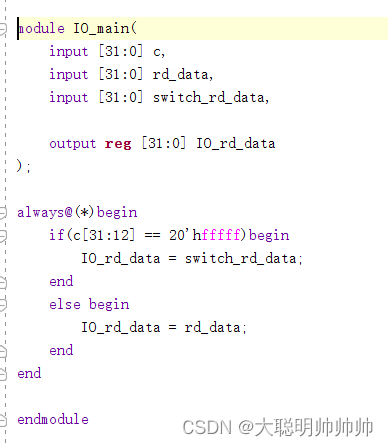

IO接口部分:

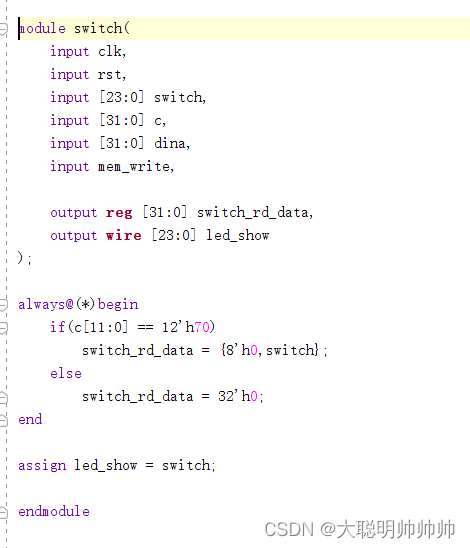

switch模块:

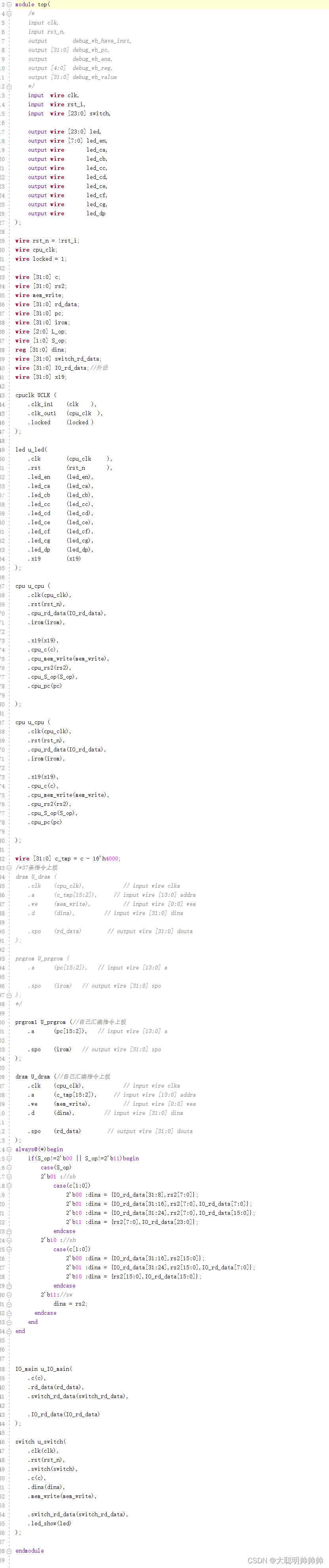

top模块:

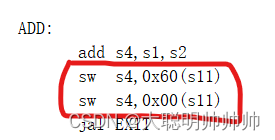

然后需要注意的是,我的汇编代码是把计算结果存放在s4寄存器(也就是x20寄存器),所以我直接用一根线从寄存器模块取出x20的值,赋给led模块就行了(之前图片中也有)。

行了,外设部分到这就结束了。大家理解后,自己动手设计。

重要的事情说三遍!!!

千万不要抄袭!!!

千万不要抄袭!!!

千万不要抄袭!!!

各位看官觉得有帮助的话,点赞、关注和评论支持我一下呀!

相关的(.v文件)我也上传了,是外设部分的,而trace上板部分也只需要按照前面所说小改一下就行,链接如下:

单周期cpu的设计-trace和外设上板验证-verilog-计算机组成原理-其它文档类资源-CSDN文库

这篇关于大二下学期个人学习笔记(2)——单周期cpu的设计(37条指令,trace下板,外设下板)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!