本文主要是介绍【FPGA】关于KC705开发板的差分时钟(主时钟为差分100M),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

写作时间:2020-03-08

开发环境:vivado2019.1

readme:

最近在学习FPGA,第一个实例当然是流水灯了,我已经将之整理为博客。

FPGA实现led流水灯 (工程+代码)

这个工程,使用的开发板,给FPGA的主时钟是单端时钟,然而我想把这个工程套用在xilinx KC705上,发现不是那么顺利。

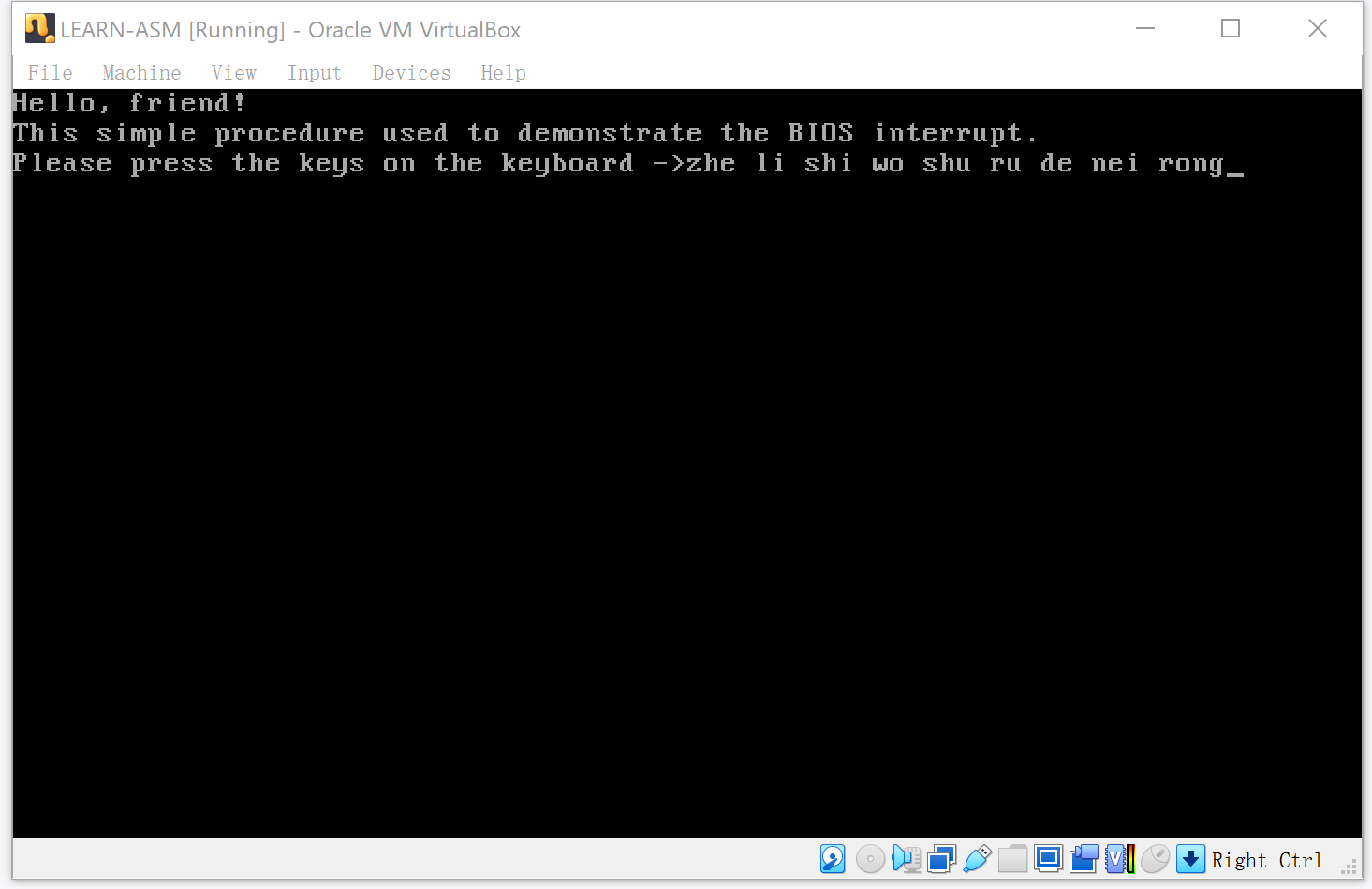

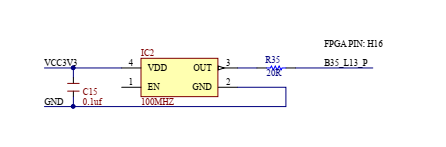

我自己的开发板,主时钟是单端时钟,如下图:

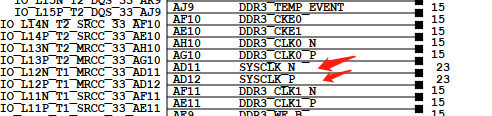

因为KC705上的主时钟是差分时钟,如下图:

对于差分时钟,我们需要在==.v文件和约束文件xdc==中修改下,才可以生成bit正常。

1).v文件 修改如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//module run_led(input sys_clk_p,input sys_clk_n,input RSTn_i,output reg [3:0]LED_o

);

//*********差分时钟这么处理***********

wire CLK_i;

//对差分时钟采用IBUFGDS IP核去转换

IBUFGDS CLK_U(

.I(sys_clk_p),

.IB(sys_clk_n),

.O(CLK_i)

);

//**********************************

reg [31:0] Cnt;

always @(posedge CLK_i )if (RSTn_i==1)//复位begin LED_o<=4'b0001;end

elsebeginif (Cnt==32'd200_000_000)beginCnt<=32'd0;if(LED_o==4'b1000)beginLED_o<=4'b0001;endelse begin LED_o<=LED_o<<1'b1;endendelsebeginCnt<=Cnt+1'b1;LED_o<=LED_o;endendendmodule

2)约束文件xdc 修改如下:

#vivado管脚约束XDC文件

#*********差分时钟这么处理***********

set_property PACKAGE_PIN AD12 [get_ports {sys_clk_p}]

#//只需要约束p端

set_property IOSTANDARD DIFF_SSTL15 [get_ports {sys_clk_p}]

#//注意这里的电平标准

set_property IOSTANDARD DIFF_TERM true [get_ports {sys_clk_p}]

#//只需要约束p端

set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

#//可以忽略掉drc error

#**********************************#rst_n

set_property PACKAGE_PIN AG5 [get_ports RSTn_i]

set_property IOSTANDARD LVCMOS15 [get_ports RSTn_i]

#LED_o

set_property PACKAGE_PIN AB9 [get_ports {LED_o[3]}]

set_property IOSTANDARD LVCMOS15 [get_ports {LED_o[3]}]

set_property PACKAGE_PIN AC9 [get_ports {LED_o[2]}]

set_property IOSTANDARD LVCMOS15 [get_ports {LED_o[2]}]

set_property PACKAGE_PIN AA8 [get_ports {LED_o[1]}]

set_property IOSTANDARD LVCMOS15 [get_ports {LED_o[1]}]

set_property PACKAGE_PIN AB8 [get_ports {LED_o[0]}]

set_property IOSTANDARD LVCMOS15 [get_ports {LED_o[0]}]#set_property CONFIG_MODE <configuration_mode> [current_design]

#set_property BITSTREAM.CENERAL.COMPRESS TRUE [current_design]

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]这样修改后,bit 生成正确,流水灯跑起来了哈~~

其他项目中,FPGA的时钟为差分时钟的时候,完全可以套用本文方法。

补充:

关于复位,说明如下:

GPIO_SW_E是直接连接到FPGA管脚上,下拉到地,按键断开时,常为低电平。按键按下闭合,为高电平。

我们想要实现的就是,按键按下,为高电平时候,进行复位。

THE END~

【MATLAB-app】系列教程(含视频)00_csdn上第一套关于matlab appdesigner系列“视频课”来啦~~

【图像算法&MATLAB】一文讲明白:图像的直方图均衡化(附作者自编源代码)

【探测器与相机标准】我对图像(图像传感器/相机)“非均匀性”的理解与学习笔记

这篇关于【FPGA】关于KC705开发板的差分时钟(主时钟为差分100M)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!