本文主要是介绍LPC1768@100MHz和LPC1788@120MHz的PLL0设置,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

对于搞软件开发的来说,弄一些硬件相关参数总觉得有点没底。做了几年,总算知道锁相环(PLL)的作用是把一个输入频率“放大”后输出,虽然对PLL的电路原理还是一窍不通。最近研究LPC1788和LPC1768的主频时发现两者的PLL0配置相差挺多的,于是耐着性子啃了User manual,总算理清楚了(作为软件开发者,某些太细节的硬件原理就不去深究了)。

首先LPC1788工作在120MHz是没问题的,但LPC1768的最高频率只能是100MHz(LPC1769可以到120MHz,但估计大陆很少有人会去用这片子)。

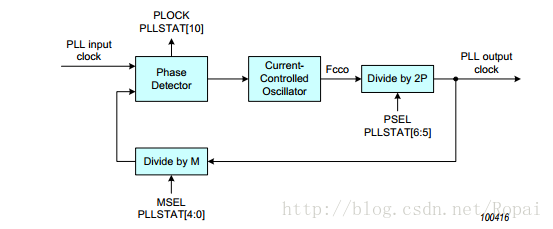

LPC1788 的PLL原理图

其中MSEL和PSEL分别是指PLL倍频器值(M)和PLL分频器值(P)。在LPC1788的寄存器PLL0CFG可以设置。

Fcco指PLL电流控制振荡器的频率。

所以根据上图 PLL的输出频率 PLL_out_clk = PLL_in_clk x M 或PLL_out_clk = Fcco/(2xP)

可以看出PLL输出频率只由PLL_in_clk和M值决定,而P值是用来决定Fcco的(Fcco限制工作范围是156MHz~320MHz)

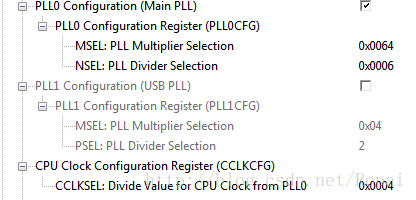

然后看下Keil中LPC1788的时钟配置

外部晶振(Main Osicallor)为12MHz,可以算出PLL_out_clk = 12MHz x 10 = 120MHz

而LPC1788的主频率 cclk = PLL_out_clk / CCLKDIV = 120MHz / 1 = 120MHz

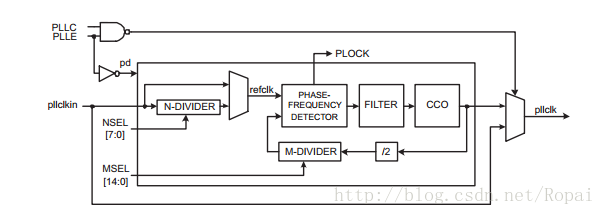

再来看下LPC1768的PLL原理图

细心的可以发现这里是NSEL而不是PSEL, 查阅官方手册,NSEL是指Pre-Divider。和LPC1788的PLL工作方式不同,LPC1768的PLL是先分频和倍频,Fcco就等于输出的PLL频率。

于是 PLL_out_clk = Fcco = PLL_in_clk x M x 2 / N

可以看出PLL输出频率与M值和N值都有关,而LPC1768的Fcco的范围是(275MHz~550MHz),Ps: LPC1788的Fcco更低,是不是更省电?

同样看下Keil中LPC1768的时钟配置

为什么这么配肯定是有道理的(有兴趣请参见LPC176x User Manual中第4章)。

外部晶振同样是12MHz, 于是PLL_out_clk = Fcco = 12MHz x 100 x 2 / 6 = 400MHz

而LPC1768的主频 CCLK = PLL_out_clk / CCLKSEL = 400MHz / 4 =100MHz

于是,笔者就弄明白了同样12MHz外部晶振下,怎么配置PLL以把LPC1788和LPC1768分别工作在120MHz和100MHz

这篇关于LPC1768@100MHz和LPC1788@120MHz的PLL0设置的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!