100mhz专题

基于FPGA和STM32的频率计设计(100Mhz-1hz精确到0.1hz)

目录 1. 前言2. 设计2.1 要求2.2 说明2.3 设计方案 3. 实现3.1 顶层模块3.2 预采样模块3.3高频测量模块3.4 低频测量模块3.5 定时器模块3.6 TestBench代码3.7 约束xdc文件 4. 后言 1. 前言 2019年8月20日:本人一名FPGA的菜鸟,为了准备电赛,几天前完成了FPGA频率计和相位差测量的FPGA工程,这算我独立完成的FP

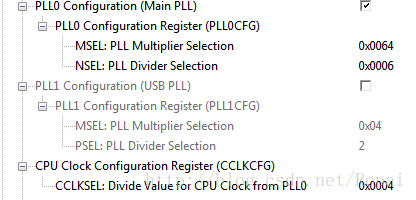

LPC1768@100MHz和LPC1788@120MHz的PLL0设置

对于搞软件开发的来说,弄一些硬件相关参数总觉得有点没底。做了几年,总算知道锁相环(PLL)的作用是把一个输入频率“放大”后输出,虽然对PLL的电路原理还是一窍不通。最近研究LPC1788和LPC1768的主频时发现两者的PLL0配置相差挺多的,于是耐着性子啃了User manual,总算理清楚了(作为软件开发者,某些太细节的硬件原理就不去深究了)。 首先LPC17