本文主要是介绍数字逻辑综合工具 synopsis DC学习笔记(二),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1.setup文件

history 查看过去执行的命令

alias 重命名 history命名为h

2.用read指令读入verilog文件

读入多个文件时,读入的首个文件默认为顶层文件,也可用连接符同时读入多个文件,首个文件默认为顶层文件。

还可以通过current_design指定顶层文件。

在link后,可以通过check_design检查电路是否有问题。若error = 0,则有问题。

另外,还可以用analyze-elaborate代替read

analyze生成一个.pvl文件(中间格式),然后通过elaborate转化为GETCH格式,同时指定顶层。

3.source命令设置约束

如果没有正确配置path则会报错。

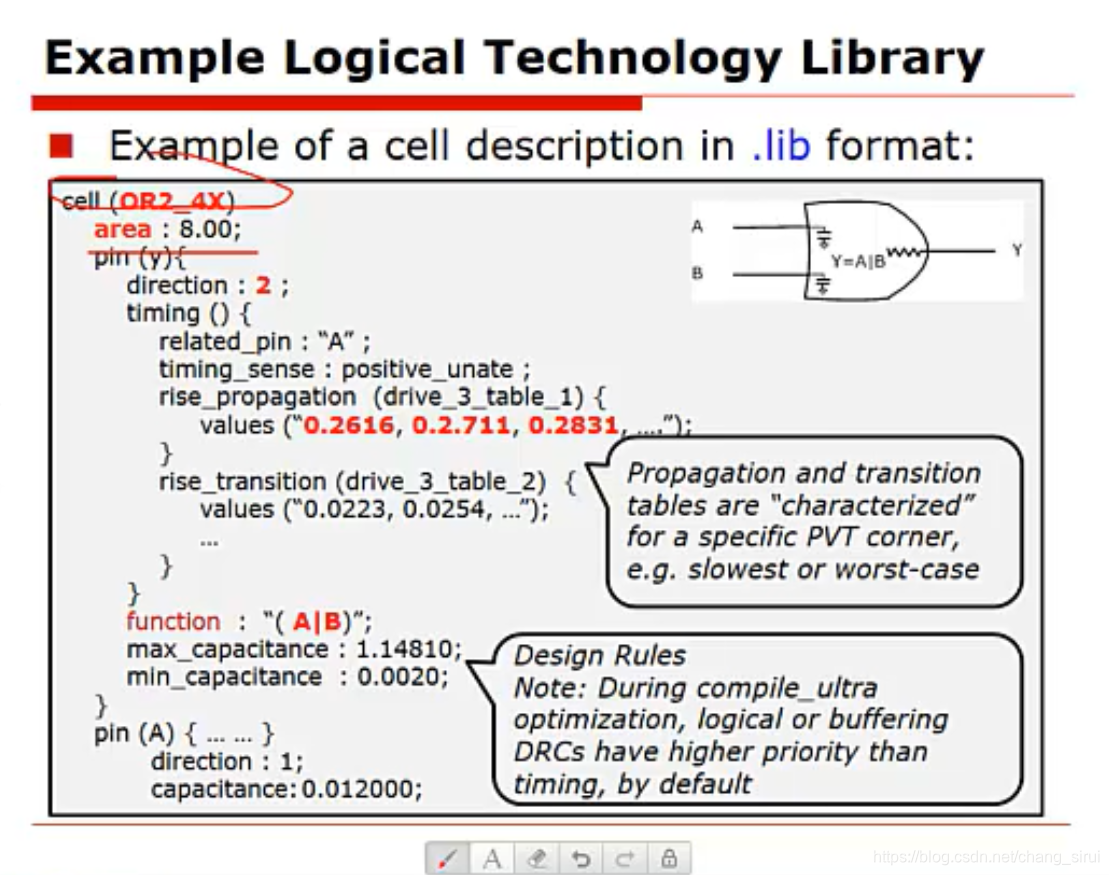

4.lib文件格式如下:

工艺库中,area的单位没有给出,要咨询厂商。

其中direction = 2 表示输出端口,direction = 1表示输入端口。具体可参见手册。

5.target library:

printvar:打印

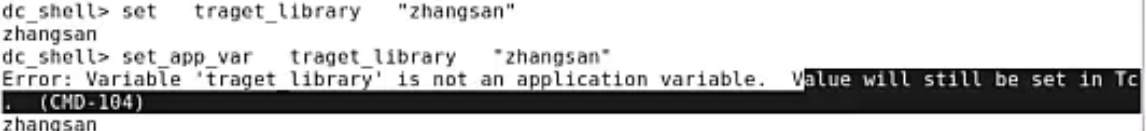

set与set_app_var:配置target library

set_app_var更安全

link library:

link library中通常是一些保密的ip核,为.db文件,没有.v形式

读入ddc文件(即同时读入.v+.db)

link后可以将结果保存为ddc文件,节省下次运行的时间。

6.结果的保存:

使用write命令,保存为verilog格式

同时会输出一个.sdf文件(时序信息)/ .ddc文件(新版dc,.ddc保存时序信息和网表信息等,ddc约等于.v+.sdc)

保存为ddc格式,用于后仿真。

7.report违规:

8.search path 设置搜索路径:

.表示在当前目录下(当前目录命令cwd)。

9.

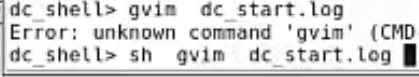

在dc_shell下无法执行linux命令,此时在前面加上sh命令就可以正常执行

set_app_var比set更安全,set在出错时不会报错。

这篇关于数字逻辑综合工具 synopsis DC学习笔记(二)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!