本文主要是介绍论文解析——AMD EPYC和Ryzen处理器系列的开创性的chiplet技术和设计,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

ISCA 2021

摘要

本文详细解释了推动AMD使用chiplet技术的挑战,产品开发的技术方案,以及如何将chiplet技术从单处理器扩展到多个产品系列。

正文

这些年在将SoC划分成多个die方面有一系列研究,MCM的概念也在不断更新,AMD吸收了chiplet架构的理论并应用到实际的设计中。

II. chiplets 驱动力

A. 计算的强大需求

B. 摩尔定律正在解体

C. 大芯片难以挽救

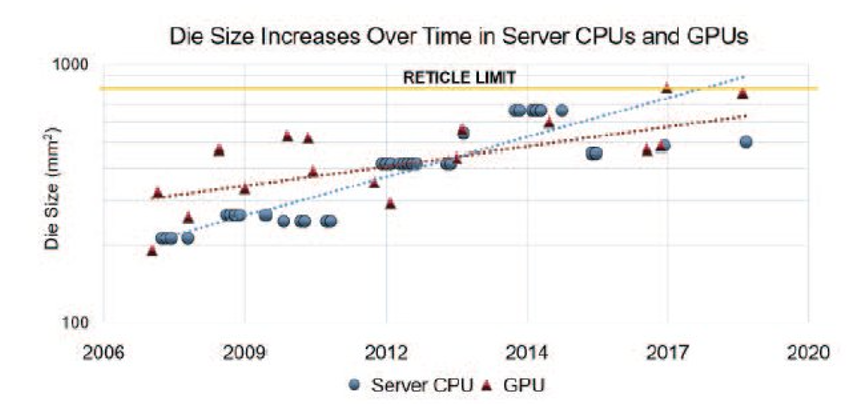

大型SoC的Die大小在不断增长,且正在逼近掩膜的极限。

D. 产品组合

一个产品系列有16、24、32核等版本,每个版本都要分别tapeout,除了流片的成本,还有硅前的物理设计、测试和debug、验证、固件、功耗和热管理优化等成本花销。

III. Chiplet将会延续摩尔定律

A. Chiplet解决方案

Chiplet解决方案是指将整块单die的SoC大芯片划分成几个小的die,在将其通过封装内互联,使之表现的类似于一个完整的SoC。

这种方式可以是很经济的,因为流片的费用和chip大小并非成线性关系。例如晶体管数量为T/2的芯片流片费用将比T个晶体管数量的芯片的一半少很多。

先进制程的良率(yield rate)相比于成熟工艺会低很多,因此对于制造小的chiplet,相比传统的大芯片,能尽早地使用先进工艺。

chiplet的另外一个优势是chiplet将不会受掩膜限制。

B. Chiplet不是免费的午餐

将Chiplet应用在SoC构建有很多潜在的优势,但也带来一些新的成本代价和复杂度。

为了较合适的将SoC划分成正确数量和种类的chiplet,每个Chiplet设计需要预先做大量的工程工作。有很多划分SoC的可能性,但不是所有的选择都满足成本要求、性能需求、IP的简化、成品硅片的复用等等。

Chiplet同样需要新的chiplet间数据传输通路。相比于片上互联的金属导线,chiplet间更长路径的互联将导致潜在的高阻抗、低带宽、高功耗和高延迟,互联开销也将包括跨电压域和时域、协议转换以及串行化/解串的电路,相比于大芯片设计,这些电路将带来额外的功耗和硅面积开销。

这篇关于论文解析——AMD EPYC和Ryzen处理器系列的开创性的chiplet技术和设计的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!