本文主要是介绍eMMC总线上电,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

目录

1 通讯线

2 上电

3 设备接口时序

4. 上电流程

a 正常上电

b 低压上电

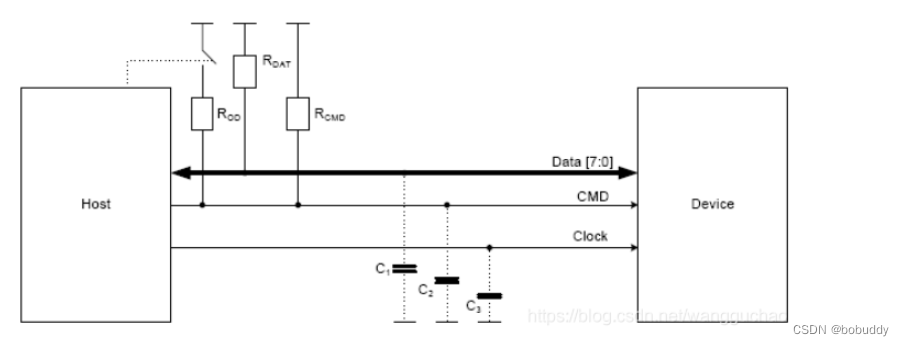

1 通讯线

e•MMC 总线有 10 条通讯线:

CMD: 命令线,双向信号。主机和设备驱动器以两种模式工作,开漏和推挽。

DAT0-7: 数据线,双向信号。主机和设备工作在推挽模式下。

CLK: 时钟,是主机发往设备的信号。 CLK 工作在推挽模式下。

2 上电

上电(包括热插入,即总线工作时插入设备)后,设备进入pre-idle状态。供电电压的上电时间应小于为总线主机电源电压规定的tPRU。

如果设备不支持引导模式,或 BOOT_PARTITION_ENABLE 位被清除,设备立即进入idle 状态。在 idle 状态下,设备忽略所有总线传输,直至接收到 CMD1。如果设备仅支持标准 v4.2 或之前版本,它上电后立即进入 idle 状态。

如果设备 BOOT_PARTITION_ENABLE 位置位,设备进入 pre-boot 状态。 然后,设备等待引导启动序列。在引导工作阶段之后,设备进入 idle 状态。在 pre-boot 状态期间,设备接收到任何 CMD1 或引导启动序列(保持 CMD 线为低至少 74 个时钟周期,或发送参数为 0xFFFFFFFA 的 CMD0)之外的 CMD 线事务,设备将进入 idle 状态。如果设备接收到引导启动序列(保持 CMD 线为低至少 74 个时钟周期,或发送参数为0xFFFFFFFA 的 CMD0),设备开始引导操作。如果引导确认被使能,设备应在规定时间内向主机发送 “010” 确认模板。在引导操作结束后,设备进入 idle 状态并准备好CMD1 操作。如果设备在 pre-idle 状态下接收到 CMD1,它开始应答命令并进入设备识别模式。

e•MMC 在 VDD 线上可呈现的最大初始负载(上电或热插入后)应为最大 10 uF 并联最小 330 ohm。在工作状态下在 VDD 线上的设备电容任何时刻都不得超过 10 uF。

在 idle 状态下, e•MMC 忽略所有总线事务直至接收到 CMD1。

CMD1 是用来协商工作电压范围,并轮询设备直至其结束上电过程的专用同步命令。除设备的工作电压状况外, CMD1 的应答还包含一个忙标志,表示设备仍工作于上电例程,没有准备好识别。此位告知主机设备没有准备好。主机必须等到此位清除。设备必须在具有有效 OCR 范围的 CMD1 发送 1 秒内完成其初始化。如果 e•MMC 设备在上一个上电周期内成功地完成了分区( EXT_CSD 字节[155]PARTITION_SETTING_COMPLETE 的 bit 0 置位)则初始化延迟(不是 1s)要通过 INI_TIMEOUT_PA(EXT_CSD 字节[124])计算。此超时仅适用于成功分区之后的第一次初始化。对于所有后续初始化,适用 1 秒的超时。

如果不执行引导操作,设备应在 1 秒内完成其从第一条有效 OCR 范围的起的初始化。

使设备退出 idle 状态是总线主机的责任。因为上电时间和电源爬升时间取决于应用参数,如总线长度和供电单元,主机必须保证电源建立起工作电平( CMD1 中规定的电平)之后再发送 CMD1。

在上电后,主机启动时钟并在 CMD 线上发送初始化序列。序列长度是以下最长者:1 ms、 74 个时钟、电源爬升时间或引导操作时间。要额外提供 10 个时钟(除设备准备好通讯后的 64 个时钟)以消除上电同步问题。

每一个总线主机都必须实现 CMD1。对所有 e•MMC 强制实现 CMD1。

3 设备接口时序

eMMC 4.51标准下的时钟速率:

sama5d2的SDMMC支持的eMMC 4.51设备时钟速率:

• Support for MMC/e.MMC Default Speed (Maximum SDCLK Frequency = 26 MHz)

• Support for MMC/e.MMC High Speed (Maximum SDCLK Frequency = 52 MHz)

• Support for e.MMC High Speed DDR (Maximum SDCLK Frequency = 52 MHz)

• Support for e.MMC HS200 (Maximum SDCLK Frequency = 120 MHz)

4. 上电流程

a 正常上电

1. 给总线加电,通讯电压范围 2.7-3.6V。

2. 设置时钟为 400KHz,或以下。

3. 等待 1ms,然后再等待 74 个时钟周期。

4. 发送 CMD0 使总线复位,在此步骤中保持 CS 线为高电平。

5. 发送 CMD1,参数为所要的电压范围, 0x00FF8000 或 0x00000080。

6. 接收 R3。

7. 如果 OCR 忙位为 ‘0’,重复步骤 5 和 6。

8. 从 R3 应答的参数,主机可以知道设备是高电压设备还是双电压设备。如果参数是0x80FF8000 则设置是仅高电压的,如果参数是 0x80FF8080 则设备是双电压。

9. 如果 R3 返回某一其它值,则设备不兼容(因为它由于电压不兼容而将自己置于 inactive状态,无应答)。在此要求况下,主机必须使总线下电,并开始错误恢复例程。

b 低压上电

如果主机支持低压上电,执行以下步骤;否则跳到identify mode//。

10. 如果主机是低压主机,且识别到双电压设备,使 MMC 总线下电。

11. 以低电压范围( 1.70 -1.95V)给总线上电。

12. 等待 1ms,然后再等待 74 个时钟周期。

13. 发送参数为 0x00000080 的 CMD1。

14. 接收 R3,它应为 0x00FF8080。

15. 如果 OCR 忙位为 ‘0’,重复步骤 13 和 14。

————————————————

这篇关于eMMC总线上电的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!