本文主要是介绍8086cpu计算机开机时如何工作的,8086的时序-微计算机原理-电子发烧友网站,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

§第六节 8086的时序

计算机在软件的控制下,可以完成计算、图形/图像、声音、通讯、控制工厂生产设备、通讯等复杂工作,这些工作都是由CPU的几种基本操作构成的。CPU的基本操作有:

存储器读、I/O接口读、CPU内部运算、存储器写、I/O接口写、中断、空操作、复位。

本节只关心CPU从存储器、I/O接口获得运算数据,或把运算结果写入存储器、I/O端口的操作,以及中断、空操作、复位操作,特别是进行这些操作时CPU各信号之间的协调关系,即"时序"。

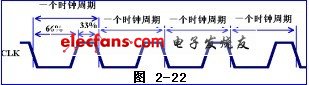

计算机的基本操作均是以时钟信号CLK为基准信号进行协调工作的。8086的时钟频率为5 ,故其时钟周期(或称一个T状态)为200ns,时钟信号输入时序如图2-22所示。

执行一条指令所需要的时间,称为一个指令周期。一条指令一般包含几个基本操作,存储器读、存储器写、I/O接口读写、中断、复位等操作均与总线有关(各部件均连接至总线上),称为"总线操作"(或称"总线通讯")。一次总线操作所需的时间称为"总线周期"或"机器周期"。

8086的基本总线周期由4个T状态组成T1、T2、 T3、T4如图2-23所示。

T1:CPU发出地址信息,指出要访问的存储器/外设端口地址。

T2:CPU撤消地址信号,准备传输数据。

T3:CPU的总线借口部件(BIU)与存储器/外设端口传输数据。

T4:传输数据并结束总线周期。

TW:等待状态,在T3状态时,若存储器/外设端口未准备好(接收或输出)数据,CPU在T3后插入TW。

Ti:空闲周期,只有在CPU与存储器/外设端口传送数据时,CPU的BIU才执行总线周期,否则,BIU执行空闲周期Ti.

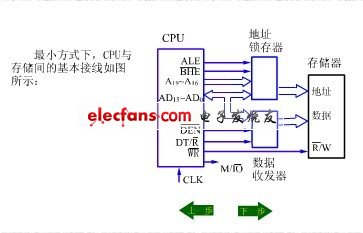

§2.6.1存储器读周期

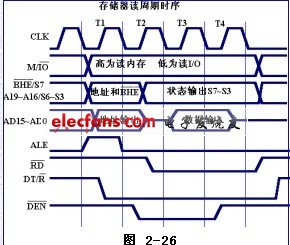

一个基本的存储器读周期由4个T状态组成,如图所示:

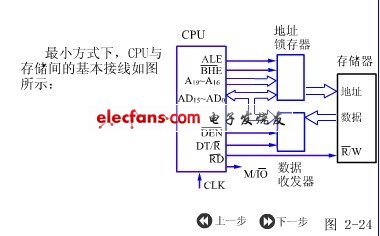

存储器读涉及的信号有:

① 用 M/IO信号确定CPU是与存储器或外设通讯。M/IO=1,CPU与存储器通讯。该信号在T1状态开始有效。

② 指出存储器单元的地址。CPU在T1状态从分时复用信号线A19/S6~A16/S3、AD15~AD0上发出20位地址信号A19~A0.在T1状态,PU还要发出地址锁存信号ALE。在ALE下降沿,地址信号被锁存在地址锁存器8282中。这样,在其它T状态,分时复用信号线A19/S6~A16/S3、AD15~AD0就可以用来传送状态和数据信号了。

③ CPU在T2状态发出读命令RD(此时WR信号无效)。另外,从T2状态开始,A19/S6~A16/S3信号线上发出状态信号。在T2状态,AD15~AD0上的地址已消失、数据还未到达,因此,处于悬空状态。

④ 存储器收到地址信号、读命令后,经过一定时间,在T3状态,把指定存储单元的数据送到数据总线上,CPU在T3的后下降沿从AD15~AD0上获得该数据。

⑤ CPU获得数据后,在T4状态,CPU撤消本次操作的信号。本次操作完成。

⑥ CPU与数据总线一般通过数据收发器8286连接,因此,CPU还要发出控制8286的信号DT/R、DEN。控制8286的数据传送方向在存储器读周期中,DT/R=0,表示数据进入CPU(接收)。DT/R使8286允许传送数据。DT/R从T1状态开始在整个周期中一直有效。DT/R从T2状态开始有效。

具有等待状态的读周期时序:

若所使用的存储器或外设的工作速度较慢,CPU在T2结尾、T3开始处未检测到READY信号,则在T3后插入一个或几个TW状态,并在每个插入的TW前沿,均检测READY,当检测到READY=1时,不再插入TW,并在最后一个TW 的后下降沿从总线上读取 数据。然后,CPU进入TW状态,T4结束本操作周期。

§2.6.2 存储器写周期

它也是由4个状态组成,如图所示。它与存储器的读周期类似,首先也要有M/IO信号来表示进行存储器操作。若M/IO=1则与存储器通信。其次也要有写入单元的地址以及ALE信号,但写入存储器的数据不同。在T2状态,即当16位地址线AD15~AD0已由ALE锁存时后,CPU就把要写入的16位数据放至AD15~AD0上了。要写入,当然要又WR信号代替RD信号,它也在T2状态有效。DT/R信号应为高电平。8086在T4状态后就使控制信号变为效。实际上8086是认为在T4状态,对存储器的写入过程已经完成。若有的存储器和外设来不及在指定的时间内完成操作,可以利用READY信号,使CPU插入TW状态,以保证时间配合,具有TW的写入时序与读时序类似。

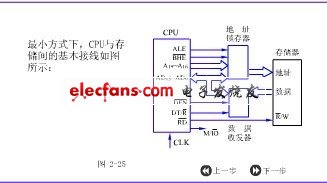

CPU写存储器涉及的信号有:

① 用M/IO 信号确定CPU是与存储器或外设通讯。在整个写周期中,M/IO =1,表示CPU与存储器通讯。

② 指出存储器单元的地址。由于8086CPU的地址信号和数据信号复用一组引脚,CPU只能分时传送地址信号和数据信号。CPU在T1 状态从分时复用信号线AD19/S6~AD16/S3 、 AD15~AD0 上发出20位地址信号A19~A0 。

③ 为了保持住地址信号,需要使用地址锁存器8282。在T1状态,CPU还要发出地址锁存信号ALE,在ALE下降沿,地址信号被锁存在地址锁存器8282中。这样,在其它T状态,分时复用信号线 AD19/S6 ~AD16/S3 、 AD15~AD0 就可以用来传送状态和数据信号了。

④ CPU在T2状态发出写命令WR(此时RD信号无效)。另外,从T2状态开始,AD19/S6 ~AD16/S3 信号线上发出状态信号。在T2状态,AD15~AD0上的地址已消失,在数据还未到达前处于悬空状态。

⑤ 存储器收到地址信号、写命令后,经过一定时间,把指定存储单元的数据送到数据总线上。如果存储器的写入速度较快,在T2状态结束时(下降沿),就可以写入数据,使CPU在T3的后下降沿从AD15~AD0上获得该数据。

⑥ CPU获得数据后,在T4状态,CPU撤消本次操作的信号。本次操作完成。

⑦ CPU与数据总线一般通过数据收发器8286连接,因此,CPU还要发出控制8286的信号DT/R、 DEN 。DT/R控制8286的数据传送方向,在存储器写周期中,DT/R=1,表示数据离开CPU(写入)。DEN使8286允许传送数据。DT/R从T1状态开始在整个周期中一直有效。DEN从T2状态开始有效。

§2.6.3 输入输出周期时序

输入周期,CPU从I/O接口电路读取外设的数据和外设状态;输出周期,CPU把数据或命令送到外设的I/O接口电路中。它们的操作时序与存储器操作时序几乎相同,只是M/IO=0。

§2.6.4 空转周期(Idle Cycle,空闲周期)

CPU总线接口部件BIU从存储器取指令时,执行存储器读周期。CPU需要存储器中的数据时,也执行存储器读周期。(取指令时S2S1S0=100,读数据时S2S1S0=101)。CPU把数据写入存储器时执行存储器写周期。CPU与外设通讯时执行输入或输出周期。CPU响应外设的中断请求时,执行中断响应周期。

如果CPU不执行上述任何周期,则总线接口执行空转周期。空转周期由一系列Ti状态(Idle)构成。在Ti状态,A19/S6~A16/S3线 上为上一个总线周期的状态信息。若上一个总线周期是写周期,在Ti状态,AD15~AD0线上仍为原数据信号。若上一个机器周期是写周期,则在空转状态,CPU在AD15~AD0上仍然输出上一个机器周期要写的数据,直至下一个机器周期的开始。

§2.6.5 中断响应周期

"中断(Interrupt)"是一种操作,它使CPU中止正在执行的程序,而转入称为"中断处理程序(Interrupt Handler)"(或称中断服务程序Interrupt Service,或称中断例程Interrupt Routine)的程序。当中断处理程序执行完后,CPU接着执行被中断的程序(相对于中断处理程序来说,被中断的程序称为主程序)如2-28所示。

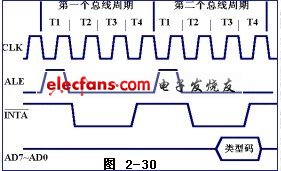

多个外部设备一般通过"中断控制器"8259向CPU提出中断请求,8259也向CPU提供"中断类型码",以标识是那一个外部设备在向CPU请求中断。CPU用中断响应信号 通知8259。在中断响应信号INTA的第二个周期,8259向CPU提供中断类型码。

8086CPU有两个引脚可以接收外部的中断请求:INTR和NMI,如图2-29所示。

当NMI(非屏蔽中断请求)引脚上出现上升沿信号时,CPU立即无条件(不执行中断响应周期,不受标志寄存器IF位的影响)地转入"2号中断处理程序"。

当INTR(可屏蔽中断请求)引脚上出现高电平信号时,若IF=0,CPU不响应中断请求。若IF=1,CPU响应中断请求。CPU响应中断时,首先执行"中断响应周期",以便从中断控制器8259获得中断类型码,然后根据中断类型码转入相应的中断处理程序,当中断处理程序执行完后,CPU返回被中断的程序。中断类型码指定了中断处理程序的地址。

中断响应周期由两个总线周期构成,在每个中断响应的总线周期, 均有效(为低电平)。在第二个总线周期,中断控制器送出中类型码,CPU读的类型码后,从"中断矢量表"中查得中断处理程序的地址,如图2-30所示。

§2.6.6 系统复位(RESET)

8086CPU的RESET引脚上出现高电平时,终止所有操作,直到RESET信号变为低。在这期间,CPU内各寄存器被初始化为复位状态,见表2-9所示。

表2-9 8086复位期间的内部状态

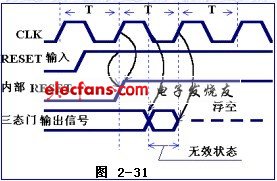

对于复位信号的要求是:它必须与系统时钟CLK同步(由时钟电路8284来实现),至少维持4个时钟周期。若是直接接通电源引起的复位,复位信号必须至少大于50微秒。

在复位期间,所有三态引脚,先被置为无效状态(如RD=1为无效),然后被置为浮空状态。其他(非三态)引脚被置为无效状态(如ALE=0为无效状态)如图2-31所示。

AD15~AD0,A19/S6~A16/S3,BHE/S7,S2(M/IO),S1(DT/R),S0(DEN),CLOCK(WR),RD,INTA先置成无效状态,再进入三态(浮空)。不作用状态占进入三态的半个时钟周期。

ALE:低

HOLD:低

RQ/GT0,RQ/GT1:高

QS0,QS1:低

在复位期间,由于CS=FFFFH,IP=0000H,因此,当CPU脱离复位状态后,从CS:IP = FFFFH:0000H = FFFF0H处开始执行第一条指令。物理地址FFFF0H对应的实际存储器单元在微机主板的BIOS芯片内。

BIOS芯片内存放以下信息:

① 系统初始化程序。

它检测微机系统的基本部件是否完好,并对基本部件进行第一步初始化,使其做好基本的工作准备。(操作系统,如DOS、Windows可能对这些部件进行第二步初始化,以便优化这些部件的性能)。

② 系统设置程序。

它允许用户配置计算机的参数和性能,如磁盘参数、存储器参数、键盘参数、启动顺序等。

③ 系统信息,如配置信息、日期、时间信息等。

BIOS中的系统信息存放在由电池供电的CMOS电路中(配置系统信息又称为"CMOS设置"),即使关闭计算机电源,这些信息也不会丢失。

(在某些BIOS芯片内部,已经包含了电池,因此,主板上看不见电池)。

系统初始化程序和系统设置程序放在BIOS的EPROM存储器区,具有"非易失性",即使关闭计算机电源,这些程序也不会丢失。现代BIOS一般由Flash EPROM构成,这种存储器除有非易失性外,在特定的程序控制下,还可改写其中的信息。这为BIOS的升级提供了有利条件。同时,也向"病毒"敞开了大门,首例攻击BIOS的病毒是"CIH"(1998年)。

这篇关于8086cpu计算机开机时如何工作的,8086的时序-微计算机原理-电子发烧友网站的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!