本文主要是介绍可测试性设计原理:Wrapping Core (Ⅱ),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

Wrapping core

本文主要讲述了The Simple Core Wrapping Flow的基本原理,区别于The Maximized Reuse Core Wrapping Flow实现更为简单,但会引入更大的timing和area的影响。参考(翻译)自《Synopsys® TestMAX™ DFT User Guide》,FYI。

The Simple Core Wrapping Flow

简易的core wrapper flow提供了基本的core wrapper functionality。

Simple Core Wrapper Cell

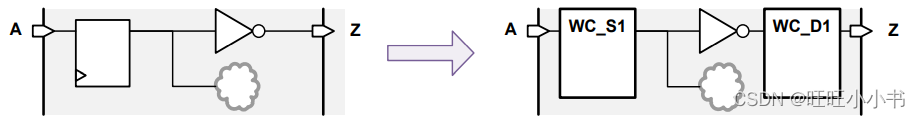

- Dedicated Wrapper Cell

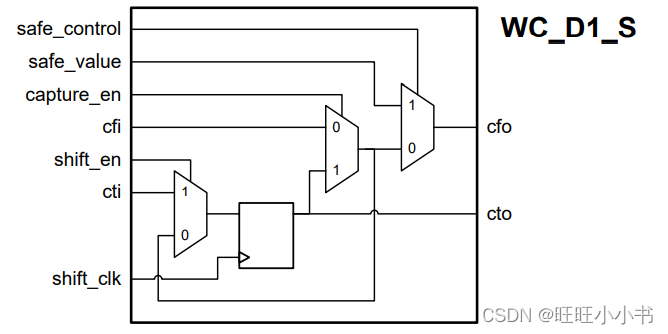

默认情况下该flow使用的是WC_D1专用wrapper cell进行core wrapping,由内部的专用flip-flop提供可控制性和可观测性以及移位功能。

- cti - Core test input

wrapper cell 的test input端,它可以来自PI或者上一个wrapper cell 的cto; - cto - Core test output

wrapper cell 的test output端,它可以驱动PO或者下一个wrapper cell 的cti; - cfi - Core functional input

对于input wrapper cells,输入来自于围绕core的周边逻辑;对于output wrapper cells,输入来自于core; - cfo - Core functional output

对于input wrapper cells,输出驱动core;对于output wrapper cells, 输出驱动core周边逻辑; - shift_clk - Wrapper clock

由核内部的wrp_clock驱动,clock wrapper cell内部的flip-flop; - shift_en - Shift enable

wrapper cell的scan-enable信号,当该信号为高电平时,wrapper cell shift cti和cto;当该信号为低电平时,wrapper cell capture function input value或者保持当前状态,取决于此时capture_en的值 ,该信号对于input 和output wrapper cell有不同的控制; - capture_en

该信号控制wrapper cell何时进行capture,当该信号为低电平时,wrapper clock capture functional输入值,当该信号为高电平时,wrapper cell保持当前状态;

- cti - Core test input

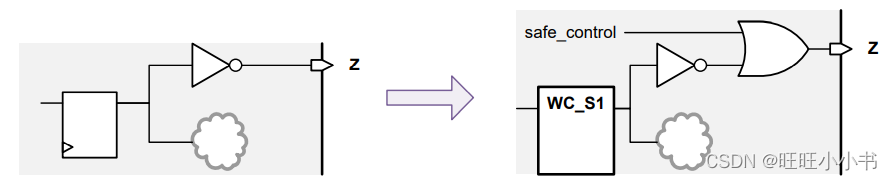

- Dedicated Safe-State Wrapper Cell

该类型的wrapper cell在输入端提供可观测性,在输出端提供可控制性,core input和core output都使用WC_D1 wrapper cell,但是可控制的wrapper cell输出端可以作为数据toggle shift进wrapper chain,在某些情况下,如果边沿触发或者电平敏感逻辑存在于wrapper cell的fanout,可能需要额外的操作。

为了避免这种情况,可以为wrapper cell spec一个safe value。DFTC通过使用WC_D1_S wrapper cell来实现存储safe value的功能。它在输出端增加了一个额外的mux来驱动safe value通过一个额外的控制信号来使能。

WC_D1_S与WC_D1 interface大致相同,增添了以下额外信号:

safe_control - Control signal

这个信号决定何时输出safe value;

safe_value - Logic value

这个信号定义了safe state logic value; - Shared-Register Wrapper Cells

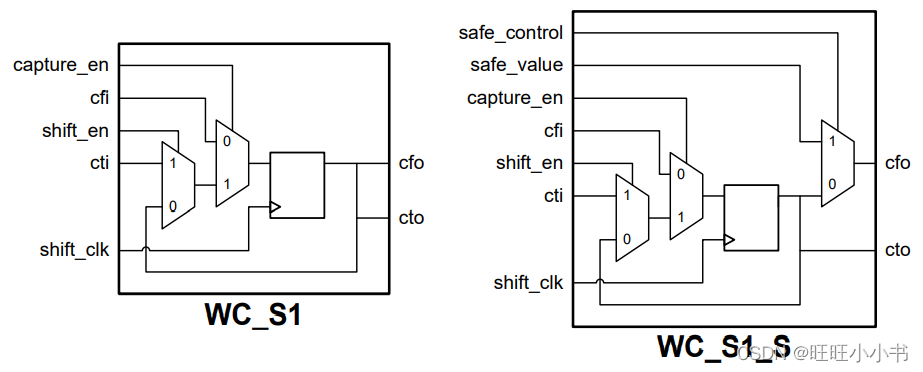

如果design中有与port相连的boundary I/O register,可以复用这些function register作为wrapper cell logic去减少面积开销。使用Shared wrapper cell来代替存在的function register在function mode下提供等价的功能。

为了core wrapping 的特性能共享到function register,I/O register和port必须满足以下情况: - 这个register的data input或者output必须通过wire或logic path的方式连接在boundary port上,这条logic path必须可以敏化以产生buffer或invert的效果并且必须由恒定信号类型控制(静态值为0或1)主要输入输出。

- 共享的register必须是function clock控制。

如果I/O register 的clock与core clock是同一个,并且在wrapper chain操作的时候会影响到core logic就需要分离function clock给 shared wrapper cell或者使用 -use_dedicated_wrapper_clock选项。

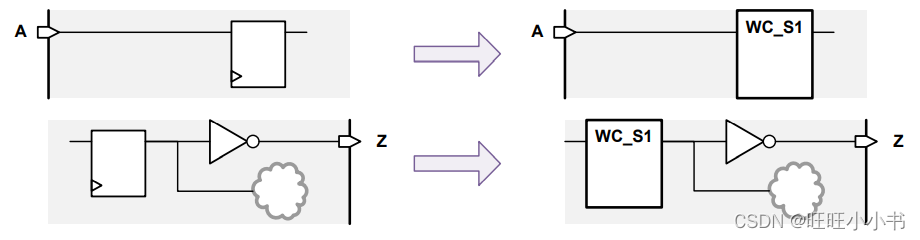

当启用shared wrapper cell style时,DFTC将尽可能地插入shared wrapper cell,比如

但是如果register不满足要求,就只能插入dedicated wrapper cell,比如

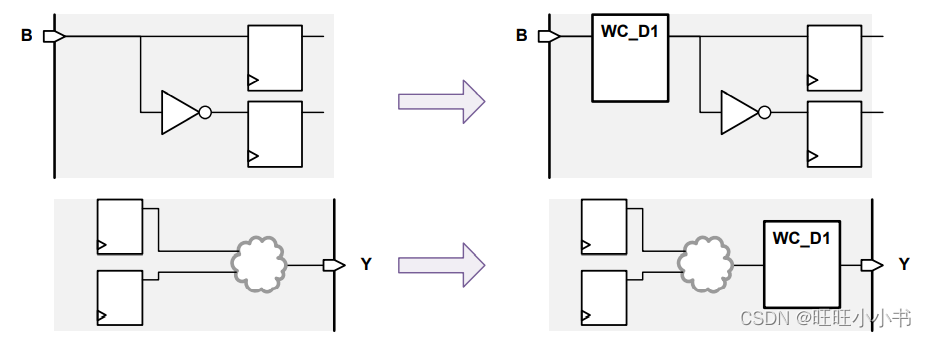

如果一个寄存器既是输入共享寄存器又是输出共享寄存器,那么该寄存器就成为输入共享寄存器,并且在输出端口放置一个dedicated wrapper cell,比如

如果一个输出shared register被定义了一个safe state通常使用WC_S1_S wrapper cell。但是如果除了输出port之外寄存器的输出还驱动了内部的logic那么WC_S1_S里的safe state logic会阻止寄存器驱动内部logic,所以当DFTC检测到这种情况时会使用WC_S1来代替WC_S1_S并将safe state logic移到output port。

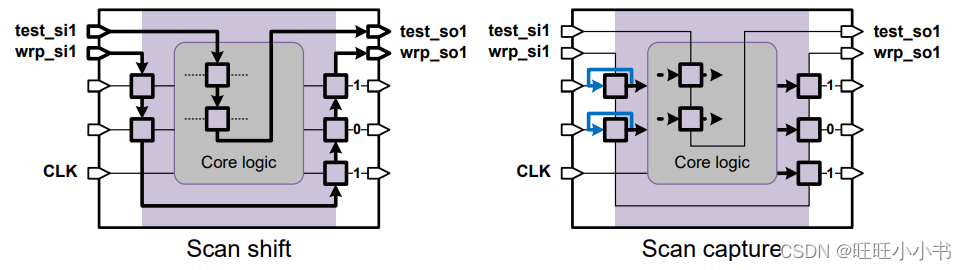

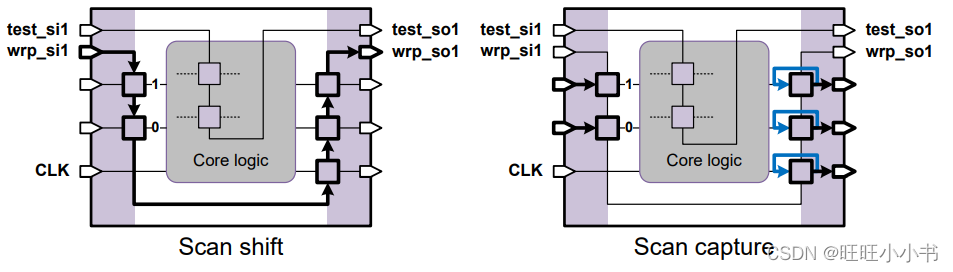

Simple Core Wrapper Chains

在simple core wrapping flow里输入和输出wrapper cell可以被放在一条wrapper chain。设计中可以有一条或多条wrapper chain。

上图为inward-facing操作下wrapper chain的shift和capture行为,在capture阶段wrapper cell会通过循环一直保持同一个值来block住外部输入。

上图为outward-facing操作下wrapper cell的shift和capture行为。

这篇关于可测试性设计原理:Wrapping Core (Ⅱ)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!