本文主要是介绍PS通过GTX实现SFP网络通信1,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

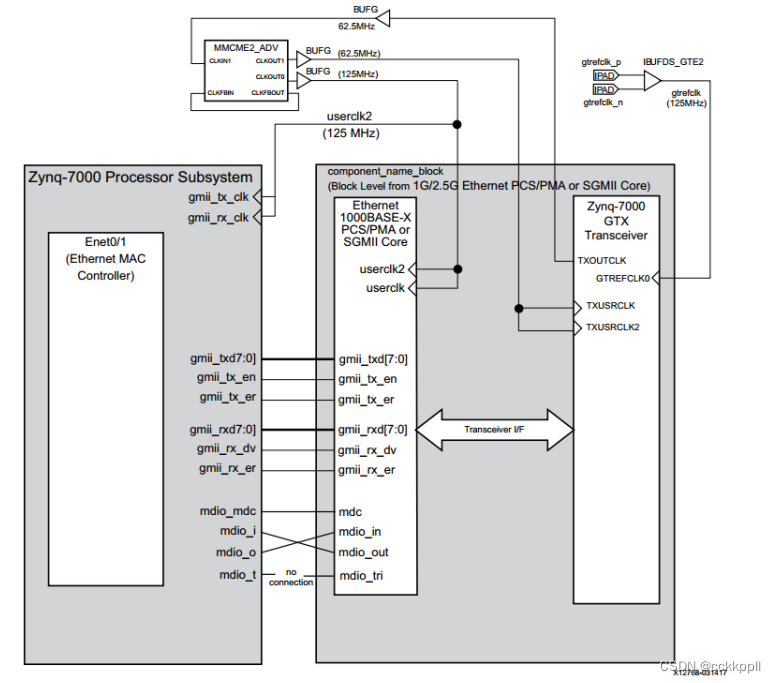

将 PS ENET1 的 GMII 接口和 MDIO 接口 通过 EMIO 方 式引出。在 PL 端将引出的 GMII

接口和 MDIO 接口与 IP 核 1G/2.5G Ethernet PCS/PMA or SGMII 连接, 1G/2.5G Ethernet PCS/PMA or SGMII 通过高速串行收发器 GTX 与 MIZ7035/7100 开发板的 SFP 接口连接。在 PS 端通过 SDK 自带的 lwip echo server 例程实现与电脑的 TCP 通信。

PL 部分设计

ZYNQ PS 设置

要实现本例程的功能,在原有基础上 PS 需要添加 2 个设置。首先,将 ENET1 及其 MDIO 接口以 EMIO 方式引出,如下图所示。

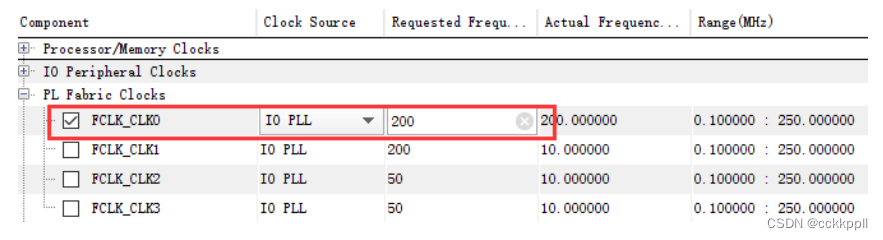

设置 PS 输出 1 路 200MHz 的时钟,用于给 1G/2.5G Ethernet PCS/PMA or SGMII IP 核提供参考时钟。 例如,使用 FCLK_CLK0 输出 200M 时钟,如下图所示。

1G/2.5G Ethernet PCS/PMA or SGMII IP 核设置

将 IP 核设置为 PS 的以太网控制器。

选择 1000BASEX 模式,如下图。

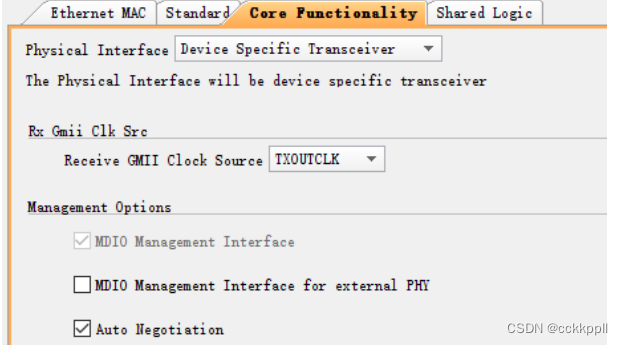

使用 GTX 收发器作为 SFP 的接口,输入 IP 核内部的 MMCM 的时钟源选择为 GTX 收发器输出

的时钟 TXOUTCLK ,该 MMCM 将产生我们所需要的用户接口时钟。 MDIO 接口默认启用。使能自协商。如 下图。

当设计中只包含 1 个此 IP 核时,应当将可共享的逻辑资源和硬件模块包含在 IP 核内部,这样会减少

所生成的模块数量,简化设计。如下图所示。

当设计中需要同时使用若干个此 IP 核,且所使用的 GTX 均位于同一个 GTX BANK 中。此时,只需其中 1 个 IP 核内部的共享资源( MMCM 、 GTP PLL 、 GTX 参考时钟等)便可以满足所有 IP 核的需求,即选择将共享 资源包含在 IP 核内部。其余 IP 核将这些共享资源从其内部剔除即可,即选择将共享资源包含在 example 中。

IP 核结构

时钟网络

IP 核内部时钟网络结构如下图所示。

用户接口

这里对一些重要的用户接口进行说明,其他接口可参考 IP 核手册。

GMII 接口

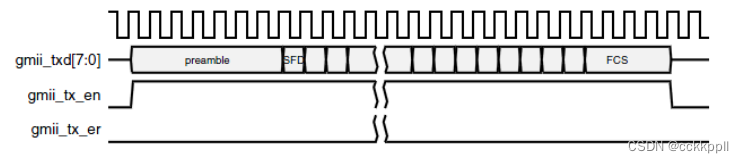

GMII 接口的同步时钟为 IP 核的输出时钟 userclk2 。 GMII 接口发送时序如下图所示。

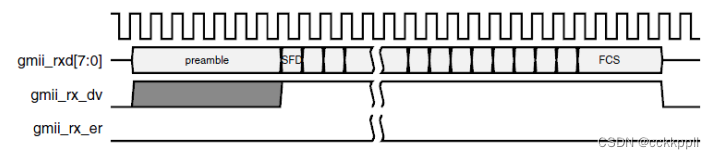

GMII 接口接收时序如下图所示。

independent_clock_bufg

independent_clock_bufg 是频率为 200MHz 的输入时钟。在 IP 核的 example design 中, GMII 接口连接了 IDELAYE2,并作为 IO 与芯片引脚连接。 independent_clock_bufg 输入的 200MHz 时钟便作为 IDELAYCTRL 的 参考时钟。在本例程中,GMII 作为内部信号,不用作 IO 口,所以不需要使用 IDELAYCTRL 。 除此之外,independent_clock_bufg 还供 IP 核内部的其他逻辑使用。因此,无论是否需要使用 IDELAYCTRL,independent_clock_bufg 都必须输入 200MHz 的时钟。后缀 bufg 表示该 200MHz 时钟进入 independent_clock_bufg端口前就已经通过 BUFG 进入了全局时钟网络。在例程中,这个 200MHz 时钟直接由 PS 输出的 FCLK_CLK0 提供。

signal_detect

要使 IP 核正常工作,需要将 signal_detect 置 1 。例程中,通过 IP 核 Constant 将 signal_detect 置 1 。 Constant 设置如下图所示。

Configuration_Vector

Configuration_Vector 用于配置 IP 核的基本工作模式,可替代 MDIO 接口的功能。其具体含义如下图所示。

由于例程中启用了 MDIO 接口,因此 Configuration_Vector 无实际使用。例程中,通过 IP 核 Constant 将输入 的 Configuration_valid 置为 0 ,则使 Configuration_Vector 无效。 Constant 设置如下图所示。

an_adv_config_vector

an_adv_config_vector 用于配置 IP 核的自协商功能,其具体含义如下图所示。对于 1000BASEX 模式,只需要关注 bit5,bit8~7,bit13~12。IP 核的自协商功能可以通过 MDIO 接口进行配置,由于例程中启用了 MDIO 接口,因此 an_adv_config_vector 无实际作用。例程中,通过 IP 核 Constant 将输入的 an_adv_config_val 置为 0,则使输入 an_adv_config_vector 无效。

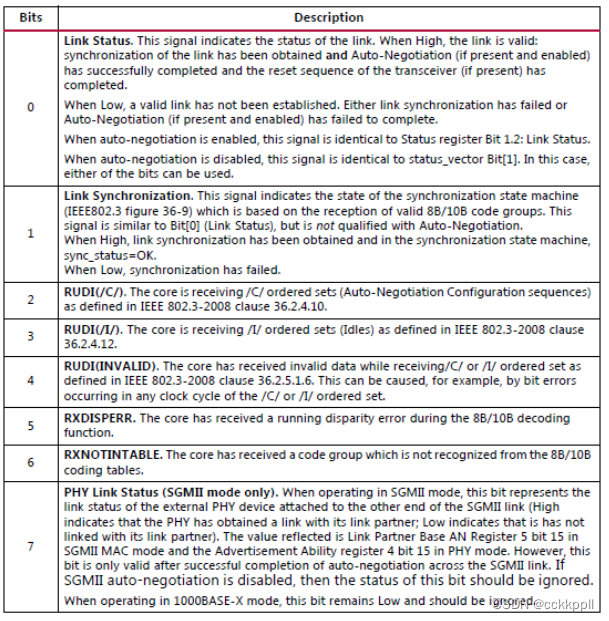

Status_Vector

Status_Vector 反应了 IP 核工作状态,其具体含义如下图所示。

phyaddr

例程中启用了 MDIO 接口,由于 MDIO 接口时基于地址进行访问的,因此需要为 IP 核设置 1 个 phy address 。 在例程中,通过 IP 核 Constant 将 phy address 设置为 6 。

将 PS ENET1 与 1G/2.5G Ethernet PCS/PMA or SGMII 连接

这篇关于PS通过GTX实现SFP网络通信1的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!