本文主要是介绍(南京观海微电子)——液晶画面Crosstalk的原理与本质分析,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

一、H-Crosstalk (与EE开发相关)

1.画面轻重载切换交界处有水平弱线或Block

– Power IC 相关

– Root cause:AVDD drop 后恢复过慢

– Solution : Power IC 补偿调整优化

范例:AVDD在重载区Drop明显,且恢复较慢导致的Hcrosstalk;

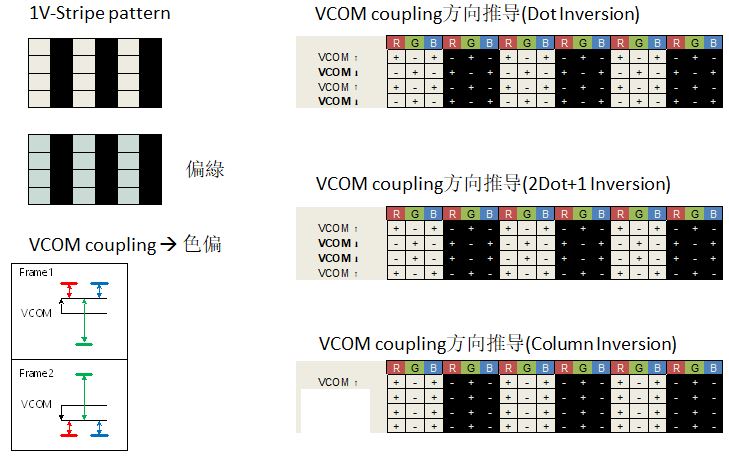

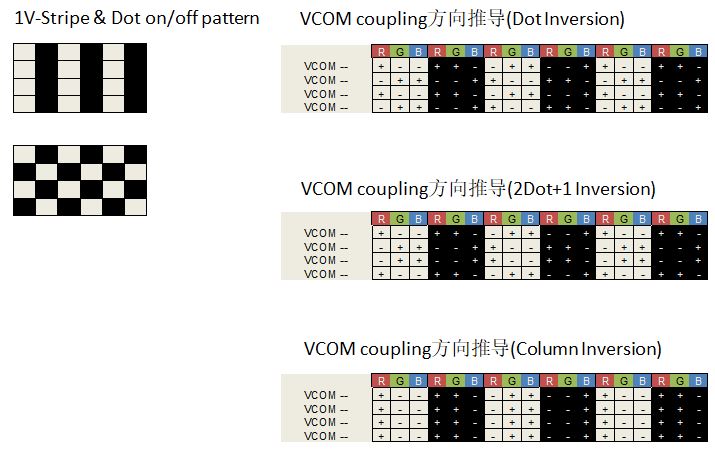

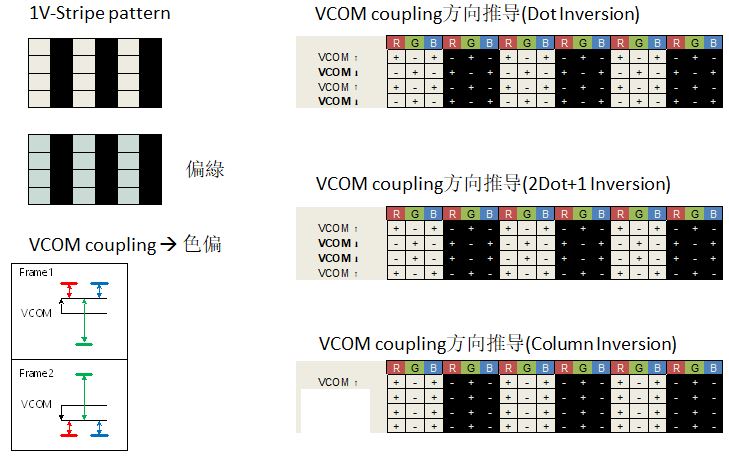

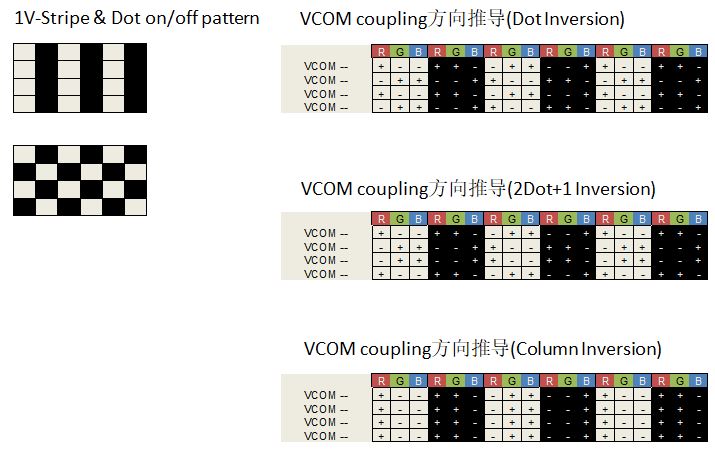

Result:当采用 H1dot 驱动 改为 H2dot or 1+H2dot驱动,Greenish现象消失

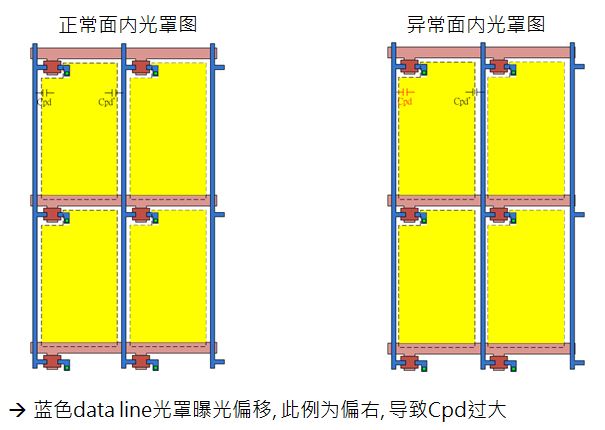

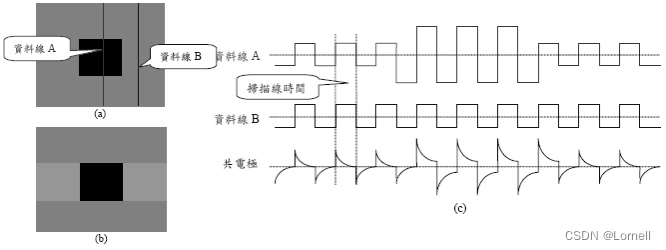

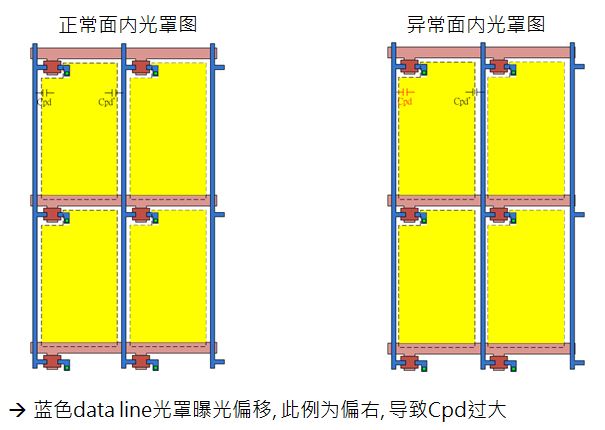

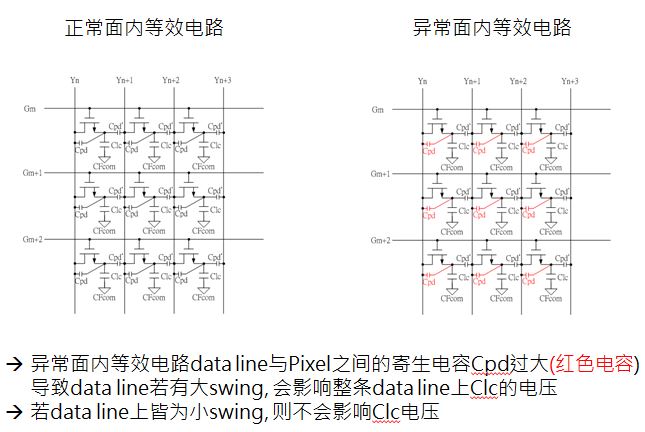

二、V-Crosstalk (与Mask对位相关)

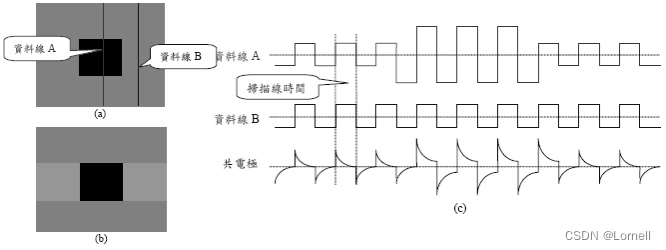

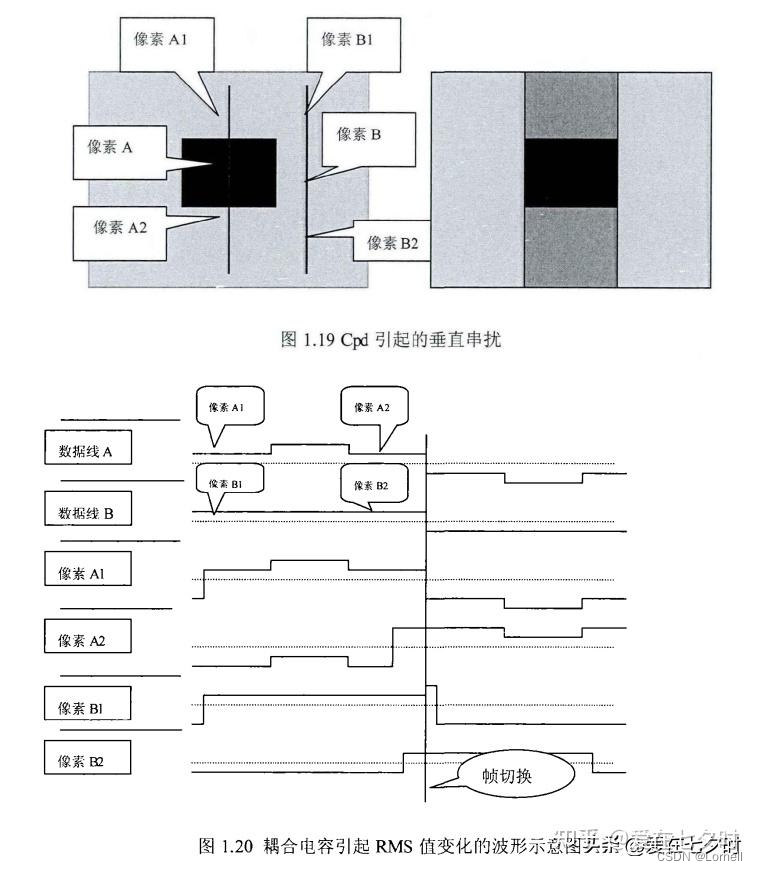

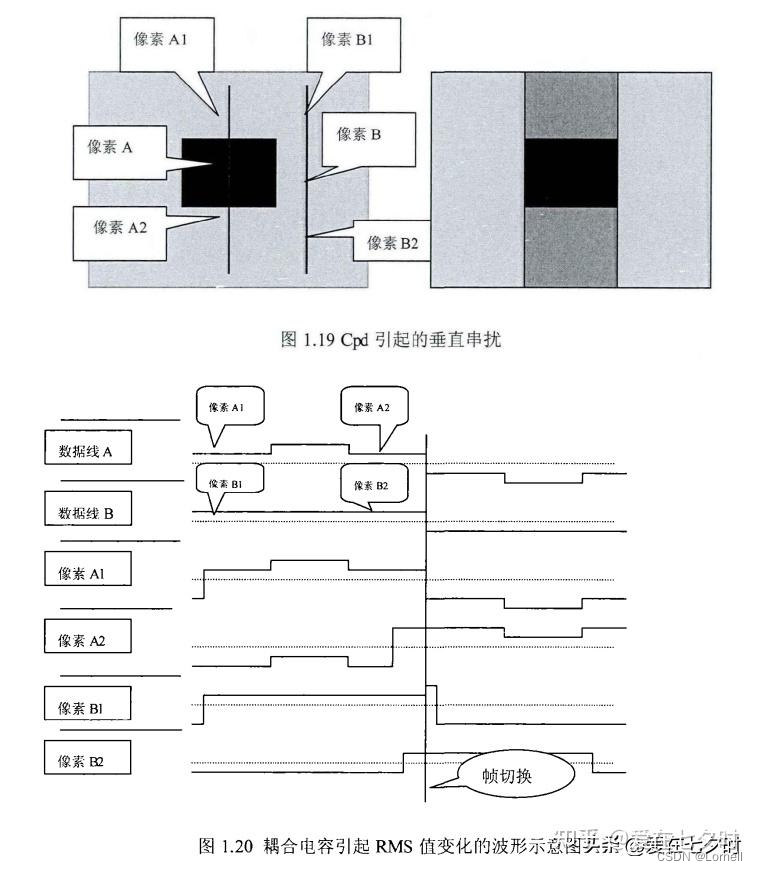

– Root cause : Mask光罩曝光对位偏移, 造成Cpd大小不一;

– Solution : 调整Mask光罩对位

下图为data line对位偏移状况 & root cause

图框反转(Frame Inversion)对垂直crosstalk的影响

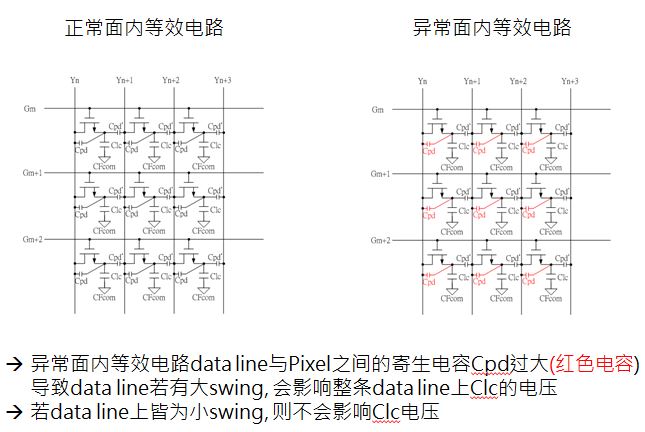

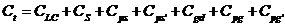

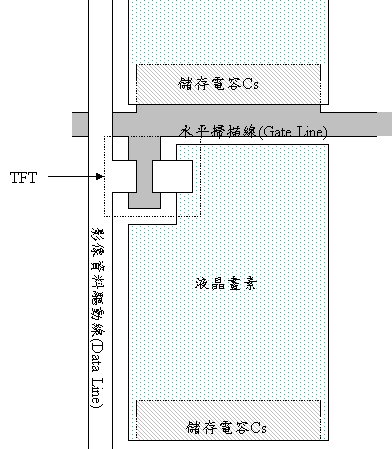

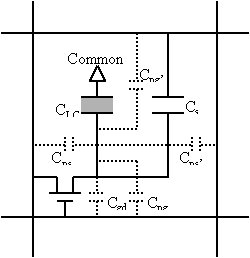

由于液晶必须以交流方式驱动,以避免液晶电容内有残馀的直流电压成份,造成液晶分子的电化学反应。交流驱动的方式有图框反转(Frame Inversion)、线反转(Row Inversion、Line Inversion)、行反转(Column Inversion)、及点反转(Dot Inversion)。以下即针对不同的交流驱动方式所产生的垂直串音现象分别作讨论。首先参考图一的液晶画素等效电路,一个液晶画素的等效电容值Ct如(1)式,是所有的杂散电容、储存电容、及液晶电容的总和。液晶画素经由Cps与Cps’的电容藕合效应,可以用藕合参数(Coupling Parameter)α、β来表示,如(2)(3)式:

(1)

(2)

(3)

图1. TFT LCDs 的画素矩阵佈局与液晶画素的等效电路

在同一条水平扫描线上,跨于液晶画素电容两端的画素电压可用(4)式描述,随扫描时间不同,液晶画素被其他扫描时间的影像资料讯号(Vj)影响,所以液晶画素的有效电压为在整个图框扫描的均方根电压(RMS)。

(4)

对于讯号电压的极性定义以共通电极(Common)的电压位准为参考依据,若是讯号的电压位准低于共通电极的电压位准,此时讯号电压Vj(t)即为负极性,若是高于共通电极的电压位准,即为正极性的影像讯号,同理Vi的定义也是以共通电极的电压位准为参考。参考(4)式,若Vi是正极性而Vj(t)为负极性,(4)是可改写成如(5)式:

(5)

(5)式中Vi,Vj都是取正数。

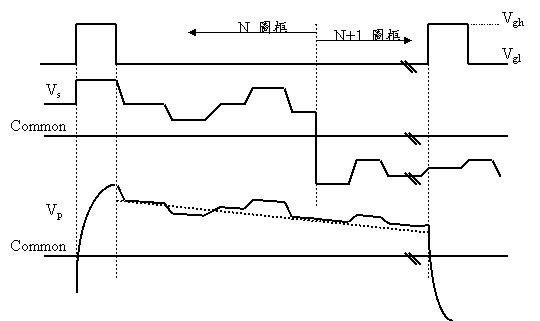

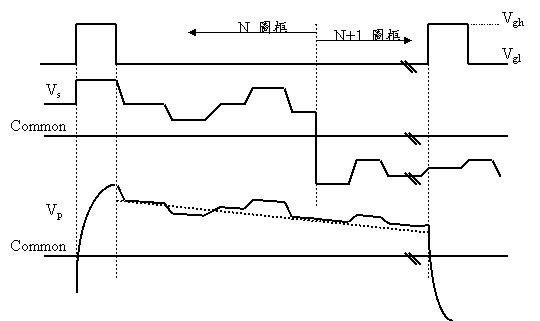

图2. 採用图框反转交流驱动时,TFT LCDs的驱动波形与液晶画素电压波形。Vgh与Vgl分别为水平扫描脉波开启与关闭TFT的电压位阶,Vs为垂直讯号线上的驱动波形,Vp为液晶画素内的电压波形。

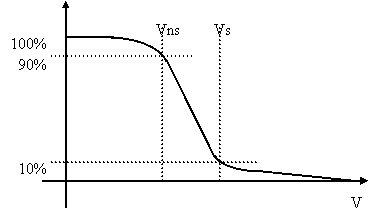

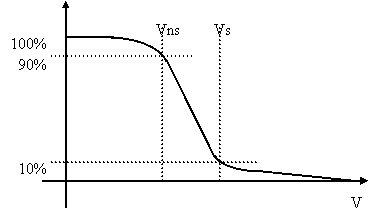

图3. 液晶的电光特性曲线

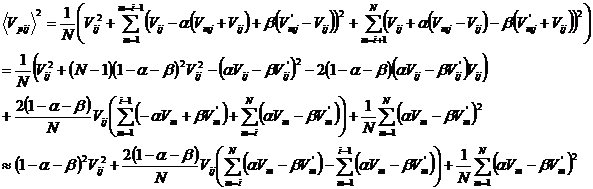

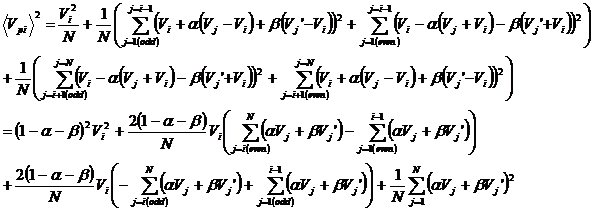

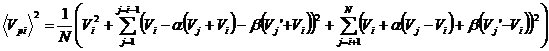

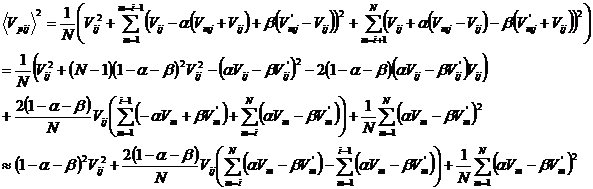

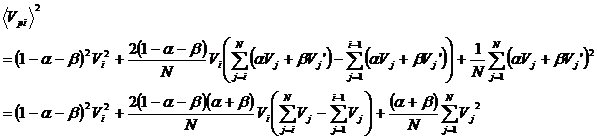

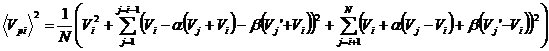

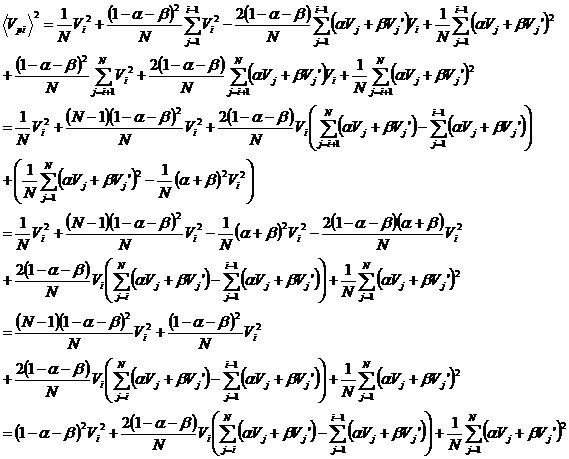

若是採用图框反转的极性交换方式,第i列(Row)的液晶画素的有效电压值,是整个画面完成扫描的週期时间内的电压均方根(RMS)值。假设第i列水平扫描线被选取驱动时,对应的垂直影像电压为Vi;同理,当其他水平扫描线被选取驱动时,对应的垂直影像电压为Vj(1 < j < N,N为水平扫描线的数目),所以对于第i列上液晶画素的最后RMS电压值如(6)式:

(6)

分析(6)式各项

所表示的意义:大括号内的第一项Vi2是扫描第i列时的讯号电压平方值,第二项多项式重写如下式:

这项是表示在第i列以上的水平扫描线,在扫描週期内对于第i列的电容藕合效应。由于从第1列至第i-1列的垂直影像讯号与第i列上液晶画素所储存的影像讯号电压极性是相反的,对于第i列的液晶画素所造成的影响趋势是将液晶画素内储存的电荷经由藕合电容洩漏到垂直影像讯号驱动线。所以液晶画素的有效电压会较理想的电压位阶低。

参考(5)式中的第三项:

这项是表示在第i列以下的水平扫描线,在扫描週期内对于第i列的电容藕合效应。由于从第i-1列至第N列的垂直影像讯号与第i列上液晶画素所储存的影像讯号电压极性是相同的,对于第i列的液晶画素所造成的影响趋势是将储垂直影像讯号驱动线上的电荷经由藕合电容洩漏到液晶画素内。

重新审视整理(6)式,经过计算后可得到如(7)式的结果。(7)式的三个部份分别代表不同的意义:第一部份表示第i列上液晶画素被写入的正确电压,第二部份表示第一阶串音成份,第三部份表示第二阶串音成份。至于造成串音的主要成份是第一阶串音,第二阶串音由于是平方项所以造成串音的影响很小。所以垂直串音都以第二项的一阶串音为主要克服对象。

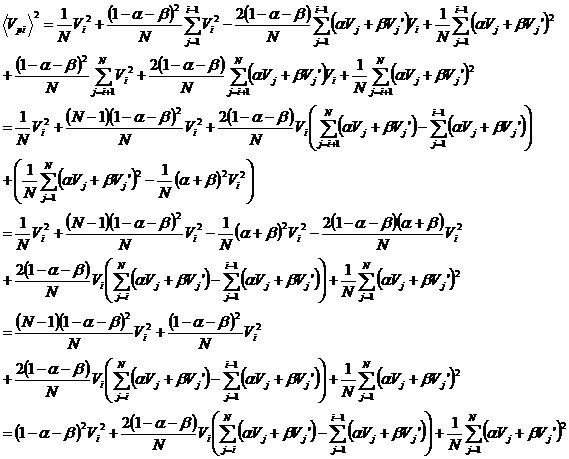

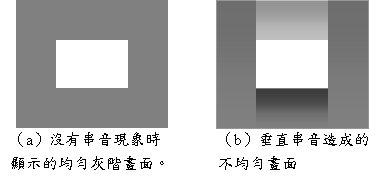

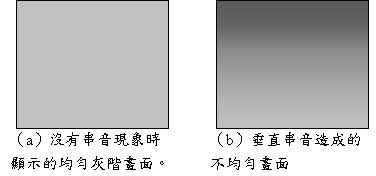

假设一个液晶显示器的画面具有240条水平扫描线,交流驱动的方式採用图框反转驱动,画面显示单一灰阶背景时,在实际画面上会有什麽情况发生?参考(7)式的结果: 若i<120也就是第i列是在前半部的水平扫描中的某一条时,由于从i+1至第N条水平扫描线的对应垂直影像电压极性与第i列相同,而且电容藕合的效果大于由第1列至第i-1列的相反极性电压藕合的影响,所以会造成第i列上液晶画素的RMS电压值大于理想正确电压值(1-α-β)2 Vi2,而且当i愈接近1时此一情况愈严重。相反的情况发生在当i>120时,液晶画素上的RMS电压值会愈来愈小于理想的正确电压值。若是液晶显示器是NW(Normal White)显像模式,垂直串音造成的结果是画面的亮度由画面顶端到底端分佈不均匀,愈顶端画面愈黑,愈低端画面亮度愈亮。参考图4的显示画面。

(7)

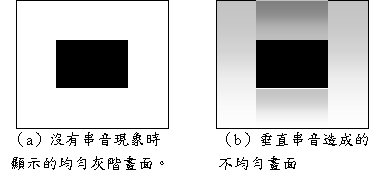

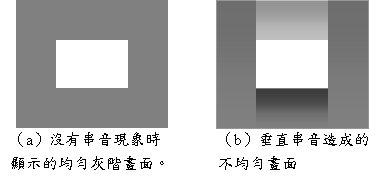

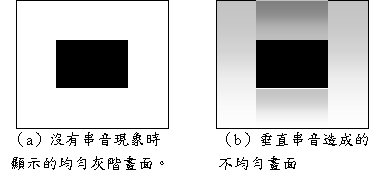

若是画面显示如图5的视窗画面时,同样可以用上述的方式来讨论:若是视窗画面为黑色背景与白色视窗时,由于白色视窗讯号电压为低电压驱动讯号,所以在白色视窗的垂直区域内,电压的电容藕合效应较低,所以上半部份的画面会较背景的亮度更低,下半部的情况则相反。若画面的视窗图样是白色背景与黑色视窗时,画面的显示状态如图6所示。

图4.採用图框反转交流驱动时,液晶画面的垂直串音现象。

图5.採用图框反转交流驱动时,液晶画面显示黑底白视窗画面的垂直串音现象。

图6.採用图框反转交流驱动时,液晶画面显示白底黑视窗画面的垂直串音现象。

1.2直行反转(Column Inversion)对垂直串音的影响

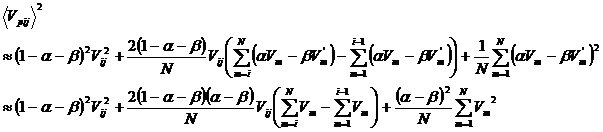

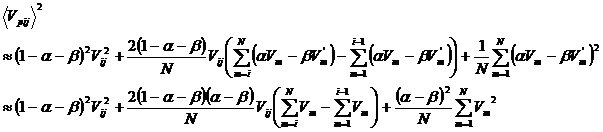

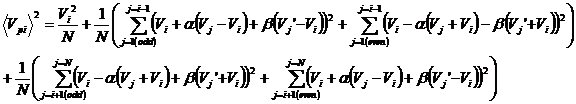

前面介绍了图框反转的垂直串音效应,现在继续考虑直行反转的交流驱动方式对垂直串音现象的影响。首先考虑直行反转时的垂直驱动电压的极性,若在第i列、第j行上的垂直驱动电压为正极性时,其相邻的第j’行上的驱动电压极性变为负极性驱动,所以在第i列、第j行上的液晶画素电压为:

(8)

如同前一节讨论的方式,若是以第i列为参考依据时,从第1列至第i-1列的水平扫描週期时间内,第j行上的垂直驱动电压极性都是与第i列,第j行上液晶画素所储存的电压极性相反,从i+1至第N列的水平扫描週期时间内的垂直驱动电压极性与第i列相同;相反的,在相邻的第j行上的电压极性正好相反,意即从第1列至第i-1列的垂直驱动电压极性与液晶画素所储存的电压极性相同,从i+1至第N列的垂直驱动电压极性是相反。所以在整个图框週期内,液晶画素内储存的RMS电压如(9)式:

(9)

比较(7)式与(9)式,可以发现在造成串音的主要成份中((7)式与(9)式中的第二项),直行反转由于相邻垂直电极对于液晶画素所造成的电容藕合效应有相互抑制的效果(参考(9)式第二项),所以垂直串音的现象因为採用直行反转的交流驱动方式而获得改善。

参考(9)式,若是假设Vm=Vm’时,(9)式可以改写成如(10)式:

(10)

同样的若(7)式的Vj=Vj’时,(7)式可以重写成如(11)式:

(11)

参考(10)与(11)可以更明显的看出图框反转的驱动方式与直行反转的驱动方式之间的差异;图框反转的方式中,水平方向上相邻的电极对于液晶画素是造成加成的藕合效应(因为电容藕合项为(α+β)),直行反转是造成相互抑制的效应(因为电容藕合项为(α-β))。

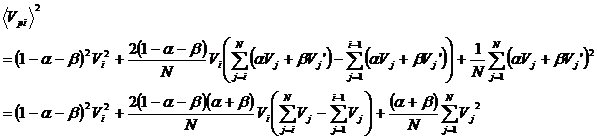

1.3线反转(Line Inversion)对于垂直串音的影响

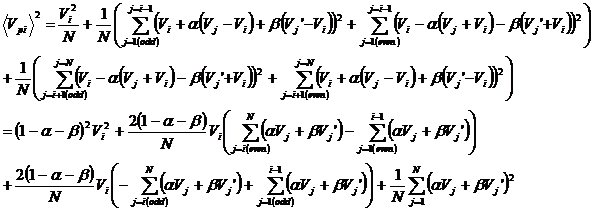

对于线反转的交流驱动讯号而言,在同一条水平线上的影像驱动讯号极性是相同的,但是相邻的水平扫描线上的垂直驱动讯号极性是相反的。若是第i条(假设i是偶数时)水平扫描线上对应的垂直讯号电压极性为正极性时;在整个图框扫描週期时间内,扫描第1条至第i-1条的水平扫描线时对应的讯号极性,偶数条的水平扫描线的讯号极性是负极性,奇数条扫描线上的驱动讯号为正极性;而后在驱动第i条扫描线上的液晶画素时,是将液晶画素由正极性转变成负极性;剩下的第i+1条至最后一条扫描线的驱动讯号极性也是偶数条是负极性,奇数条是正极性。所以对于第i条水平扫描线上的液晶画素的有效RMS可以用(12)式来表示:

(12)

(12)式中的第二项对应在第i条扫描线以上的驱动讯号对于液晶画素的影响,其中奇数条扫描线的影响是向正极性的方向(假设第i条扫描线为偶数条扫描线,而且液晶画素所储存的电荷电压极性为正极性),偶数条扫描线的驱动电压影响为向负极性的方向;同理从第i+1条到第N条扫描线的驱动电压影响与前述的相反。将(12)式简化可以获得(13)式的结果:

(13)

观察(13)式可以发现使用线反转的交流驱动方式,由于奇数条与偶数条水平扫描线对于液晶画素相反的电容藕合效应,使其具有与直行反转相似的抑制作用,不同的地方在于直行反转是相邻垂直驱动讯号间的抑制作用,线反转的交流驱动是由于相邻的水平扫描线上相反的垂直驱动电压极性,造成电容藕合效应的抑制。所以採用直行反转或是线反转对于垂直方向上的画面串音有明显的抑制,可以改善画面的显像品质。

若是将(13)式简化,同样假设Vj=Vj’时,即是以显像画面为单调的灰阶画面为参考时,能够更加的明瞭线反转对于垂直串音的影响。

(14)

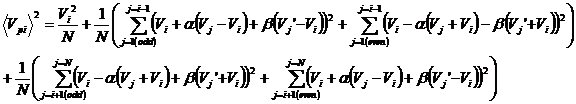

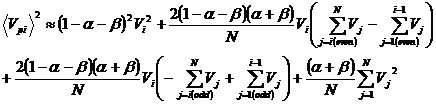

1.4点反转(Dot Inversion)对于垂直串音的影响

点反转的交流驱动方式可以视为直行反转与线反转交流驱动方式的组合,对于任意的一个液晶画素,它与周围其他四个液晶画素的电压极性都不相同。若是显示某一灰阶画面实,点反转的驱动方式对于液晶画素的影响如(15)式:

(15)

所以比较(15)式与其他驱动方式的分析结果,可以发现採用点反转的驱动方式对于垂直串音的抑制效果最佳。

1.5 水平串音的画面分析

水平串音的形成主因在于各个驱动电极上的讯号电压变化,经由液晶面板间的杂散电容藕合效应,影响到共通电极的参考位准,因而造成画面的水平串音。在此对于水平串音的分析主要是对于影像驱动讯号对于液晶画素的充电方式所造成的效应做讨论。

1.5.1串列输入/并列输出(Serial In /Parallel Out)方式的影响

首先考虑讯号驱动的方式是採用串列输入/并列输出的架构,这也是一般大尺寸高解析度的液晶显示器所採行的讯号驱动架构。基本的动作方式是影像讯号依时间的顺序依序的输入至影像讯号驱动电路,驱动电路依序的将影像讯号储存起来,等到一条水平扫描线的讯号全部都储存起来后,再同时并行的输出至液晶画素。所以此种方式对于共通电极的影响是发生在同一个时间点上。以下的讨论分别对于不同的极性驱动方式做更进一步的分析:

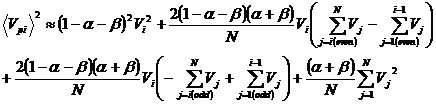

(a)採用图框反转或是线反转的驱动方式:

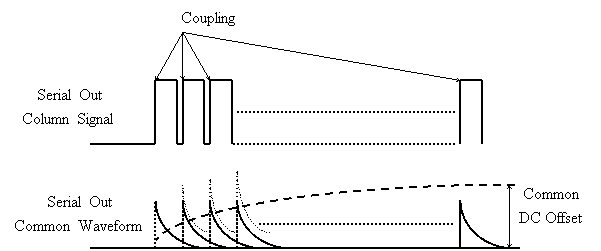

考虑一个影像讯号电极的输出电压讯号对于共通电极的影响为αVm,水平解析度为N的影像画面,对于共通电极的参考位准影响为NαVm,而且共通电极的影响会随水平解析度的增加而愈加严重。由于共通电极是一个RC的电路负载,所以共通电极上的参考位准变化可用RC放电曲线来描述,所以共通电极被藕合效应影响后,对于液晶画素参考电压位准的变化,必须视RC等效电路而定。若RC常数大的话,代表放电时间长,所以产生的误差电压大,因而造成较严重的水平串音的效应。参考图7。

图7.并列输出方式,图框反转与线反转之驱动方式对于共通电极的参考电位影响

(b)採用直行反转或是线反转的驱动方式:

採用直行反转与点反转的驱动方式,由于水平方向上,相邻的液晶画素的驱动电压极性是相反的,所以对于共通电极的藕合影响会有相互抑制的效果,因而降低水平串音的现象。

1.5.2串列输入/串列输出(Serial In /Serial Out)方式的影响

若讯号驱动的方式是採用串列输入/串列输出的架构,这也是一般小尺寸低解析度的低温多晶硅液晶显示器(Low Temperature Poly-Si TFT LCDs)所採行的讯号驱动架构。基本的动作方式是影像讯号依时间的顺序依序的输入至影像讯号驱动电路,驱动电路再依序的将影像讯号经由传输闸或是输出驱动电路输出至液晶画素。所以此种方式对于共通电极的参考电位影响是发生在不同时间点上。以下的讨论分别对于不同的极性驱动方式做更进一步的分析:

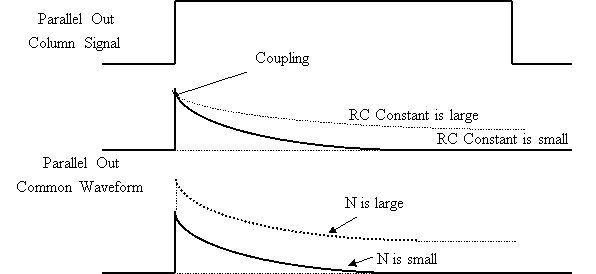

(a)採用图框反转或是线反转的驱动方式:

考虑一个影像讯号电极的输出电压讯号对于共通电极的影响为αVm,水平解析度为N的影像画面,对于共通电极的参考位准影响如图8,而且共通电极的影响会随水平解析度的增加而愈加严重。由于共通电极是一个RC的电路负载,所以共通电极上的参考位准变化可用RC放电曲线来描述,由于共通电极被藕合效应影响的时间点不在同一时间点上,所以会造成更严重的共通电极的参考电位漂动问题。若RC常数大的话,代表放电时间长,所以产生的误差电压大,因而造成更严重的水平串音的效应。参考图8。

图8. 串列输出方式,图框反转与线反转之驱动方式对共通电极的参考电位影响

(b)採用直行反转或是线反转的驱动方式:

採用直行反转与点反转的驱动方式,由于水平方向上,相邻的液晶画素的驱动电压极性是相反的,所以对于共通电极的藕合影响会有相互抑制的效果,因而降低水平串音的现象。

2.低温多晶硅薄膜电晶体液晶显示器的电路架构

经由上述对于影像画面的分析,我们可以明确的架构出LT Poly-Si TFT LCDs的电路架构,以及预测不同的架构对于画面的影响;此节主要是由驱动系统的观点来讨论不同的架构的优缺点:

2.1串列输入/串列输出(Serial In /Serial Out)方式

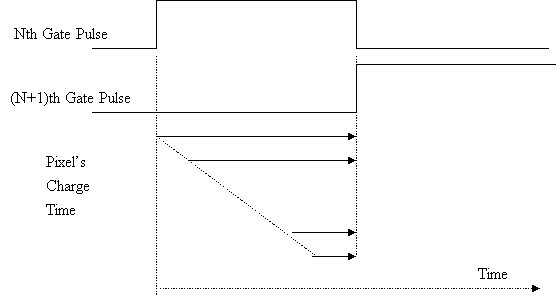

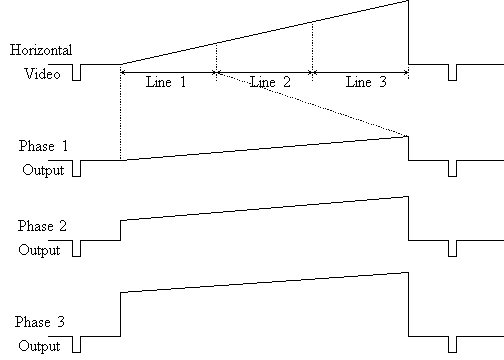

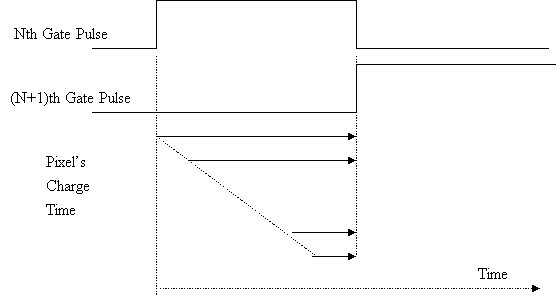

串列输入/串列输出方式的架构,对于高解析度大面积的TFT LCDS而言,是一个极不洽当的驱动方式,主要原因在于对于每个液晶画素的充放电时间不相同,参考图9,愈先取样输出的影像电压,对于液晶画素的充放电时间愈长,愈后取样输出的影像电压,对于液晶画素的有效充放电时间会愈短,因而造成画面的左右亮度不均匀。

图9.串列输出架构的液晶画素充放电时间

所以,对于大尺寸高解析度的液晶显示器而言,不建议採用此种架构,因为随著解析度的提高,表示一条水平扫描线的时间亦加缩短,因而会加重画面的不均匀性;随著面板面积的增加,造成垂直驱动电极与水平驱动电极的负载增加,使得水平脉波与讯号电压的驱动波形延迟时间增长,降低有对液晶画素的有效充放电时间,同样会增加画面亮度分佈的不均匀性。

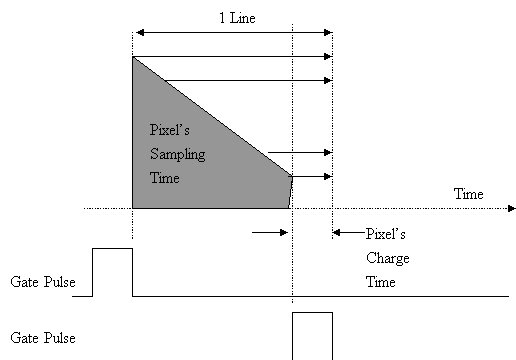

若为了克服亮度分佈不均匀的问题,可以採用如图10的驱动架构,先将垂直电极走线上的杂散电容充电(此时杂散电容当作是讯号电压的储存电容),待依序充电完毕后在开启水平脉波,但是此方式所面临的问题是水平脉波的时间宽度大幅的减小,对于高解析度的影像画面而言,所面临的问题是整个画面的液晶画素充放电时间不够,造成整个画面的亮度不足,而且画面对比剧降。

图10. 串列输出架构的驱动时序

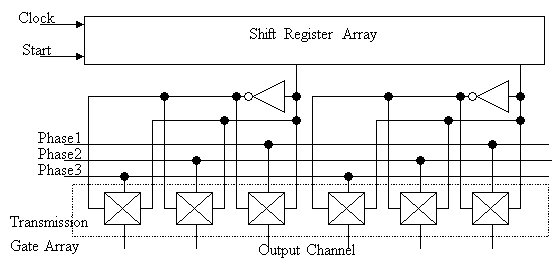

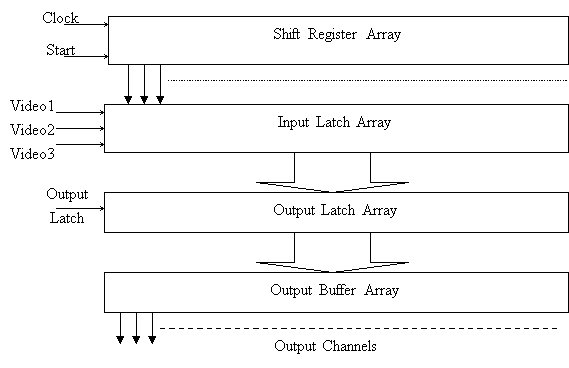

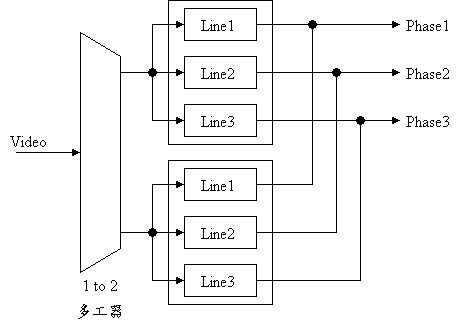

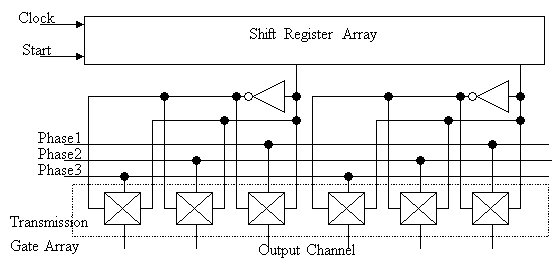

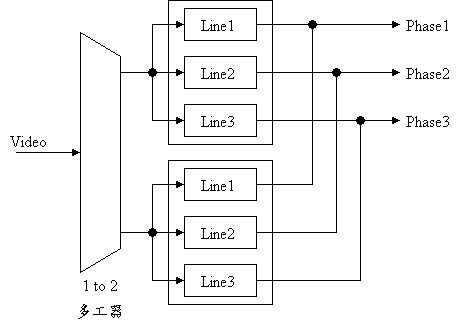

串列输入/串列输出的驱动电路架构,如图11所示。参考图11的架构,影像讯号的输入有三个路径,分别为Phase1,Phase2,以及Phase3;对于彩色的液晶面板而言,这三个影像讯号输入的路径分别为红色、绿色、及蓝色。若是VGA解析度的液晶面板,移位暂存器(Shift Register)的钟控讯号(Clock)的频率为25MHz。

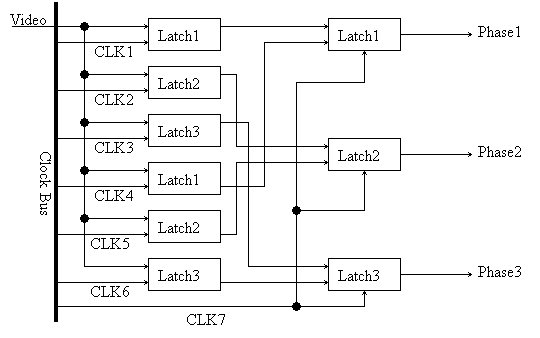

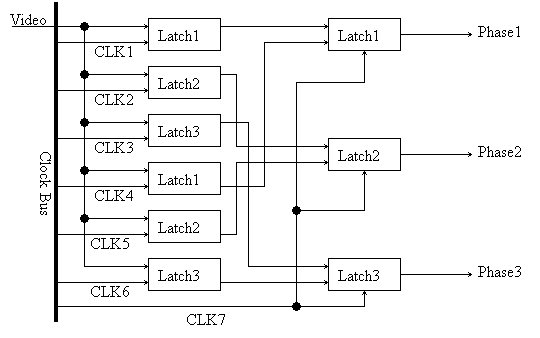

若是黑白的液晶面板而言,Phase1、Phase2、及Phase3的影像讯号为原本的影像讯号除三倍频后的低频讯号,而且移位暂存器的钟控讯号亦为25MHz的除三倍频,约为8.33MHz;如此架构的好处在于在玻璃上的积体化多晶硅驱动电路的操作频率可以降低,同时对于每一条垂直讯号电极走线上的杂散电容充电的时间较原本增加三倍,由原本的40ns增加为120ns。但是外部的影像讯号驱动电路的複杂度会增加许多。参考图12影像驱动分相电路的架构图、图13分相钟控讯号时序图。

图11. 串列输入 / 串列输出电路架构

图12. 影像驱动分相电路架构

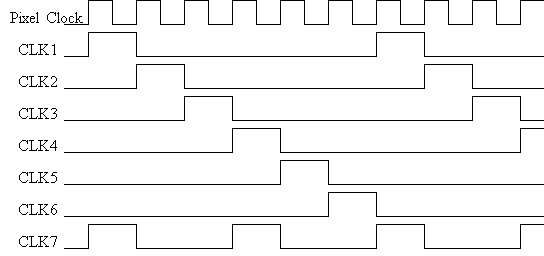

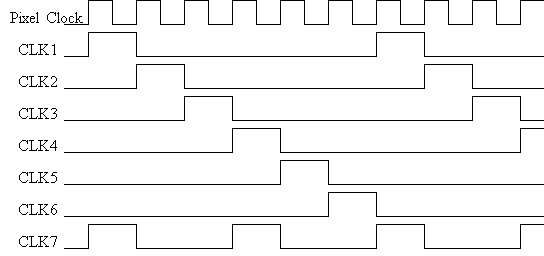

参考图12与图13,LCK1、CLK2、及CLK3分别控制第一级上半部三个栓锁电路(Latch1、Latch2、及Latch3),CLK4、CLK5、及CLK6分别控制第一级上半部三个栓锁电路;CLK7控制第二级的三个栓锁电路。第一级的两组栓锁电路将影像讯号交错的取样储存起来,第二级的栓锁电路则是经由内部多工器的选择,交错的选取上半部或是下半部栓锁电路所取样

储存的影像讯号,经由CLK7的钟控讯号将三个不同相位的影像讯号同步成为相同相位的讯号,再送至液晶显示器的驱动电路。

图13. 分相电路控制时序图

2.2串列输入 / 并列输出(Serial In / Parallel Out)方式

对于高解析度,大尺寸的液晶面而言,如果如同小尺寸的液晶面板一般,採用所谓的Driver on Glass的架构,就是将水平扫描脉波驱动线路与垂直影像驱动线路全部都设计佈局与玻璃之上,薄膜的製程採用多晶硅(Poly-Si)的元件,虽然可以提高电荷载子的移动率(Mobility),克服非晶硅(Amorphous Si)元件电荷载子移动率不足的问题,但是仍需要注意多晶硅元件在玻璃基板上製作电路的元件特性,是否达到高解析度的高频操作要求。例如对于SVGA的解析度而言,若是图框重複率(Frame Rate)为60Hz,对应的系统操作频率需要39MHz;若为XGA时,需要65MHz;若是更高的SXGA的解析度而言,所需的操作频率高达130MHz。

所以在高解析度、高频的操作模式下,採用Driver on Glass的架构时,对于驱动电路的设计架构,必须先做评估:在此提出三种驱动电路的架构以解决高频动作所可能面临的问题。

2.2.1 影像分相电路架构(Video Multi-Phase Structure)

第一种架构如前节所介绍的影像分相架构,但是为了增加对于垂直驱动电极走线上杂散电容的充电时间,驱动电路的架构为串列输入 / 并列输出的架构。若影像分相的数目愈多,垂直驱动电路的钟控讯号频率就愈低;假若将影像分成10相,对于60Hz图框重複率的VGA而言,钟控讯号由原先的25MHz降至2.5MHz;但是要注意,若是外部影像分相驱动电路(图12)处理的影像讯号是类比影像讯号时,影像分相的数目愈多,最后在液晶面板上所显示的影像画面会愈模糊,这是由于分相电路的低通滤波特性所造成,而且随分相数目的增加,低通的效果会愈明显;因此,若採用影像分相电路架构时,对于影像分相的数目需要多考虑,同时分相数目过多时,影像分相电路的控制时序会变的更複杂,所需的处理电路亦会增加许多。

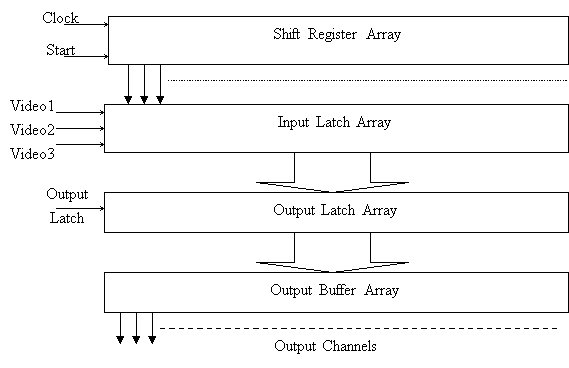

图14. 并列输出驱动电路架构

参考图14、移位暂存器(Shifter Register Array)依序的送出控制讯号控制输入栓锁暂存器(Input Latch Array),输入栓锁暂存器将影像讯号依序的取样储存起来,等到一条水平扫描线上的影像讯号全部都被取样储存后,利用输出栓锁讯号将输入栓锁暂存器所储存的影像资料转移至输出栓锁暂存器(Output Latch Array),同时输出对应的驱动电压至液晶面板上,在此同时输入栓锁暂存器再继续取样储存下一条水平线的影像讯号。由以上的动作方式可知,输出至液晶面板的驱动电压作用时间长达一条水平扫描线的週期,所以与串列输出的方式最大的不同,即是增加了对液晶面板上垂直驱动电极走线的杂散电容充电时间,改善显像画面的亮度不均匀性与低的画面对比。

至于图中的影像输入讯号有三组,对于彩色的液晶面板而言,此三组的影像输入讯号分别为红色、绿色、与蓝色。此时驱动电路的钟控讯号频率每有降低三倍,仍然维持显像系统的影像画素更换频率(Pixel Rate),若为三个相同颜色讯号的输入影像讯号,此时驱动系统的钟控讯号频率即可较画素更换频率降低三倍。

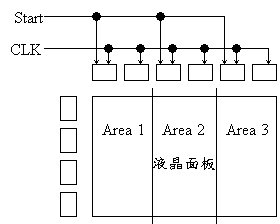

2.2.2垂直画面分割架构

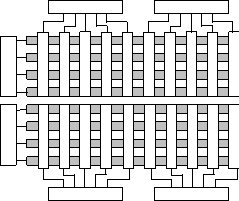

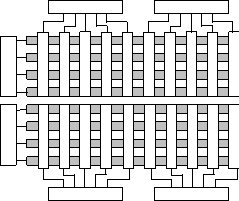

另一种降低驱动系统频率的方式是将显像画面分割成数个小的显像扫描区域,每个显像扫描区域都是同时的扫描显示画面。这种分个画面扫描的分是可以归纳成为两类,一为垂直画面分割,另一为时间扩展(Timing Expansion)的讯号处理架构。这节先对垂直画面分割的驱动架构做一简单的分析与介绍。首先参考图15的液晶面板佈局方式,将一个液晶面板分割成为上下两半,上面一半与下面一半的画面是被同时驱动显像,所以对于垂直讯号驱动电极走线的设计也与传统的方式不同,传统的垂直讯号电极佈局的方式是一条垂直讯号电极由面板的上方舖设到下方,若是对于VGA的驱动讯号而言,垂直方向的解析度为480条水平扫描线,所以一条垂直驱动讯号电极上便会连接480个液晶显像画素;但是垂直画面分割是将垂直讯号驱动电极走线分成上下两半,上半部连接240个液晶画素,下半部连接240个液晶画素。此种驱动架构使得每一条水平扫描线的週期成为传统的两倍,意即系统的操作率可以降低一半。

图15.垂直分割扫描的液晶面板架构图

从图15中可以看出垂直影像驱动电路需要两组,传统的扫描方式只需要一组的垂直影像驱动电路。对于外部的影像处理电路而言,影像电路处理的架构如图16:

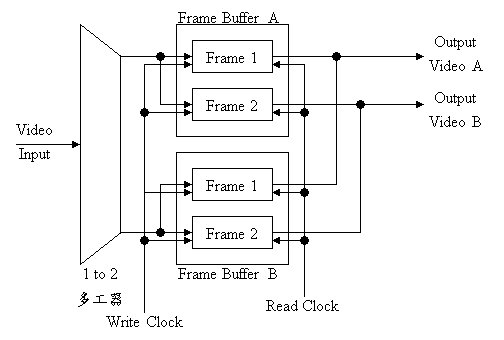

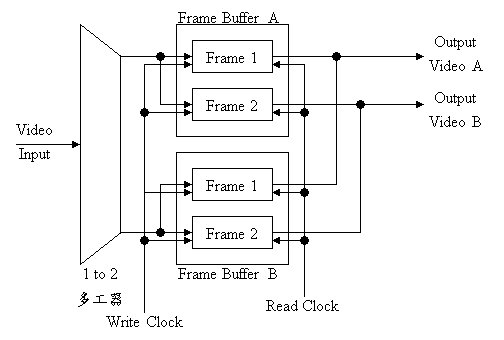

图16. 垂直画面分割影像处理电路架构

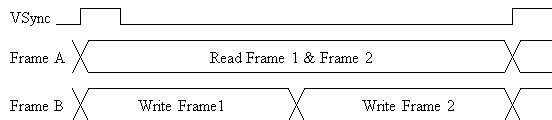

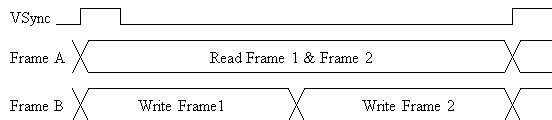

参考图16,输入影像讯号先经由多工器选择输入至哪一个图框缓衝记忆体。当图框缓衝记忆体A被多工器选择输入影像讯号储存时,在同一时间图框缓衝记忆体B将其所储存的影像资料输出至液晶面板的驱动电路。反之,图框缓衝记忆体A与B的处理动作交换;为何要如此的架构设计?其中原因为垂直分割画面的扫描方式,在输出影像讯号时记忆体所储存的资讯内容不可以变更,所以需要两组缓衝记忆体交互读写的动作。

在将影像讯号写入缓衝记忆体时,写入资料的顺序是从第一个图框记忆体写起,顺序的资料写入;当写完一半的图框画面资料后,接著后面一半的图框画面写入第二个图框记忆体。影像资料由图框记忆体内读出时,是同时由第一个与第二个图框记忆体并行的读出,送至液晶面板的驱动电路,所以图框记忆体的写入钟控讯号(Write Clock)的频率与影像讯号的画素更换频率(Pixel Rate)相同,但是图框记忆体的读取钟控讯号(Read Clock)频率只有写入频率的一半,而且每一条水平扫描线的週期增加一倍。影像讯号与控制讯号的关系如图17:

採用此种方式的优点在于液晶面板上的垂直影像驱动电路的操作频率可以降低一半外,另一个 优点是水平扫描週期的时间增加一倍,所以除了可以降低操作频率外,还可以增加TFT 的水平脉波选取时间,增加液晶电容充电的时间。

图17. 图框缓衝记忆体动作时序图

2.2.3时间扩展(Timing Expansion)架构

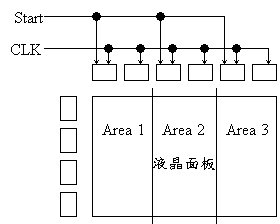

应用时间扩展电路架构时,液晶面板的佈局上与传统的方式相同,但是垂直驱动电路的架构需要做变更,参考图18,假设将画面在水平方向上分割成为三个显像区域,每个显像区域如同垂直画面分割的方式,都是并行同时扫描。因此垂直驱动电路的操作频率可以较原先所需的降低为三分之一。

但是要注意到,水平扫描时间週期并没有改变,若原先水平扫描週期为31us,採用垂直画面分割的电路架构,水平週期增加为62us,但是时间扩展的电路架构週期仍为31us。另外比较两者的影像讯号处理架构,垂直画面分割需要图框记忆体(Frame Memory),但是时间扩展方式只需要线扫描记忆体(Line Memory)。在液晶面板的佈局架构上,垂直画面分割需要在佈局上将液晶面板分成上下两个独立的显像区域,垂直讯号驱动电极分别由上下两边的驱动电路所驱动,垂直电极也被分割成上下两个独立的驱动电极走线。採用时间扩展方式时,液晶面板的佈局方式与传统的完全相同,不需要在佈局上将液晶面板分割,只需在垂直驱动电路上做电路架构的独立分割。

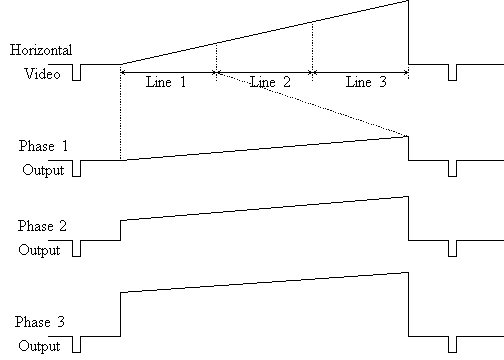

图18. 时间扩展方式垂直驱动电路架构

参考图18,垂直驱动电路的控制与传统的方式的不同点,最主要是在水平扫描触发讯号的控制模式,传统的触发讯号是触发第一颗垂直驱动晶片开始动作扫描,但是时间扩展的方式是扫描触发讯号是同时触发三个扫描区间的第一颗驱动晶片,同时操作频率降低为原本所需的三分之一。

至于外部讯号处理电路的架构如图19,两组扫描线缓衝记忆体的功用在于影像讯号写入一组的同时,另一组将所储存的影像资料输出至液晶的驱动电路。讯号处理的时序图如图20:

图19. 外部讯号处理电路架构图

图 20. 讯号处理架构图

3.结论

以上各节分别针对低温多晶硅所可採行的驱动架构做初步的介绍,同时针对不同架构所可能面对的画面问题做初步的讨论,综合以上的各部分讨论,对于高解析度的液晶面板,要採用多晶硅元件于玻璃上製作驱动电路时,需要针对多晶硅的频率操作特性作深入的瞭解,方可採行适当的驱动电路架构。例如将串列输入 / 串列输出的电路架构应用于大尺寸、高解析度的液晶面板时,第一个面临的问题是多晶硅元件的操作频率是否可以达到要求,第二是对于垂直驱动电极走线的杂散电容充电的问题,因为时间过短的话,无法对液晶画素提供正确的充电电压位准,第三由于对于液晶画素的充电时间随画素在水平扫描线上的位置不同,因而随之改变,可能造成画面的亮度分佈不均匀的问题,第四若是要降低驱动电路的操作频率,以及增加对垂直驱动电极的充电时间,採用影像分相驱动的架构时,对于类比的影像讯号若分相数目过多,会造成严重的低通滤波器的效果,使得高频画面失真。

再者,需要考虑到驱动电路的架构,事实上与外部讯号处理电路的架构是一体的,在决定採用何种的驱动电路架构时,即已决定可与之搭配的讯号处理电路架构,具体而言,面板上的驱动电路与外部处理电路所要执行的工作定为100%时,若是面板上驱动电路所能处理的部分仅为20%,那麽外部电路就要处理80%的工作,所以虽然将驱动电路直接製作于玻璃上有降低液晶面板的成本考量,但是必须更进一步的考量外部处理电路的複杂度与周边电路成本上升的问题,所以对于利用多晶硅元件直接于玻璃上製造驱动电路的竞争优势,势必要以液晶模组的角度作整体性的考量,方可摆脱由半导体製程方面考虑的盲点。

这篇关于(南京观海微电子)——液晶画面Crosstalk的原理与本质分析的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()