本文主要是介绍LLVM Cpu0 新后端 系列课程总结,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

想好好熟悉一下llvm开发一个新后端都要干什么,于是参考了老师的系列文章:

LLVM 后端实践笔记

代码在这里(还没来得及准备,先用网盘暂存一下):

链接: https://pan.baidu.com/s/1yLAtXs9XwtyEzYSlDCSlqw?pwd=vd6s 提取码: vd6s

系列课程告一段落,这里对这个系列课程做个总结。

1.文件对应的功能

| 文件 | 功能 |

| Cpu0AsmParser.cpp | 汇编器 |

| Cpu0Disassembler.cpp | 反汇编器 |

| Cpu0ABIInfo.cpp/.h | Cpu0ABIInfo.cpp定义ABI的信息,提供了O32、S32和未知三种ABI规范。 |

| Cpu0AsmBackend.cpp/.h | 定义后端的一些功能,包括重定位等等 |

| Cpu0BaseInfo.h | 一些flag信息的定义 |

| Cpu0ELFObjectWriter.cpp | 用来完成最终的 ELF 文件格式的写入任务 |

| Cpu0ELFStreamer.cpp/.h | 定义了一个cpu0架构的elf文件输出流类 |

| Cpu0FixupKinds.h | 重定位相关的Fixups结构的定义 |

| Cpu0InstPrinter.cpp/.h | 将Cpu0的MCInst(Machine Code Instruction)转换成可读的Cpu0汇编指令 |

| Cpu0MCAsmInfo.cpp/.h | 定义了一些汇编文件格式通用的东西 |

| Cpu0MCCodeEmitter.cpp/.h | 负责汇编指令最后发射 |

| Cpu0MCExpr.cpp/.h | 定义一些汇编阶段的符号、表达式等 |

| Cpu0MCTargetDesc.cpp/.h | Cpu0MCTargetDesc里边包括了对Cpu0架构的详细描述,包括对td文件生成的相应的inc文件的引用,以及对Cpu0各个工具的注册 |

| Cpu0TargetStreamer.cpp/.h | 定义了一个cpu0架构的后端输出流类 |

| Cpu0TargetInfo.cpp/.h | Cpu0TargetMachine就是为了定义Cpu0 Target供外部文件引用的 |

| Cpu0.h | Cpu0后端全局函数的入口 |

| Cpu0.td | Cpu0后端入口的td文件,include了其余的td文件 |

| Cpu0AnalyzeImmediate.cpp/.h | 分析一些带立即数的指令,framelowering的辅助函数 |

| Cpu0AsmPrinter.cpp/.h | 将LLVM的机器代码(Machine Code)转换成Cpu0汇编代码 |

| Cpu0CallingConv.td | Cpu0架构的Calling Convention |

| Cpu0DelaySlotFiller.cpp | 延迟槽插入的后端PASS |

| Cpu0DelUselessJMP.cpp | JMP优化的后端PASS |

| Cpu0FrameLowering.cpp/.h | 栈桢处理相关的,包括prologue和epilogue。 |

| Cpu0InstrFormats.td | 定一个Cpu0Inst这个指令父类,以及Cpu0架构的各种指令形式 |

| Cpu0InstrInfo.cpp/.h | 对于Cpu0GenInstrInfo类的使用,td文件能定义的功能有限,还需要使用cpp文件进一步扩展。 |

| Cpu0InstrInfo.td | 定义了各种指令,以及各种匹配模式 |

| Cpu0ISelDAGToDAG.cpp/.h | 指令选择的一些接口 |

| Cpu0ISelLowering.cpp/.h | LLVM IR转换为DAG。 |

| Cpu0MachineFunctionInfo.cpp/.h | Cpu0架构Machine Function一些通用接口的定义 |

| Cpu0MCInstLower.cpp/.h | 将 MI 指令 lower 到 MCInst 指令的工作 |

| Cpu0RegisterInfo.cpp/.h | 对于Cpu0GenRegisterInfo类的使用,td文件能定义的功能有限,还需要使用cpp文件进一步扩展。 |

| Cpu0RegisterInfo.td | 定义了各种寄存器,以及寄存器集合 |

| Cpu0Schedule.td | 定义了指令调度策略 |

| Cpu0SEFrameLowering.cpp/.h | 栈桢处理相关的,包括prologue和epilogue。 |

| Cpu0SEInstrInfo.cpp/.h | 对于Cpu0GenInstrInfo类的使用,td文件能定义的功能有限,还需要使用cpp文件进一步扩展。 |

| Cpu0SEISelDAGToDAG.cpp/.h | 指令选择的一些接口 |

| Cpu0SEISelLowering.cpp/.h | LLVM IR转换为DAG。 |

| Cpu0SERegisterInfo.cpp/.h | 对于Cpu0GenRegisterInfo类的使用,td文件能定义的功能有限,还需要使用cpp文件进一步扩展。 |

| Cpu0Subtarget.cpp/.h | Cpu0架构Subtarget的定义 |

| Cpu0TargetMachine.cpp/.h | Cpu0架构Target Machine接口的定义 |

| Cpu0TargetObjectFile.cpp/.h | 定义cpu0架构目标文件的一些配置 |

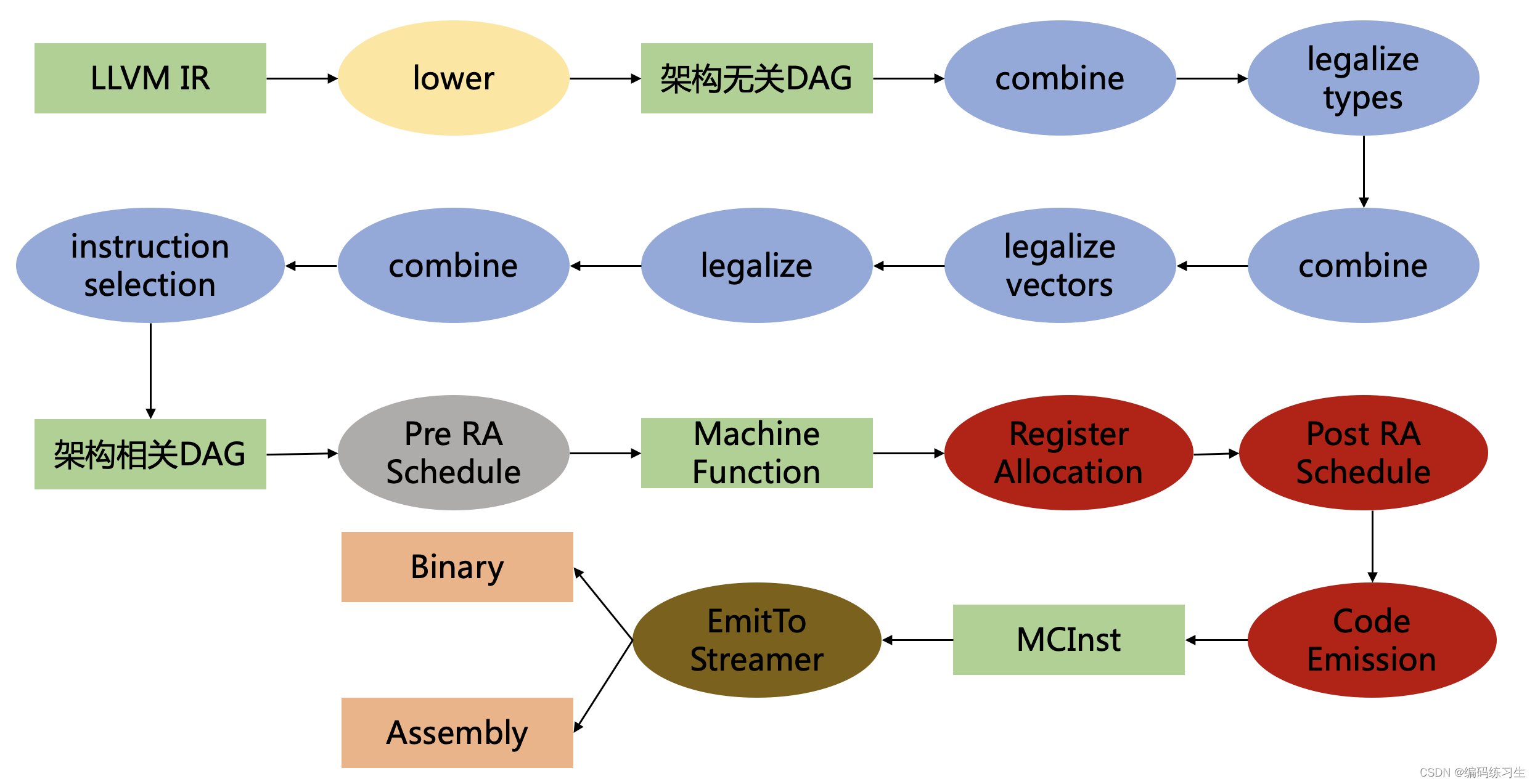

2.后端流程

3.待补充

之后想到了什么会继续补充

这篇关于LLVM Cpu0 新后端 系列课程总结的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!