本文主要是介绍libsystemctlm-soc项目分析,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

概述

libsystemctlm-soc项目是Xilinx的SystemC库。

环境安装

verilator安装

# Prerequisites:

#sudo apt-get install git help2man perl python3 make autoconf g++ flex bison ccache

#sudo apt-get install libgoogle-perftools-dev numactl perl-doc

#sudo apt-get install libfl2 # Ubuntu only (ignore if gives error)

#sudo apt-get install libfl-dev # Ubuntu only (ignore if gives error)

#sudo apt-get install zlibc zlib1g zlib1g-dev # Ubuntu only (ignore if gives error)git clone https://github.com/verilator/verilator # Only first time# Every time you need to build:

unsetenv VERILATOR_ROOT # For csh; ignore error if on bash

unset VERILATOR_ROOT # For bash

cd verilator

git pull # Make sure git repository is up-to-date

git tag # See what versions exist

#git checkout master # Use development branch (e.g. recent bug fixes)

#git checkout stable # Use most recent stable release

#git checkout v{version} # Switch to specified release versionautoconf # Create ./configure script

export VERILATOR_ROOT=`pwd`

./configure --prefix=<安装路径>

# Configure and create Makefile,安装路径要和源文件路径不一样,因为源文件中有bin文件夹,安装会重新生成bin文件夹;若路径仍然一样,install时会报冲突

# 设置 CXXFLAGS=-std=c++11 ./configure --prefix=<安装路径>

make -j `nproc` # Build Verilator itself (if error, try just 'make')

make installcp $VERILATOR_ROOT/include <安装路径> -r // 安装路径中没有include文件夹

环境变量

增加.config.mk文件

添加SYSTEMC变量

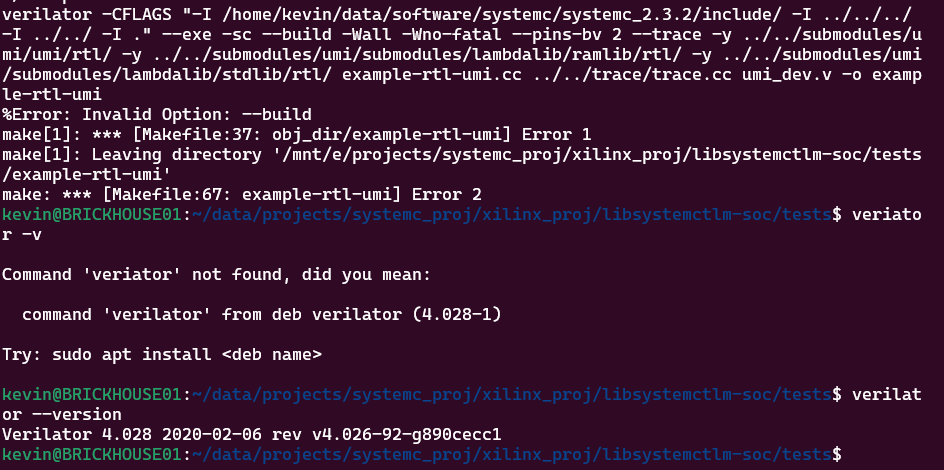

verilator版本太旧,不识别-build选项

verilator 4.028不支持-build选项,改换成v5.024

v5.024仿真报错,推测新版本不稳定,后改用v4.110

在Vmware中qemu嵌套虚拟化的设置

CSDN: vmware中创建qemu的嵌套虚拟化问题

umi编译报错

git仓库不全

测试用例解析

rtl-bridge/pcie/test_pcie_ep

仿真环境架构

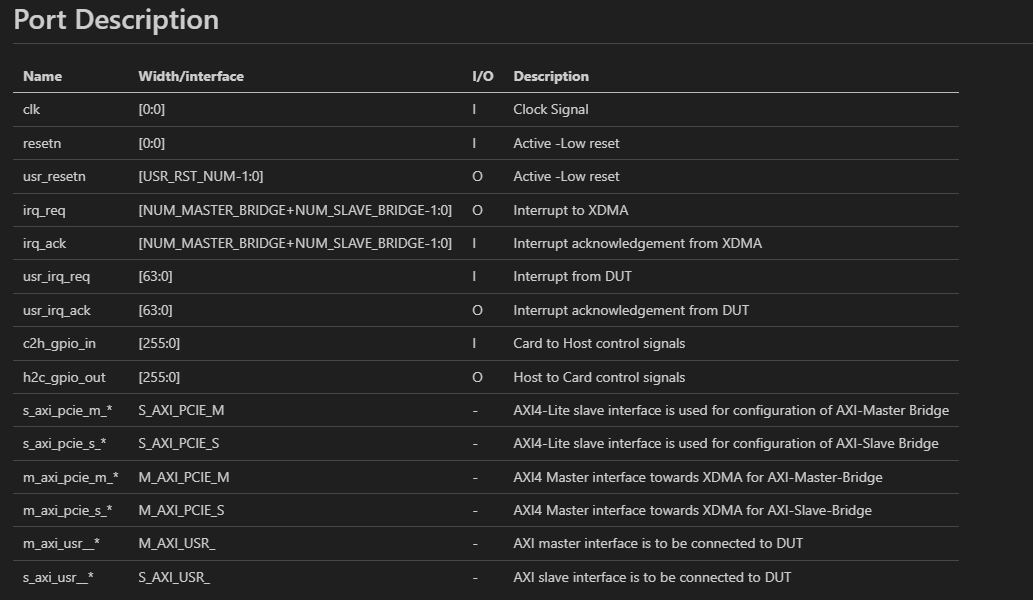

bridge端口信号

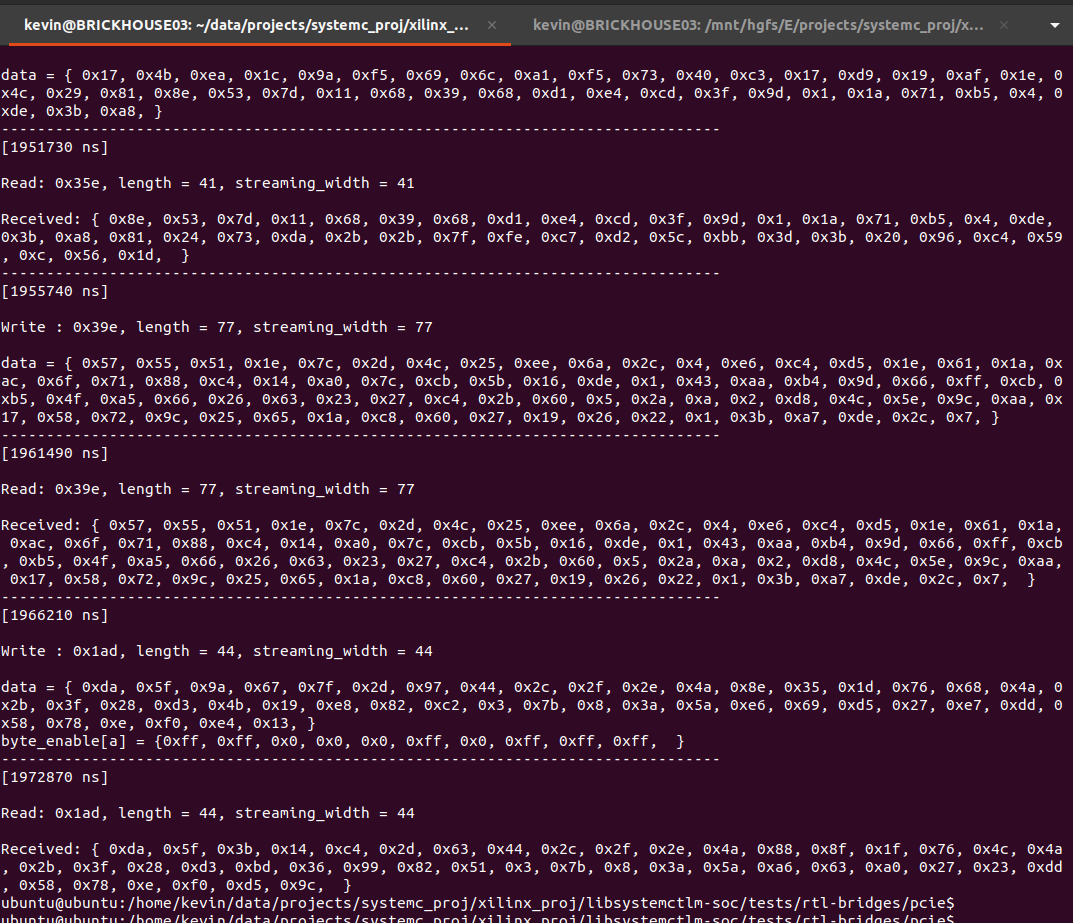

仿真过程及结果

制作镜像

qemu-img create -f qcow2 hd0.qcow2 2G

rtl-bridge/pcie/test-pcie-ep-master-vfio

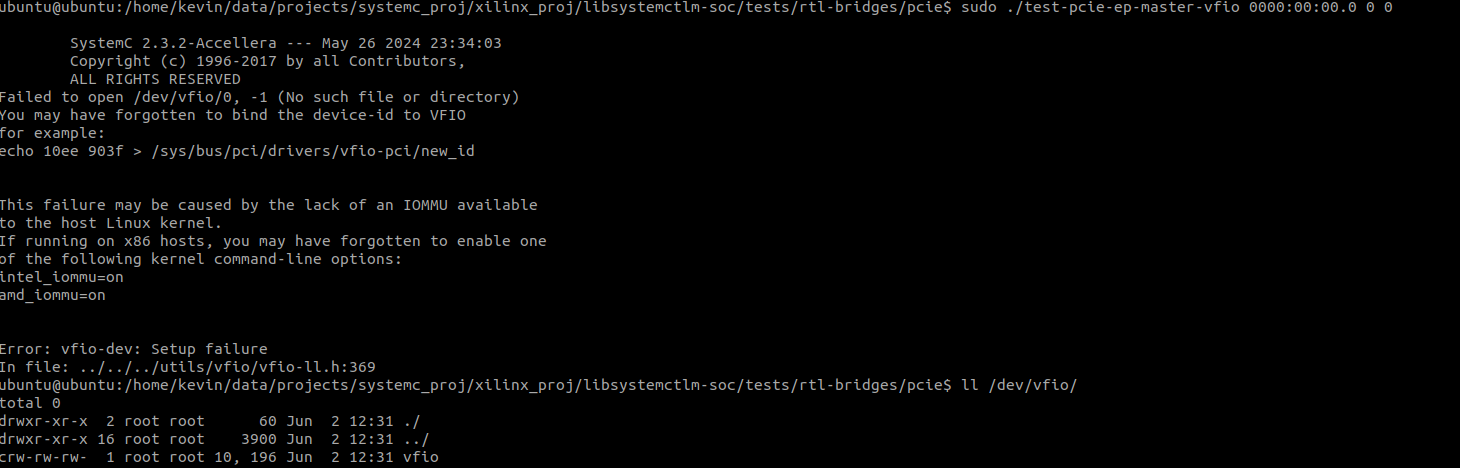

Failed to open /dev/vfio/0

rtl-bridge/pcie/refdesign-sim

仿真环境架构

该测试用例需在xilinx/qemu中运行,qemu和refdesign-sim测试用例通过remote-port连接,该组件是一个使用socket和共享内存在二者间输出事务的协议框架。

仿真时,qemu先运行,refdesign-sim后运行,refdesign-sim创建共享文件,qemu通过-machine-path指定路径监听到共享文件后开始运行。该测试目标只是实验qemu和systemc的协同仿真机制,通过hotplug判断设备是否被qemu识别,没有具体业务流。

Xilinx Wiki: QEMU Options and Commands

加了nographic选项

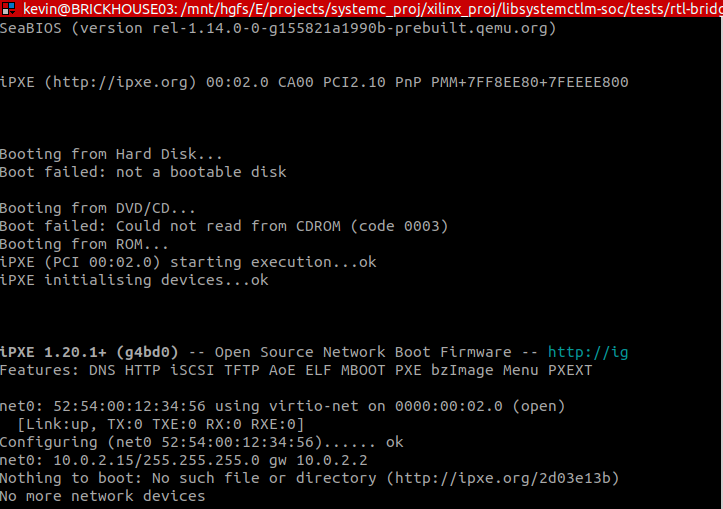

qemu-system-x86_64 -nographic -M q35,accel=kvm,kernel-irqchip=split \-device intel-iommu,intremap=on,device-iotlb=on \-cpu host -smp 8 -m 8G \-netdev user,hostfwd=tcp:127.0.0.1:2225-10.0.2.15:22,id=n0 \-device virtio-net,netdev=n0 \-drive file=hd0.qcow2,format=qcow2 \-machine-path machine-x86/ \-serial mon:stdio \-device ioh3420,id=rootport,slot=0 \-device ioh3420,id=rootport1,slot=1

-drive file=hd0.qcow2,format=qcow2

找不到hd0.qcow2来源,无法完成启动

qemu的进入monitor窗口ctrl+a c,按c的时候不用按ctrl

(忍不住口吐芬芳,坑爹。。。)

仿真过程及结果

这篇关于libsystemctlm-soc项目分析的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!