本文主要是介绍《S3C2440A时钟体系小结》,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

1.时钟源来源:S3C2440A处理器的主时钟可由外部晶振或者外部时钟提供。

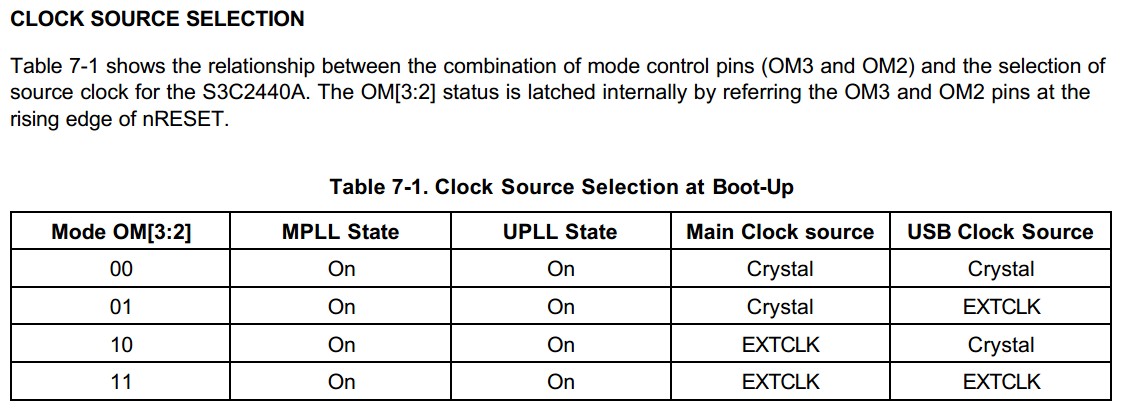

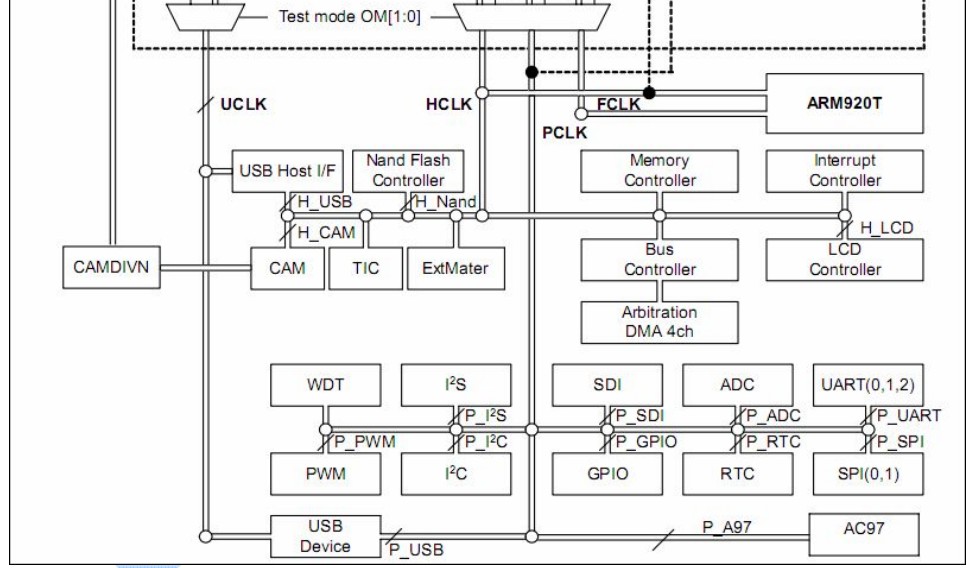

2.时钟源选择:对时钟源的选择是通过OM[3:2]来实现,如下表所示:(中英文版参照)

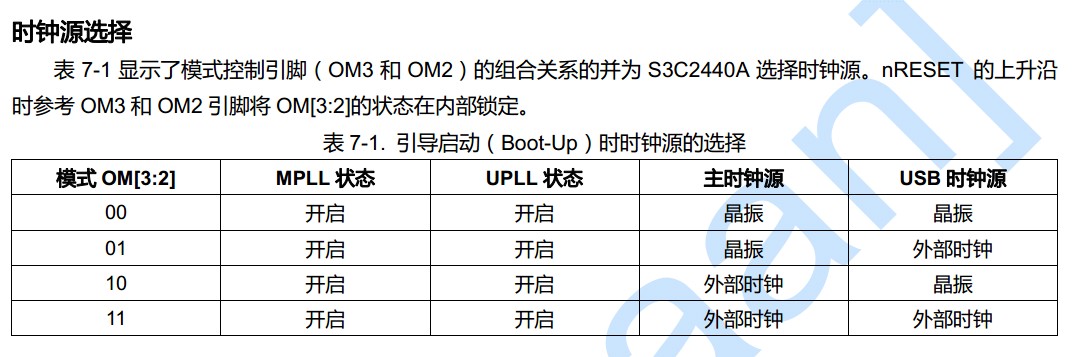

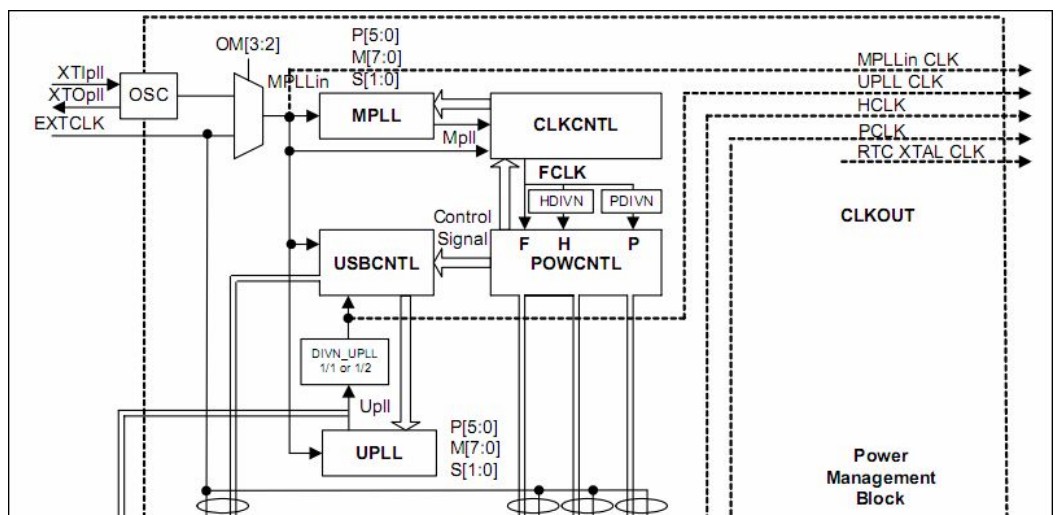

3.时钟源选择好之后就由PLL电路模块进行倍频,S3C2440有两个锁相环(PLL),分别为MPLL和UPLL。MPLL用于CPU及其他高低速外设,它可以产生三个时钟频率,分别为FCLK、HCLK、PCLK。其中,FCLK用于CPU核,HCLK用于AHB总线外设(如SDRAM),PCLK用于APB总线外设(如UART)。UPLL用于USB设备(48MHz)。具体电路如下图所示:

由技术手册可知:输出时钟频率 Mpll 与输入时钟频率 Fin 有等式 :

Mpll = ( 2 × m × Fin ) / ( p ×

这篇关于《S3C2440A时钟体系小结》的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!