本文主要是介绍PCIe-(3),希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

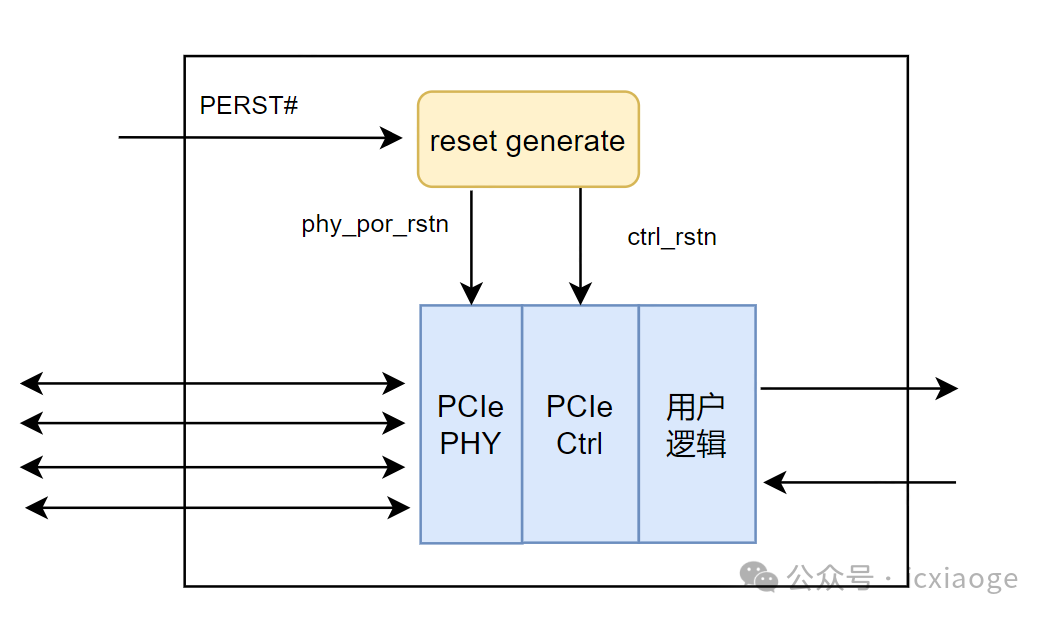

PCIe复位:

http://blog.chinaaet.com/justlxy/p/5100057844

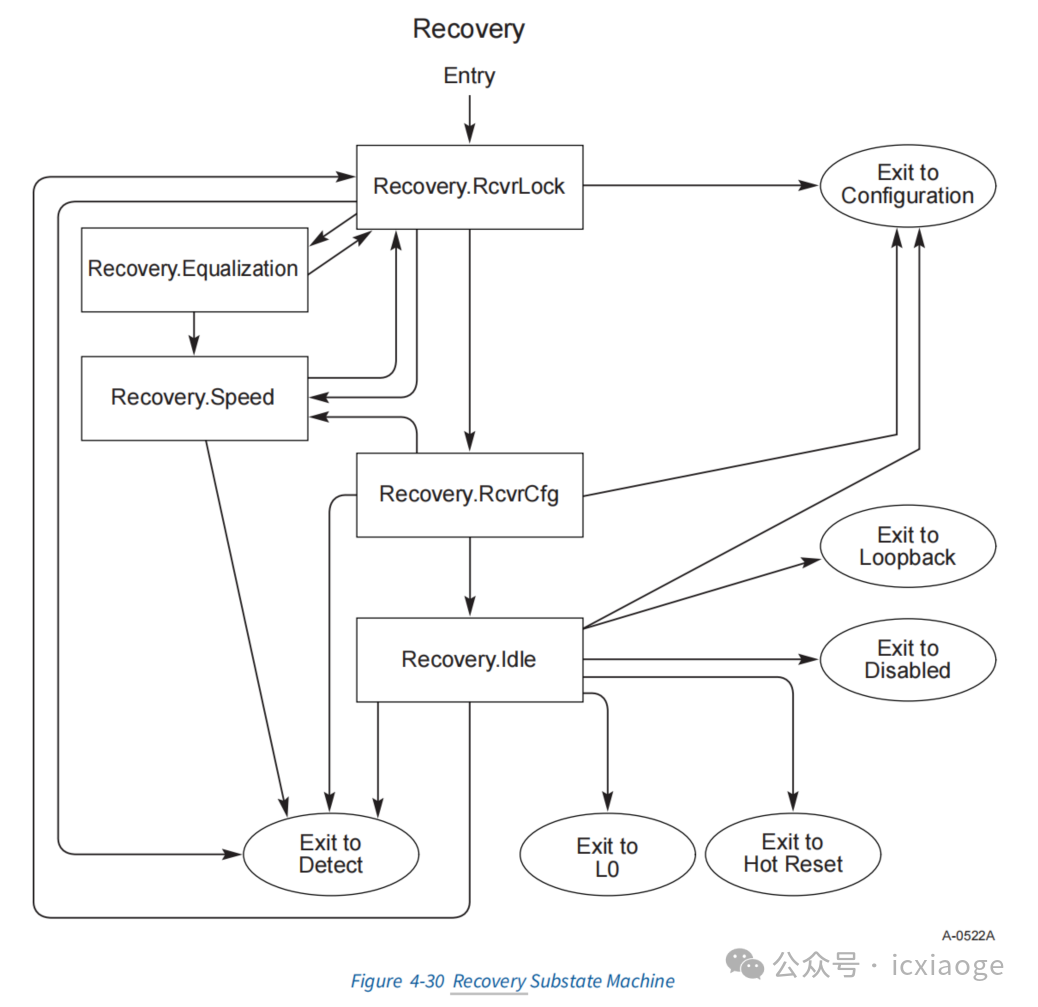

LTSSM状态:

https://blog.csdn.net/zhuzongpeng/article/details/78995340

PCIe SWITCH芯片:

https://docs.broadcom.com/doc/12351856

其它参考:

https://indico.cern.ch/event/121654/attachments/68430/98164/Practical_introduction_to_PCI_Express_with_FPGAs_-_Extended.pdf

这篇关于PCIe-(3)的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!