本文主要是介绍多分支拓扑阻抗匹配,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

最近测试信号质量,发现在有过冲、振铃等问题的时候大部分硬件工程师喜欢直接调大匹配电阻或者减小驱动电流,虽然这种操作是有效果的,但是我认为应该还可以更严谨的计算下,而不是选几个电阻多次尝试,显得不是很专业。

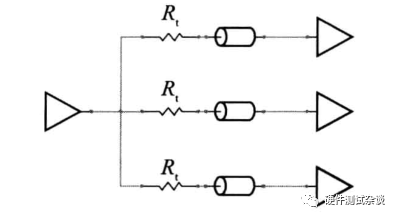

今天正好不是很忙,正好简单梳理下。下面使用ADS仿真简单看下如何选择匹配电阻,点对点的拓扑相对简单网上资料比较多,我们选择下边这种拓扑看看。

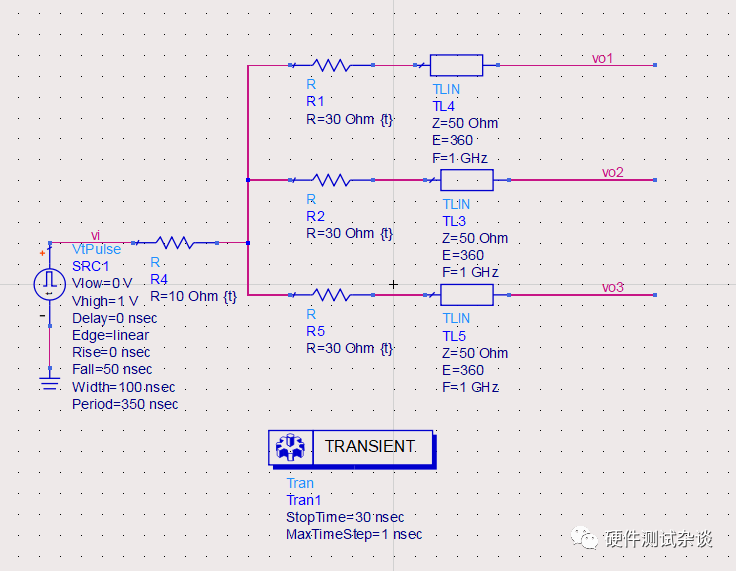

如何选择Rt,看下仿真的情况,原理图如下,其中R4是输出电阻,R1~R3是匹配电阻:

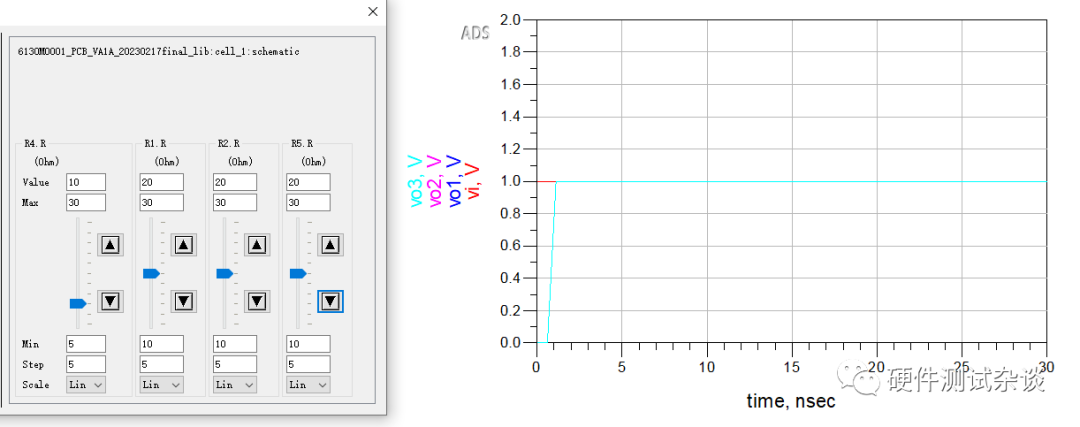

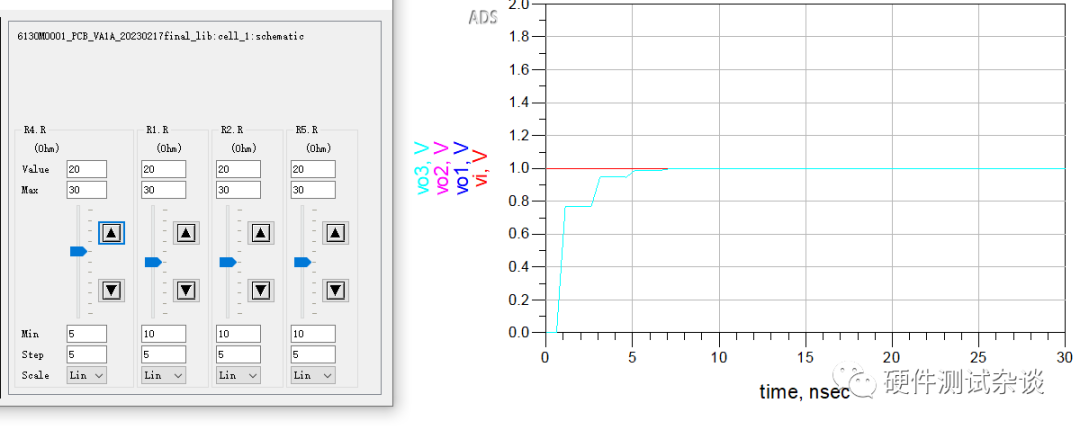

完全匹配的情况:

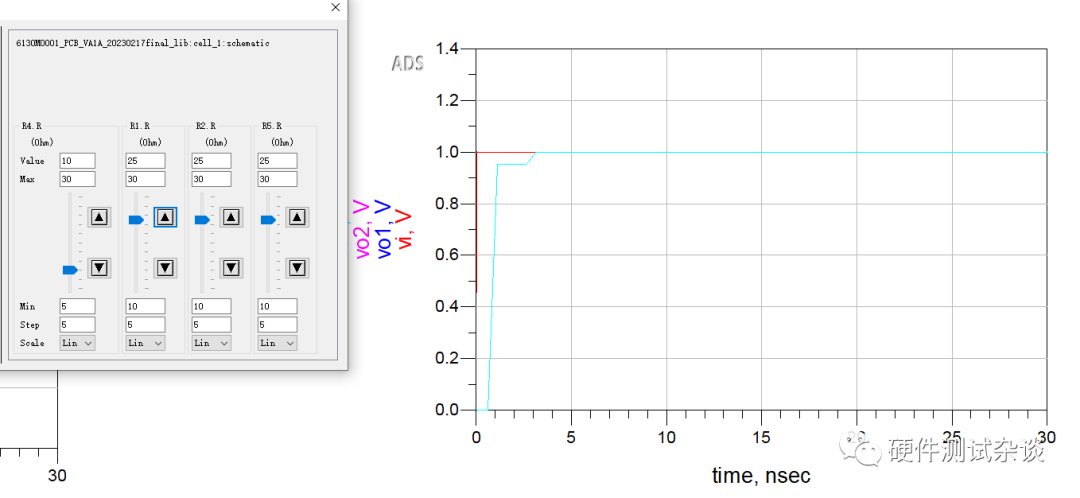

匹配电阻调大:

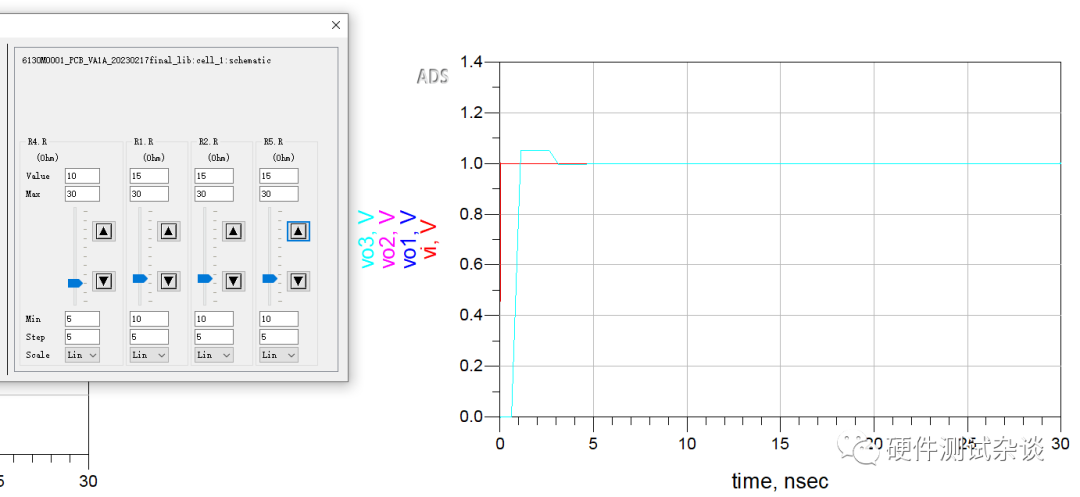

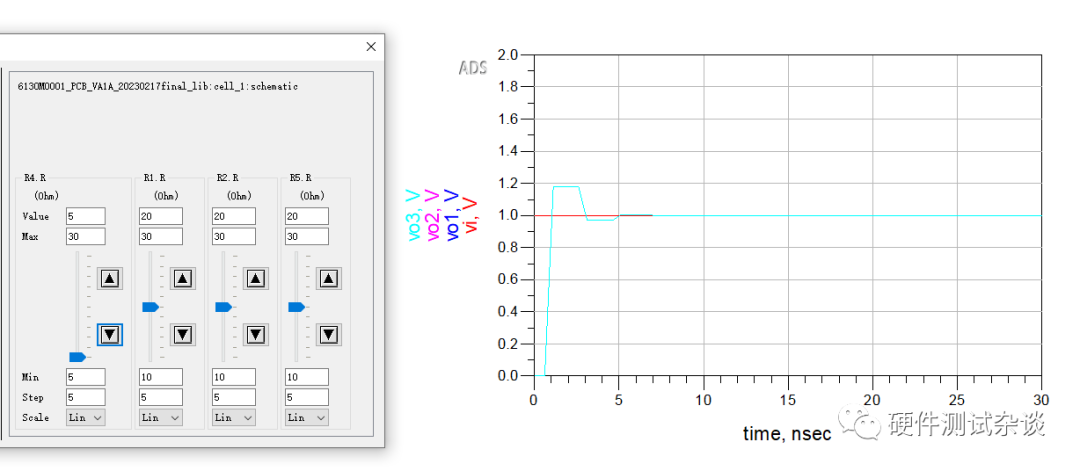

匹配电阻调小:

输出电阻调大:

输出电阻调小:

从上面几个图就能明显看出,当有过冲的时候,调高匹配电阻或者输出电阻(也就是减小驱动电流),可以把过冲拉低。

什么原因呢,根据反射的计算公式:ZO-ZI/ZO+ZI,很容易看到当电阻调高的时候,传输线的特征阻抗分压变小,在接收端反射回来后电压同样变低,波形上表现就是过冲拉低了。

那具体选择多大的匹配电阻呢,先给个公式:R=传输线特征阻抗Z-3*输出阻。例如上例中Z=50,输出阻抗R4=10,则匹配电阻是50-3*10=20。推导的话就是根据反射公式。

最后在补充几点,实际情况比较复杂,不会是如此理想的结构拓扑,大家要根据理论去实际计算。例如输出电阻是打开和关闭的时候是不一样的,也就是一定不会有完全匹配的电阻;然后就是分支一定要等长,否则反射时长不一样也会导致波形畸变。

这篇关于多分支拓扑阻抗匹配的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!