本文主要是介绍【脚本篇】---spyglass lint脚本,希望对大家解决编程问题提供一定的参考价值,需要的开发者们随着小编来一起学习吧!

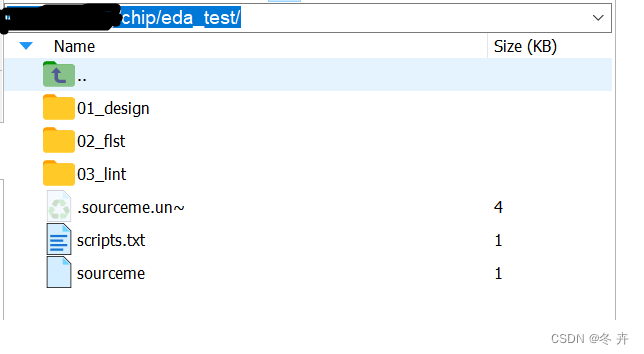

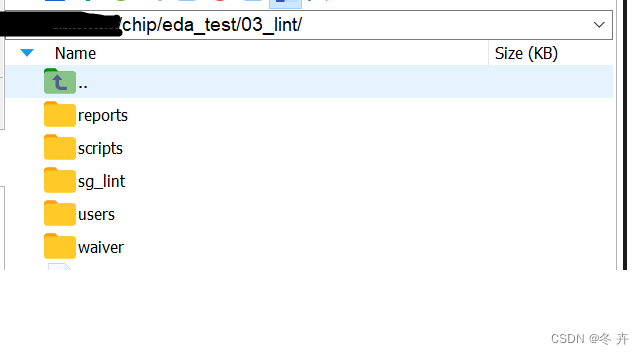

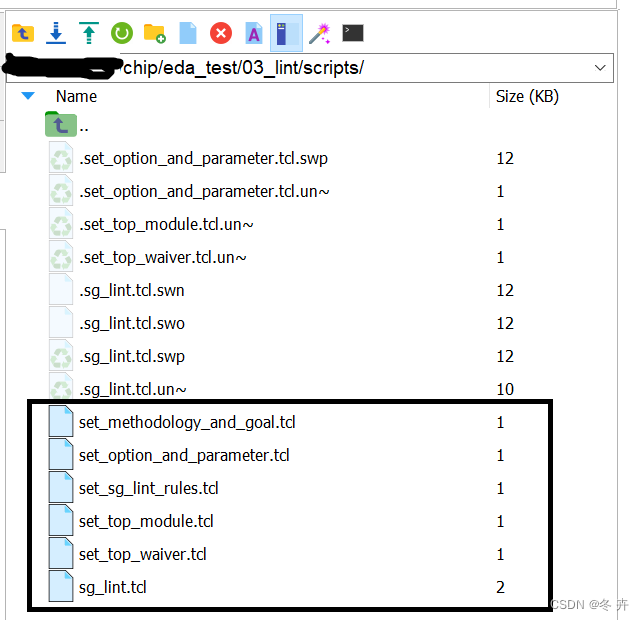

目录结构

sg_lint.tcl (顶层)

#1.source env

#date

set WORK_HOME .

set REPORT_PATH ${WORK_HOME}/reports

puts [clock format [clock second] -format "%Y-%m-%d %H:%M:%S"]

#2.generate source filelist

#3.set top module

puts "######### set top module #########"

source ${WORK_HOME}/scripts/set_top_module.tcl#4.set waiver

puts "######### set waiver file #########"

source ${WORK_HOME}/scripts/set_top_waiver.tcl#5.new project

puts "######### new project #########"

#new_project sg_lint -projectwdir ${WORK_HOME}/project/ -force

new_project sg_lint -force#6.read design file

puts "######### read design file #########"

read_file -type sourcelist ${WORK_HOME}/../02_flst/filelist.f#7.read waiver file

puts "######### read waiver file #########"

read_file -type awl $TOP_WAIVER_FILE#8.set common option and parameter

puts "######### set common option and parameter #########"

source ${WORK_HOME}/scripts/set_option_and_parameter.tcl#9.methodlogy and goal setup

puts "######### methodlogy and goal setup #########"

source ${WORK_HOME}/scripts/set_methodology_and_goal.tcl#10.set rules

puts "######### set rules #########"

source ${WORK_HOME}/scripts/set_sg_lint_rules.tcl#11.run goal

puts "######### run goal #########"

run_goal#12.analyze results

puts "######### analyze results #########"

write_report goal_summary > $REPORT_PATH/$TOP_MODULE/goal_summary.rpt

write_report goal_setup > $REPORT_PATH/$TOP_MODULE/goal_setup.rpt

write_report moresimple > $REPORT_PATH/$TOP_MODULE/moresimple.rpt

write_report summary > $REPORT_PATH/$TOP_MODULE/summary.rpt

write_report waiver > $REPORT_PATH/$TOP_MODULE/waiver.rptputs "$REPORT_PATH/$TOP_MODULE/goal_summary.rpt"

puts "$REPORT_PATH/$TOP_MODULE/goal_setup.rpt"

puts "$REPORT_PATH/$TOP_MODULE/moresimple.rpt"

puts "$REPORT_PATH/$TOP_MODULE/summary.rpt"

puts "$REPORT_PATH/$TOP_MODULE/waiver.rpt"#14.save & close project

puts "######### save & close project #########"

save_project -force sg_lint.prj

close_project -force

#date

puts "######### Using follow command to open SG_Lint project #########"

puts "spyglass -project sg_lint.prj &"set_methodology_and_goal.tcl

set METHODOLOGY_TYPE initial_rtl

set GOAL_TYPE mandatory

if { $METHODOLOGY_TYPE == "initial_rtl" } {current_methodology $env(SPYGLASS_HOME)/GuideWare2.0/block/initial_rtlset regression_mandatory_list {lint/lint_rtl adv_lint/adv_lint_struct}set regression_optional_list {lint/design_audit lint/lint_functional_rtl}

} else {current_methodology $env(SPYGLASS_HOME)/GuideWare2.0/block/rtl_handoffset regression_mandatory_list {lint/lint_rtl adv_lint/adv_lint_verify}set regression_optional_list {lint/lint_functional_rtl lint/abstract}

}

append regression_all_list {regression_mandatory_list} {regression_optional_list}if { $GOAL_TYPE == "mandatory" } {current_goal Group_Run -goal ${regression_mandatory_list} -top $TOP_MODULE

} elseif { $GOAL_TYPE == "optional" } {current_goal Group_Run -goal ${regression_optional_list} -top $TOP_MODULE

} else {current_goal Group_Run -goal ${regression_all_list} -top $TOP_MODULE

}

unset regression_all_listset_option_and_parameter.tcl

#refer to 《SpyGlass_Explorer_UserGuide.pdf》

# ##################### set options #####################

#Use this design-read option to specify macro definitions in your Verilog analysis run.

set_option define {RD = 0}#Use this design-read option to specify a top-level module so that all design units instantiated directly

#or indirectly under this module are included in the scope of SpyGlass analysis.

set_option top $TOP_MODULE#Use this design-read option to enable or disable SystemVerilog

#compatibility mode. By default, this option is disabled.

set_option enableSV yes#Use this command to enable parsing of SystemVerilog constructs.

#By default, SpyGlass reports SystemVerilog constructs as syntax errors.

set_option enableSV09 yes#Use this command to specify the operating language for the current SpyGlass run.

set_option language_mode mixed#Use this command to specify a default waiver file for saving interactive

#waiver commands. If you do not specify a default waiver file by using this command, SpyGlass

#Explorer considers the <project-wdir>/<project_name>.awl file as the default waiver file.

set_option default_waiver_file $TOP_WAIVER_FILE#Disables flattening during the compile_design command in the sg_shell.

#Also disables flattening while opening a project, if the project was closed with a flattened view.

set_option designread_disable_flatten no#The default value of the enable_save_restore option is yes.

#Use this design-read option to view built-in messages during the restore

#run that were reported during the save run.

set_option enable_save_restore no#Use this design-read option to translate design attributes from SDC format

#to SGDC format. These attributes are then used during SpyGlass analysis.

set_option sdc2sgdc no#Use this command to print the waived messages in the waiver report when

#the -ip argument of the waive constraint is specified. By default, only

#the count of waived messages is reported in the waiver report.

set_option report_ip_waiver yes#If you set the force_gateslib_autocompile command to yes to

#automatically compile gate libraries, any criteria for re-compilation of gate

#libraries is not evaluated. In such cases, the specified .lib files are always

#compiled and these files overwrite the existing .sglib file present in the

#cache directory.

set_option force_gateslib_autocompile yes# ##################### set parameters #####################

#Specifies whether the related rules check the bit_width as per LRM.

#By default, the nocheckoverflow rule parameter is set to no, and the affected rules do not check the bit-width as per LRM.

#Lint: W116, W164a, W164b, W164c, W486, W110, W263, W362

set_parameter nocheckoverflow no#(Optional) Causes the CombLoop rule to proceed from enable pin to Q (output) pin of a latch, while detecting the combinational loop.

#By default, the enableE2Q rule parameter is unset and the CombLoop rule does not traverse through latches for locating combination loops.

set_parameter enableE2Q yes#The default value is no. Set this parameter toyes to use the automatically-generated clock information.

#NOTE: This is the parameter of SpyGlass CDC solution

set_parameter use_inferred_clocks yes#Specifies whether the STARC02-2.10.3.7 rule reports a violation for hexal, octal, and decimal based

#numbers if the width specified is greater than the actual bit-width of the based number.

#The STARC02-2.10.3.7 rule reports based numbers where the bit-width definition and specified value do not match.

#If the bit-width definition-part and the value part does not match like the examples below, it can easily lead to mistakes:

#a = 3'b11111111;

#a = 3'b11;

set_parameter ignore_based_width yes#Specifies whether the STARC-2.11.3.1 rule reports a violation for sequential block infer counter logic.

#By default, the value of the ignore_fsm_counter parameter is set to no and the STARC-2.11.3.1 rule reports a violation for sequential block infer

#counter logic.Set the value of this parameter to yes to ignore violations for such cases.This parameter is only applicable for Verilog.

#STARC-2.11.3.1 : Ensure that the sequential and combinational parts of an FSM description should be in separate always blocks. (Verilog)

#Use this rule to report detect the sequential and combinational parts of an FSM that are in the same always or sequential blocks.

set_parameter ignore_fsm_counter yes#(Optional) Specifies the maximum number of logic levels beyond which the LogicDepth rule should flag an error message.

set_parameter delaymax 250#Enables the W164a, W164b, W116, and W362 rules to report a violation for static expressions and non-static expressions that contain static

#expressions.By default, this parameter is set to no. In this case, the specified rules do not report a violation for static expressions and non-static #expressions that contain static expressions.

set_parameter check_static_value yes#Use this command to enable reporting of incremental messages so that you can compare results of a previously run goal with the current goal.

if { ![file exists ${WORK_HOME}/out/${TOP_MODULE}.vdb] } {set_goal_option report_incr_messages yes#Specifies path of previous Violation Database file for consideration in Incremental Modeset_goal_option old_vdbfile ${WORK_HOME}/out/${TOP_MODULE}.vdb

} else {set_goal_option report_incr_messages no

}

set_sg_lint_rules.tcl

# ########################### ignore rules ###########################

#The W446 rule flags output ports that are read in the module where they are set.

#Such models could lead to an unintended feedback path from the instantiating module in the post-synthesis simulation while this issue is not apparent

#in the pre-synthesis simulation. Such models are also not recommended for some test tools that need to handle inout ports specially (by attaching

#bus-holders, for example).

set_goal_option ignorerules {'W446'}#The W280 rule flags intra-assignment delays specified with nonblocking assignments.

#Such description is unlikely to correspond to the physical implementation. However, such description may be required to use a unit delay to avoid

#race conditions in simulation.

set_goal_option ignorerules {'W280'}set_goal_option ignorerules {'W11'}#Use this rule to report unregistered output from a top module./ Use this rule to report output ports in a module that are not driven by a flip-flop.

set_goal_option ignorerules {'RegOutputs'}#The CheckDelayTimescale-ML rule reports a violation if a delay is used in a module and no timescale units are specified using the 'timescale compiler directive.

set_goal_option ignorerules {'checkDelayTimescale-ML'}#The LogNMux rule reports multiplexer constructs in which log of the number of select input pins is greater than the specified number, that is, the logmux_max value that is 3 by default.

set_goal_option ignorerules {'LogNMux'}#The FlopDataConstant rule reports flip-flop instances for which the data pin is tied to a constant value.

set_goal_option ignorerules {'FlopDataConstant'}#The sim_race01 rule reports signals that are assigned and used within the same module in the same simulation cycle.

#This rule detects signals that are in two always constructs in the same module or one always construct and one continuous

#assignment statement in the same module.

set_goal_option ignorerules {'sim_race01'}#The ArrayIndex rule reports violation for the bus signals that are declared with the low-order bit first,

#that is, it reports those multi-bit signals that do not follow the specified bit-order specification convention.

set_goal_option ignorerules {'ArrayIndex'}#The DisabledAnd rule reports AND or NAND gate instances for which at least one input is tied low.

#Therefore, these gate instances are effectively disabled.

set_goal_option ignorerules {'DisabledAnd'}

#The DisabledOr rule reports OR or NOR type gate instances for which at least one input is tied high.

#Therefore, these gate instances are effectively disabled.

set_goal_option ignorerules {'DisabledOr'}#The MuxSelConst rule reports the MUX gate instances for which the select pin is tied to a constant value.

set_goal_option ignorerules {'MuxSelConst'}#The DiffTimescaleUsed-ML rule flags different timescales used in the design.If different timescales are used in different modules of the design,

#then in a single simulation, delay values in one module will be different from that of other module.

set_goal_option ignorerules {'DiffTimescaleUsed-ML'}#The LogicDepth rule reports logic paths, which originate or terminate at flip-flops or primary pins,

#where the number of delay levels exceeds the specified value. This rule performs a simplified version of the critical path analysis.

set_goal_option ignorerules {'LogicDepth'}# ########################### change the rules' level ###########################

#The W210 rule flags a violation for module or interface instances with unconnected ports.

#The W210 rule flags message only when number of terminals are less than the number of ports.

#The W210 rule ignores ports that are intentionally kept open (by passing extra comma [Verilog] or by connecting them to open [VHDL]).

#If any of the unconnected ports are inputs or inouts, this is an error. It may or may not be an error if the unconnected ports are outputs.

set_option overloadrules W210+severity=Error#The W287a rule flags module or gate instances where nets connected to input ports are not driven and the instance input which are not connected.

set_option overloadrules W287a+severity=Error#The W480 rule reports violation for those for constructs in which the loop index variable evaluates to a non-integer.

set_option overloadrules W480+severity=Error#The W213 rule reports PLI tasks and functions used in the design.

set_option overloadrules W213+severity=Error#Reports constant assignments that are X-extended

set_option overloadrules W342+severity=Error#The STARC05-1.3.1.3 rule reports violation for asynchronous reset/preset signals that are used as non-reset/preset signals or as synchronous reset/preset signals.

set_option overloadrules STARC05-1.3.1.3+severity=Error#The STARC05-2.1.4.5 rule reports violation for logical operators that are used on vector operands.

#No violation is reported for logical negation on integer variables.

set_option overloadrules STARC05-2.1.4.5+severity=Error#Bit-width of operands of a logical operator must match. (Verilog)

#The STARC05-2.10.3.2a rule flags bit-width mismatches between operand expressions of logical operations.

#Bit-width mismatch between operands of a logical operation may lead to incorrect results.

#The STARC05-2.10.3.2a rule does not flag a relational operation if an integer constant is used as one of the operands and the width of that constant is less than or equal to the width of the other operand.

set_option overloadrules STARC05-2.10.3.2a+severity=Error#Do not mix descriptions of flip-flops with asynchronous reset and flip-flops without asynchronous reset in the same process/always block

#The STARC05-2.3.6.1 rule flags those always or process constructs that have a flip-flop description with a reset line and another flip-flop description without a reset line.

#The STARC05-2.3.6.1 rule does not report violation for hanging flip-flops.

#Mixing the descriptions of flip-flops with and without reset lines in the same always or process construct has the following issues:

#Such description may be confusing and difficult to debug

#Such description may also cause problems for synthesis tools.

set_option overloadrules STARC05-2.3.6.1+severity=Error#The IntReset rule reports internally generated asynchronous resets in the design.

set_option overloadrules IntReset+severity=Error#The DisallowCaseX-ML rule reports violation for casex constructs used in the design.

set_option overloadrules DisallowCaseX-ML+severity=Error#The W443 rule flags based numbers that contain the unknown value character (X).

#The unknown value character (X) has no physical counterpart and may lead to a mismatch between pre- and post-synthesis simulation.

#By default, the W443 rule does not check the presence of X value in the default statement of the case construct in Verilog designs.

#Use the strict rule parameter to check in the default statement also.

#For Verilog, no rule checking is done for unused macro definitions and unused parameters.

set_option overloadrules W443+severity=Error#A signal is included in the sensitivity list of a combinational always block but none of its bits are read in that block (Verilog)

#The W456a rule flags signals that are in the sensitivity list of a combinational always construct but are never read in the construct.

set_option overloadrules W456a+severity=Error#Do not connect buses in reverse order

#The W156 rule flags reverse connected buses.

#Making reversed connections (for example, 15:0 connected to 0:15) is legal but bad design practice and may represent an error.

#One exception (which can be handled with a waiver) is in making a big-endian/little-endian choice in connecting to a processor bus port.

set_option overloadrules W156+severity=Error#Reports a case expression width that does not match case select expression width

#The W263 rule reports the case clause labels whose widths do not match the width of the corresponding case construct selector.

set_option overloadrules W263+severity=Error

set_top_module.tcl

#get top module from environment

if { [info exist $env(TOP_MODULE)] } {set TOP_MODULE $env(TOP_MODULE)

} else {set TOP_MODULE async_fifo_mem

}

puts "TOP_MODULE = $TOP_MODULE"set_top_waiver.tcl

#set top waiver file

set TOP_WAIVER_FILE ${WORK_HOME}/waiver/${TOP_MODULE}.awl

if { ![file exists $TOP_WAIVER_FILE] } {exec touch $TOP_WAIVER_FILE

}

执行脚本

1、cd /home/xxx/chip/eda_test

2、source SourceMe

3、cd 03_lint

4、sg_shell < scripts/sg_lint.tcl | tee sg_lint_screen.log

5、spyglass -project sg_lint &

这篇关于【脚本篇】---spyglass lint脚本的文章就介绍到这儿,希望我们推荐的文章对编程师们有所帮助!