armv9专题

【ARMv8/ARMv9 硬件加速系列 2.3 -- ARM NEON 的四舍五入指令】

文章目录 NEON 的四舍五入SRSHLR 指令格式SRSHLR 操作说明SRSHLR 示例解释 NEON 的四舍五入 SRSHR指令是ARMv8 NEON SIMD指令集中的一部分,用于对向量中的每个元素进行向右的算术位移操作,并将结果四舍五入。SRSHR指令的全称是Signed Rounding Shift Right,适用于带符号的整数。这个指令对于进行数据尺度缩小、平

【ARMv8/ARMv9 硬件加速系列 2.2 -- ARM NEON 的加减乘除(左移右移)运算】

文章目录 NEON 加减乘除 NEON 加减乘除 下面代码是使用ARMv8汇编语言对向量寄存器v0-v31执行加、减、乘以及左移和右移操作的示例。 ARMv8的SIMD指令集允许对向量寄存器中的多个数据进行并行操作。v0和v1加载数据,对它们进行加、减和乘,左移和右移操作。最后,我们会将结果存储到内存地址0xb0000000处, 方便观察结果。 func neon_calc_

【ARMv8/ARMv9 硬件加速系列 4.1 -- Cryptographic Extension 解密指令 AESD】

文章目录 Cryptographic Extension 解密指令 AESDAESD 指令详解AES 工作原理AESD 使用条件 AESD 示例场景 Cryptographic Extension 解密指令 AESD ARMv9架构引入了对先进加密标准(AES)操作的改进和加速,AESD指令是这些改进之一,专门用于AES解密操作。这个指令通过对数据执行一系列变换,实现了AES

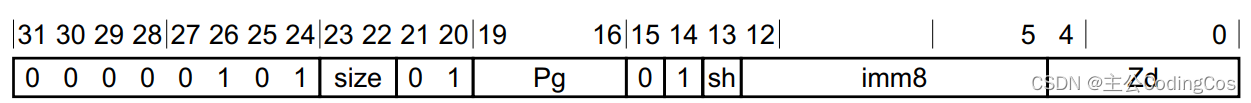

【ARMv8/ARMv9 硬件加速系列 3.4 -- SVE 复制指令CPY 使用介绍】

文章目录 SVE 复制指令CPYSVE 指令格式SVE 使用语法SVE CPY 使用示例SVE CPY 小结 SVE 复制指令CPY CPY <Zd>.<T>, <Pg>/M, #<imm>{, <shift>} cpy 指令在 ARMv9 的

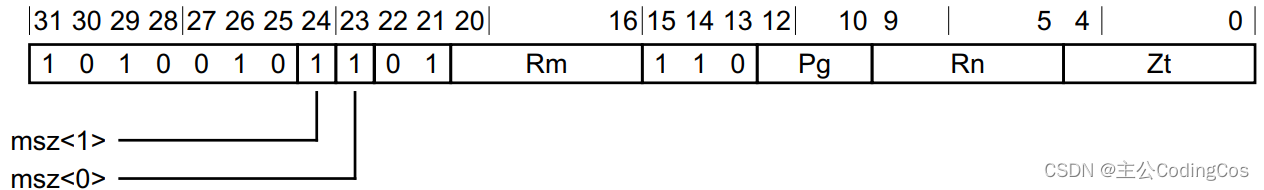

【ARMv8/ARMv9 硬件加速系列 3.3 -- SVE LD2D 和 ST2D 使用介绍】

文章目录 SVE 多向量操作LD2D(加载)LD2D 操作说明LD2D 使用举例ST2D(存储)ST2D 使用举例ST2D 存储示例代码 ld2d 和 st2d 小结 SVE 多向量操作 在ARMv8/9的SVE (Scalable Vector Extension) 指令集中,st2d和ld2d指令用于向量化的存储和加载操作,具体地,它们允许同时对两个向量寄存器进行连续的存

【ARMv8/ARMv9 硬件加速系列 3 -- SVE 硬件加速向量运算 1】

文章目录 SVE 使用介绍SVE 特点SVE2 特点 SVE 寄存器扩展的向量寄存器可扩展的谓词寄存器.d 与 .b 后缀的区别举例介绍使用 .d 后缀进行64位元素操作使用 .b 后缀进行8位元素操作 ptrue 指令小结 FFR 寄存器 SVE 使用介绍 前面文章:【ARMv8/ARMv9 硬件加速系列 1 – SVE | NEON | SIMD | VFP | MVE

【ARMv8/ARMv9 硬件加速系列 1 -- SVE | NEON | SIMD | VFP | MVE | MPE 基础介绍】

文章目录 ARM 扩展功能介绍VFP (Vector Floating Point)SIMD (Single Instruction, Multiple Data)NEONSVE (Scalable Vector Extension)SME (Scalable Matrix Extension)CME (Compute Matrix Engine)MVE (M-profile Vector

【ARMv9 DSU-120 系列 9.1 -- ROM tables】

请阅读【Arm® DynamIQ™ Shared Unit-120 专栏 】 文章目录 DSU-120 ROM tablesDebug system address map核心 <n> ROM表集群ELA核心ELA组件调试APB系统地址映射: DSU-120 ROM tables DSU-120(DynamIQ™共享单元-120)具有三种不同类型的ROM表。这些ROM表

【ARMv9 DSU-120 系列 4.1 -- Utility bus 详细介绍 2】

文章目录 ARM DSU-120DSU-120 Utiity BusCluster and core PPUPPU寄存器的访问性PPU寄存器的作用 系统组件基地址 ARM DSU-120 DSU-120 Utiity Bus 在ARMv9架构中,DSU-120(Dynamic Shared Unit 120)是一个关键组件,用于管理核心和系统组件之间的通信与协作。某些系统

【ARMv9 DSU-120 系列 -- CHI Interface】

文章目录 DSU-120 CHI BUSAddress Target Groups配置步骤映射和管理 Hashing for CHI transaction distribution散列过程和地址目标组识别散列函数定义两个地址目标组的散列四个地址目标组的散列八个地址目标组的散列 DSU-120 CHI BUS DSU-120(DynamIQ™共享单元-120)在构建时配置期间

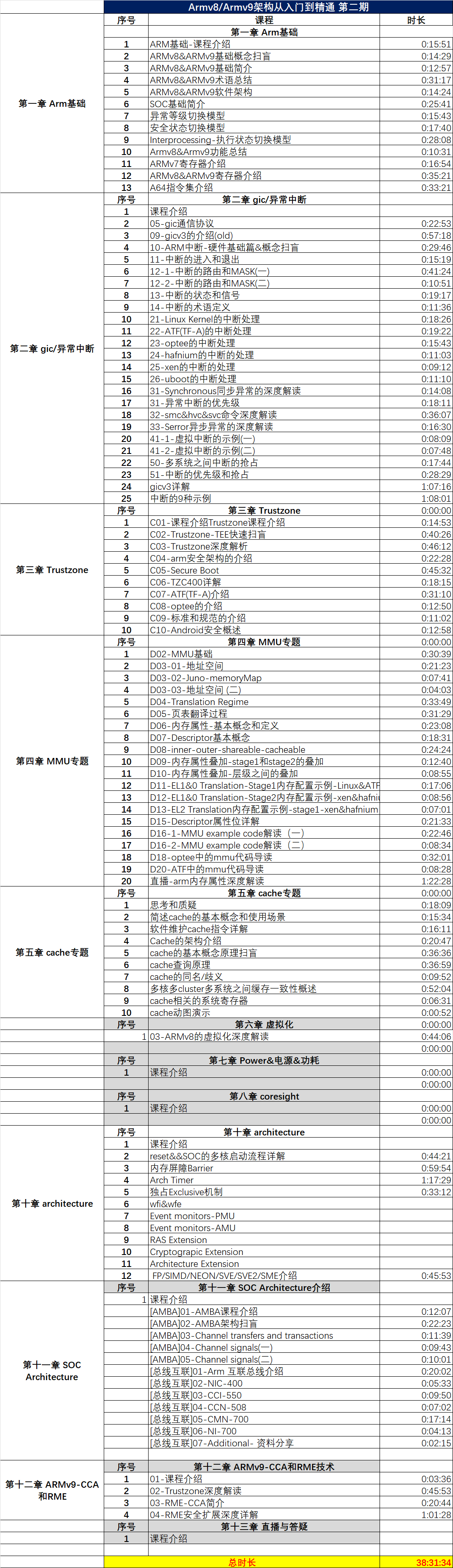

【置顶】ARMv8/ARMv9架构入门到精通-[目录]--backup-20240424

快速链接: . 👉👉👉 个人博客笔记导读目录(全部) 👈👈👈 付费专栏-付费课程 【购买须知】: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈联系方式-加入交流群 ----联系方式-加入交流群 目录 1、【armv8/armv9基础】2、【mmu/cache】3、【gic专题、异常专题、中断专题】4、【Trustzone & 安全架构】

【ARMv9 DSU-120 系列 -- Mapping for address target groups to CHI bus master ports】

文章目录 Mapping for address target groups to CHI bus master ports映射决定过程示例 CHI id bit setting Mapping for address target groups to CHI bus master ports 在DSU-120(DynamIQ™共享单元-120)中,地址目标组与总线主端口之间的

【ARMv9 DSU-120 系列 3 -- 系统控制寄存器】

文章目录 DSU-120 系统控制寄存器系统控制寄存器的访问方式Cluster 通用系统控制寄存器寄存器重置值 Generic System Control registers summaryCluster Configuration Register DSU-120 系统控制寄存器 在ARMv9架构中,DSU-120(DynamIQ™ Shared Unit-120)是一个

00-armv8/armv9中断系列详解-序言

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 1、序言 带着问题去学习,关于异常/中断的一些思考: (1)、在如下的一个大系统种,cpu正在optee os中运行,突然来了一个想给Linux Kernel处理的中断(如一个蓝牙中断),那么此时的软硬件流程是怎样的? (2)、在上述的大系统中,你的Linux Kernel、optee os、hyper

深入理解Armv9 DSU-110中的L3 cache

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 关键词: DynamIQ cluster、DSU-110、DSU-120、DSU、cache、mmu、缓存、高速缓存、内存管理、MPAM 思考: 1、L1、L2、L3 cache的替换策略是怎样的? 2、什么类型的内存永远不会进L3 cache? 3、L3 cache一般都是多大? 4、L3 cache

Armv9 Cortex-A720的L1 memory system 和 L1 Cache

快速链接: . 👉👉👉 个人博客笔记导读目录(全部) 👈👈👈 付费专栏-付费课程 【购买须知】: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈联系方式-加入交流群 ----联系方式-加入交流群 思考: L1 System memory和L1 Cache是什么关系?L1指令cache禁用时,指令cache就真的不会缓存了吗&#x

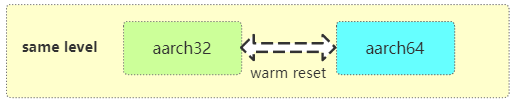

armv8/armv9不同特权程序之间的跳转模型

目录 1、前言2、4个特权等级/4个安全状态之间的跳转模型3、启动时镜像之间的跳转模型4、runtime程序之间的跳转模型推荐 本文转自 周贺贺,baron,代码改变世界ctw,Arm精选, armv8/armv9,trustzone/tee,secureboot,资深安全架构专家,11年手机安全/SOC底层安全开发经验。擅长trustzone/tee安全产品的设计和开发。

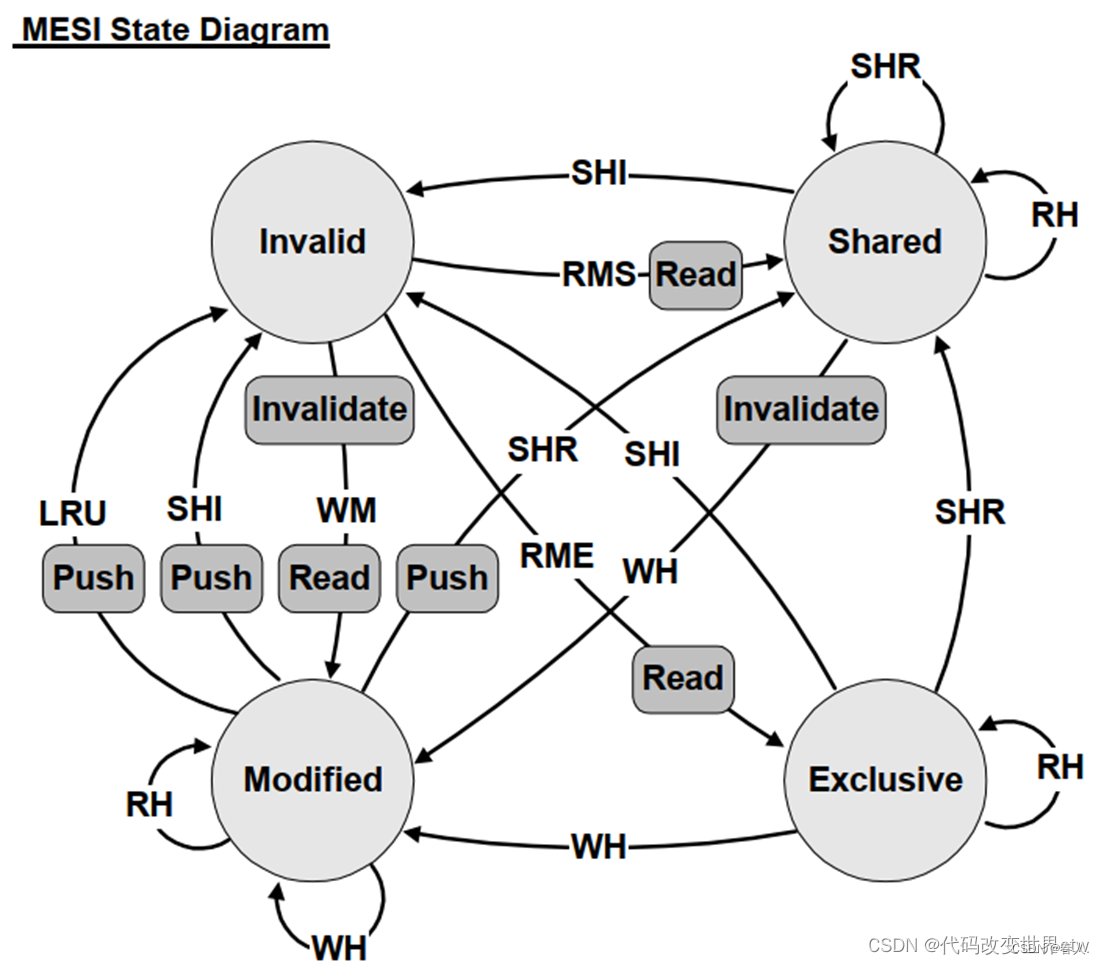

深度学习armv8/armv9 cache的原理

文章目录 1、为什么要用cache?2、背景:架构的变化?2、cache的层级关系 ––big.LITTLE架构(A53为例)3、cache的层级关系 –-- DynamIQ架构(A76为例)4、DSU / L3 cache5、L1/L2/L3 cache都是多大呢6、cache相关的术语介绍7、cache的分配策略(alocation,write-through, write-back

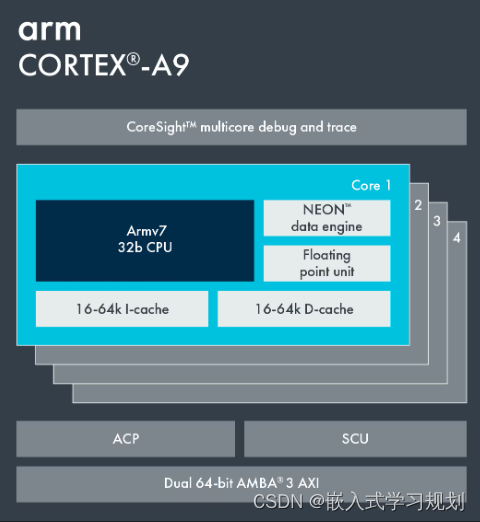

ARM9、Armv9、A9有什么区别?

1、Arm9是ARM 25年前的产品,属于armv4架构了。 著名的S3C2440开发板,就是使用的二十三年以前的ARM920T Core 现在网络上依然保持着大量的讲述arm9的文章或视频,也请各位千万不要被带偏了。 学这玩意要能找到工作,我直播吃屎。 2、A9, 其实就是cortex-A9,它是Armv7架构下的一个微架构,或者说是一个具体的core IP… 它是2008年的一个产品

2024最新:Armv8/Armv9架构从入门到精通二期-课程介绍

【学习对象】 [行业]:汽车电子、手机、服务器、云计算、物联网、人工智能; [人群]:本科/研究生/博士、初级工程师、中级工程师、资深工程师、行业大佬,即适合小白入门,也适合大佬查缺补漏; [方向]:电子/计算机专业、芯片架构设计、芯片底层软件、芯片验证、BSP软件开发、内核驱动开发、固件开发、bootrom/bootloader开发、安全、虚拟化、大系统开发等; [行业链]:主机厂、OEM

深入理解Armv9 DSU-110中的L3 cache

快速链接: . 👉👉👉 个人博客笔记导读目录(全部) 👈👈👈 付费专栏-付费课程 【购买须知】: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈联系方式-加入交流群 ----联系方式-加入交流群 关键词: DynamIQ cluster、DSU-110、DSU-120、DSU、cache、mmu、缓存、高速缓存、内存管理、MPAM 思考: 1、

Armv8/Armv9从入门到精通-课程介绍

通知,Arm二期,咱们也有大合集PDF了,共计1587页,还未完成,后续持续更新和优化中。为了方便大家阅读、探讨、做笔记,特意整了此合集PPT,为了增加标签目录,还特意开了福兮阅读器会员。 以下是此课程的介绍: 你将收获 1、全体系的掌握ARMv8/ARMv9的核心知识点(ARM基础、异常中断GIC、MMU/Cache、architecture…); 2、掌握ARM架构、掌握SOC架构、掌

Armv8/Armv9 MMU学习的28问,你能回答上来几个

01、一个大系统中有多少个MMU ? 一般情况下:一个core里面有一个MMU,8个core就是8个MMU; 除了Arm core里有MMU之外,在SOC中,还会诸多个SMMU,具体看SOC的架构设计。 02、一个ARM Core中有多少个Translation regime? 在Armv8/Armv9架构中(不考虑CCA/RME安全扩展),至少有9类Translation regime,注

![【置顶】ARMv8/ARMv9架构入门到精通-[目录]--backup-20240424](https://img-blog.csdnimg.cn/998b5eef7617440ebc92d3cfa9581b0e.gif)