高速专题

畅游5G高速网络:联发科集成Wi-Fi6E与蓝牙5.2的系统级单芯片MT7922

这周末,除非外面下钞票,否则谁也拦不住我玩《黑神话悟空》(附:两款可以玩转悟空的显卡推荐) IPBrain平台君 集成电路大数据平台 2024年09月03日 17:28 北京 联发科一直以创新技术追赶市场需求…… “不努力向前游就会被海浪拍回岸边…” 芯片设计公司产品层出不穷,想要站稳脚根只有不断创新其技术和适应市场的需求。来自台湾地区的联发科技,自

Altera FPGA与高速ADS4249和DAC3482的LVDS接口设计

引言:本文以TI的ADS4249(ADC)和DAC3482(DAC)之间的接口为例,介绍Altera FPGA与ADC/DAC之间的DDR LVDS接口设计以及时序约束详细设计。本文介绍的实例可方便扩展到具有类似接口格式的其他高速数据转换器设计。 1.概述 ADS4249是一款双通道、14位、250MSPS ADC,具有双总线、字节级数字接口。ADS4249接口示例适用于许多TI高速ADC,包

FPGA与高速ADC接口简介

引言:本文介绍FPGA与高速ADC接口方式和标准以及JESD204与FPGA高速串行接口。 1. 高速ADC与处理器互联需要权衡的因素 如图1所示,ADC模数转换器可以与微控制器、DSP、FPGA以及ASIC均可以实现互联,在进行选择时,需要考虑以下因素:设计要求的信号处理和转换器性能、开发成本、IO接口速率、开发的便利性以及器件材料成本。 图1:ADC与处理器互联需要权衡的因素 2.

FPGA与高速ADC LVDS数据接口设计考虑

引言:本文描述了ADC和FPGA之间LVDS接口设计需要考虑的因素,包括LVDS数据标准、LVDS接口数据时序违例解决方法以及硬件设计要点。 1. LVDS简介 1.1 什么是LVDS? LVDS(低压差分信号)标准是业界流行的差分数据传输标准,它是双线、低摆幅差分信号。其优点包括以下几点: •低电源电压运行 •高速数据传输 •良好的共模噪声抑制 •噪音产生更少 图1:LV

飞速(FS)400G SR4光模块:高速网络应用新选择

飞速(FS)在2024年5月11日推出的400G SR4 QSFP-DD光模块,标志着信息通信技术(ICT)产品及解决方案领域的一个重要进步。这一新产品的推出,将对高速网络的性能和传输效率产生深远的影响。 为满足数据中心和网络基础设施对更高带宽和更快数据传输速率不断增长的需求,400G SR4 QSFP-DD光模块应运而生。随着云计算、高性能计算和大数据分析等技术的快速发展,现有网络框架面临着数

Cadence高速板设计技巧(全志H3)[四]

HDMI常用的ESD器件: 可以看到一个器件可以做两路差分线的TVS防护: 按W键移动会把导线直接移走,这样显然是不行的: cadence中导线调节用的是快捷键e: 因此,虽然在某些场合下 eMMC 被称为 ROM,但从技术和功能角度来看,eMMC 并不属于传统意义上的 ROM,而是一种可读写的闪存存储器。 BUCK电路的三个重要回路:输入回路,输出回路,反馈

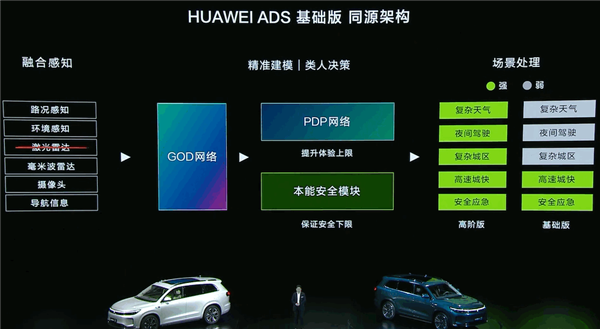

不想下牌桌!1500元以内就能拿下高速NOA,巨头狂卷“价格战”

在车企降本、智能化普及的双重压力之下,以高速NOA为门槛的高阶智驾赛道,正在席卷一场残酷的价格战。从华为、大疆、Momenta,再到数家中国本土供应商。 如今,传统外资Tier1也在下场拼杀。 本周,采埃孚官方重磅发布高速公路自动驾驶领航辅助系统RFA(Route Following Assist),基于不同主机厂需求可以进行硬件的适配调整,最低可下探至1500元以内的高速NOA解决方

RocketMQ:高速消息中间件的秘密武器

人不走空 🌈个人主页:人不走空 💖系列专栏:算法专题 ⏰诗词歌赋:斯是陋室,惟吾德馨 关于RocketMQ的详细图表,包含了Producer、Consumer、Broker和NameSe

电商企业借助精益六西格玛培训提升人岗匹配率 ———从高速增长到精细管理的破局之道

在全球电商行业的狂飙突进中,中国电商企业无疑已站上了世界舞台的中央。然而,在蓬勃发展的背后,越来越多的企业却陷入了增长的泥潭:人岗匹配率低下导致运营效率低,资产周转率不理想拖累了资金的流动性。面对这些问题,精益六西格玛(Lean Six Sigma)作为一种成熟的管理工具,被越来越多的电商企业视为突破瓶颈的利器。然而,如何将这一复杂的管理方法与电商业务的独特特性结合起来,切实提升人岗匹配率,从而实

AD9162数据链路lanes与FPGA高速BANK引脚交叉相连导致vivado编译失败

问题概述 对AD9162芯片进行功能开发时,发现AD9162的链路lanes与FPGA的高速BANK引脚存在交叉相连的情况,按照实际的引脚连接关系进行约束后,vivado编译失败。 问题阐述及原因分析 问题详情阐述 板卡对AD9162芯片进行功能开发时,发现硬件电路的设计结果存在AD9162数据链路与FPGA高速BANK引脚交叉相连的问题,示意图如图3‑1,若根据图示的引脚连接关系进行

西安电子高速PCB学习(五)

感抗(Inductive Reactance)和容抗(Capacitive Reactance)是电感和电容在交流电路中对电流产生阻碍的特性。这两个概念源于交流电路中,电感和电容对交流电流的相应反应。 感抗(Inductive Reactance) 感抗是由电感(如电感线圈)在交流电路中引起的电抗。由于电感的存在,电流在通过电感器时会滞后于电压,从而表现出对交流电流的阻碍,阻碍滤波高频。 感

西安电子高速PCB学习(四)

注意了,信号发生器的不同通路不能并联使用,示波器的信号通路不能并联电源使用,不同信号发生器不能并联使用: 严禁多个电容共用过孔: 多个电容并联时,小容量的电容应更靠近芯片电源引脚,主要原因是为了优化电源去耦性能和滤波效果。具体原因如下: 高频特性更好:小容量电容(如0.1µF或0.01µF)的高频特性比大容量电容(如10µF或100µF)更好,具有较低的等效

西安电子高速PCB课件学习(一)

在放大器电路中,“自激”或“啸叫”通常指的是一种不希望发生的现象,即电路在没有输入信号的情况下,开始产生并放大自身的信号,这些信号会以高频或低频的振荡形式出现。以下是详细解释: ### 1. **自激振荡(Self-Oscillation)**: - **定义**: 自激振荡是指放大器由于反馈不当,产生不受控制的周期性振荡。这种振荡并非来自外部信号,而是由于电路本身的条件(如寄生电容、

飞睿智能UWB定位手环芯片模块,高速无线传输超宽带uwb定位技术,创新手环科技潮流

在数字化时代的浪潮中,我们每天都在享受着科技带来的便捷和惊喜。其中,定位技术作为现代科技的重要分支,已经深入我们生活的每一个角落。从智能手机导航到共享单车,从无人驾驶到物流追踪,定位技术都在默默发挥着它的作用。而今天,我要向大家介绍的,是一款具有创新性意义的定位技术——UWB(Ultra-Wideband,超宽带)定位手环芯片模块。 一、什么是UWB定位手环芯片模块? UWB定位手环芯片模

高速异地组网怎么办理?

在当今信息化时代,跨地域的远程办公、远程教育、远程医疗等需求越来越多。而高速异地组网作为一种解决不同地区之间快速组建局域网的方法,被广泛应用。本文将介绍一款异地组网内网穿透产品——【天联】,并提供其办理流程。 【天联】组网是什么? 【天联】组网是一款异地组网内网穿透产品,由北京金万维科技有限公司自主研发,解决了不同地区电脑与电脑、设备与设备、电脑与设备之间的信息远程通信问题。【天联】操作简单,

解析卷积的高速计算中的细节,一步步代码带你飞

点击上方“AI公园”,关注公众号,选择加“星标“或“置顶” 作者:Manas Sahni 编译:ronghuaiyang 导读 卷积是深度学习中的基础运算,那么卷积运算是如何加速到这么快的呢,掰开揉碎了给你看。 在我不太破旧的笔记本电脑CPU上,使用TensorFlow这样的库,我可以(最多)在10-100毫秒内运行大多数常见的CNN模型。在2019年,即使是智能手机也能在不到半

ADOP带你了解:数据中心的高速互联解决方案

随着大语言模型和AIGC的飞速发展,数据中心对于高速、高可靠性的网络连接需求日益增长。ADOP系列产品正是在这样的背景下应运而生,为现代数据中心提供了全面的连接解决方案。 ADOP系列产品概览 ADOP系列产品旨在为云、高性能计算、Web 2.0、企业、电信、存储和人工智能、数据中心等多个应用场景提供高性能的以太网产品。以下是ADOP系列产品的一些主要特点: 产品范围:ADOP系列包括10/

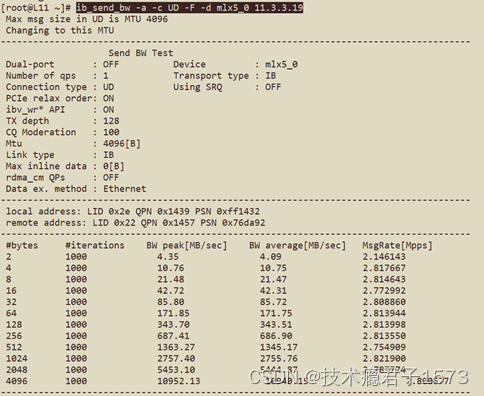

Mellanoxnvidia ib高速网络常用命令总结

1.spci:检查本地的pci设备。示例:lspci| grep -i mell 2.ofed_info:检测ofed驱动版本。示例:ofed_info-s 3.ibstat:查看本机的ib网卡状态。 4.mst:mellnoax软件管理工具。用来生成IB设备描述符。提供给其他命令使用。示例:mststart 5.mlnx_perf :可以查看端口的收发流量。 -i:选项

虹科免拆诊断案例 | 15款马自达3偶发高速CAN网络故障

CAN总线大家都不陌生,遇到这类故障,我们第一反应可能是用万用表测一下电压,看看存不存在短路、断路等问题。不过,使用万用表测得的电压值只是CAN总线上的平均电压,是一个大概的数值,并不能反映真实的CAN总线信号变化。如果想要更准确的信息,还是需要使用示波器来获取总线波形。 这里分享一个典型的总线故障波形,捕捉波形用的工具都是虹科Pico汽车示波器,软件为Picoscope6。 故障车是20

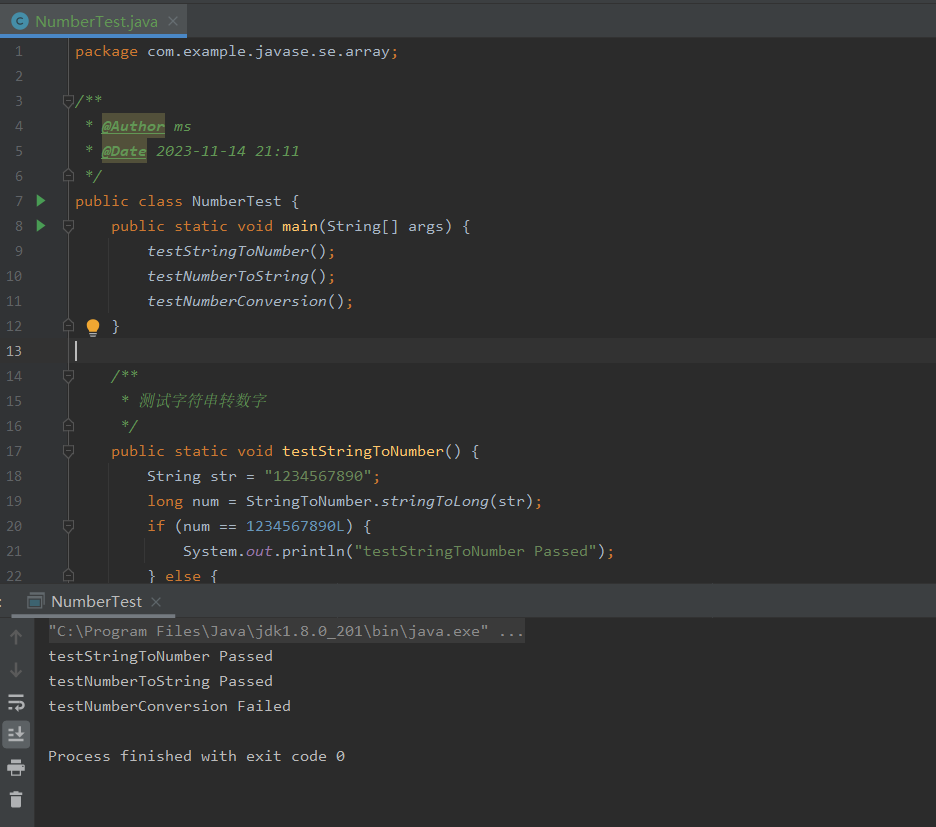

如何用Java SE数组实现高速的数字转换功能

哈喽,各位小伙伴们,你们好呀,我是喵手。运营社区:C站/掘金/腾讯云;欢迎大家常来逛逛 今天我要给大家分享一些自己日常学习到的一些知识点,并以文字的形式跟大家一起交流,互相学习,一个人虽可以走的更快,但一群人可以走的更远。 我是一名后端开发爱好者,工作日常接触到最多的就是Java语言啦,所以我都尽量抽业余时间把自己所学到所会的,通过文章的形式进行输出,希望以这种方式帮助到更多的初

STM32 | 基于 HAL 库实现 DMA 驱动 GPIO 高速翻转

项目中有一款点阵式液晶驱动芯片,需要用 IO 口翻转来实现高速串转并传输,主控芯片为 STM32F103RCT6。如果直接采用库函数进行IO的翻转不仅速度上满足不了要求,还会占用大量时间影响性能,导致时序上的错误。DMA可以在没有控制器的干预下进行数据的传输,因此决定采用DMA方式来驱动IO。本文以 HAL 库实现 DMA 驱动 GPIO 高速翻转为例说明DMA的配置过程,当然也可以改变 dma_

理解CA-IS3050G高速CAN收发器的CANH和CANL的电压

CA-IS3050G高速CAN收发器符合ISO 11898-2物理层标准。 1、CANH和CANL的电压之和为5V,下图是CA-IS3050G的高速CAN收发器参数,分析如下: 1)、总线输出显性电压 2.75V < VCANH <4.5V,负载为60Ω,CANH电压典型值为3.4V 0.5V < VCANL < 2.25V 通过交叉相加,我们发现: 2.75 + 2.25 =

基于GTX的64B66B编码IP生成(高速收发器二十)

点击进入高速收发器系列文章导航界面 1、配置GTX IP 相关参数 前文讲解了64B66B编码解码原理,以及GTX IP实现64B66B编解码的相关信号组成,本文生成64B66B编码的GTX IP。 首先如下图所示,需要对GTX共享逻辑进行设置,为了便于扩展,与8B10B编码一致,将共享逻辑放在IP外部的示例工程中。 图1 设置“GT Selection”界面

不同高速协议接口之间共享时钟

文章目录 前言1、万兆网给8B10B PHY共享2、8B10B PHY给万兆网共享3、综合实现4、总结4.1、上板验证4.1.1、第一路数据:万兆网4.1.2、第二路数据:8B10B PHY 前言 一个GT BANK有四个GT channel,他们之间是可以共享同一个QPLL输出参考时钟,之前的实验当中,我都是同样的工程例化多个channel进行时钟共享,这次在做一个BANK

国产光耦-双通道15 MBd高速光耦ICPL-075L

光电器件根据传输速率的不同可以分为普通光耦和高速光耦;高速光耦是一种数字隔离器;它的结构由光敏二极管和放大驱动电路组成;具有高速传输的特点,可以在高速数据传输时,确保信号的稳定性和可靠性。 由工采网代理的ICPL-075L是一款双通道15 MBd高速数字光耦合器,针对全双工工业通信应用进行了优化;采用最新的CMOS集成电路技术,以极低的功耗实现卓越的性能;在传输数据时,它可以同时传输两个

![Cadence高速板设计技巧(全志H3)[四]](https://i-blog.csdnimg.cn/direct/27edc442fdb84815bc44f79709e3fb86.png)