小梅哥专题

【IC设计】Verilog线性序列机点灯案例(三)(小梅哥课程)

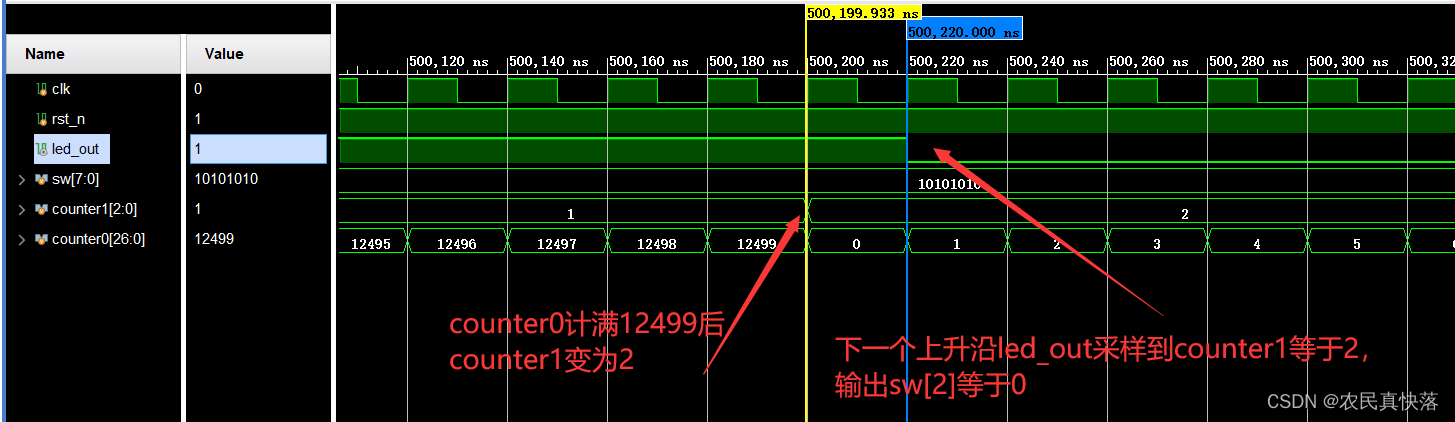

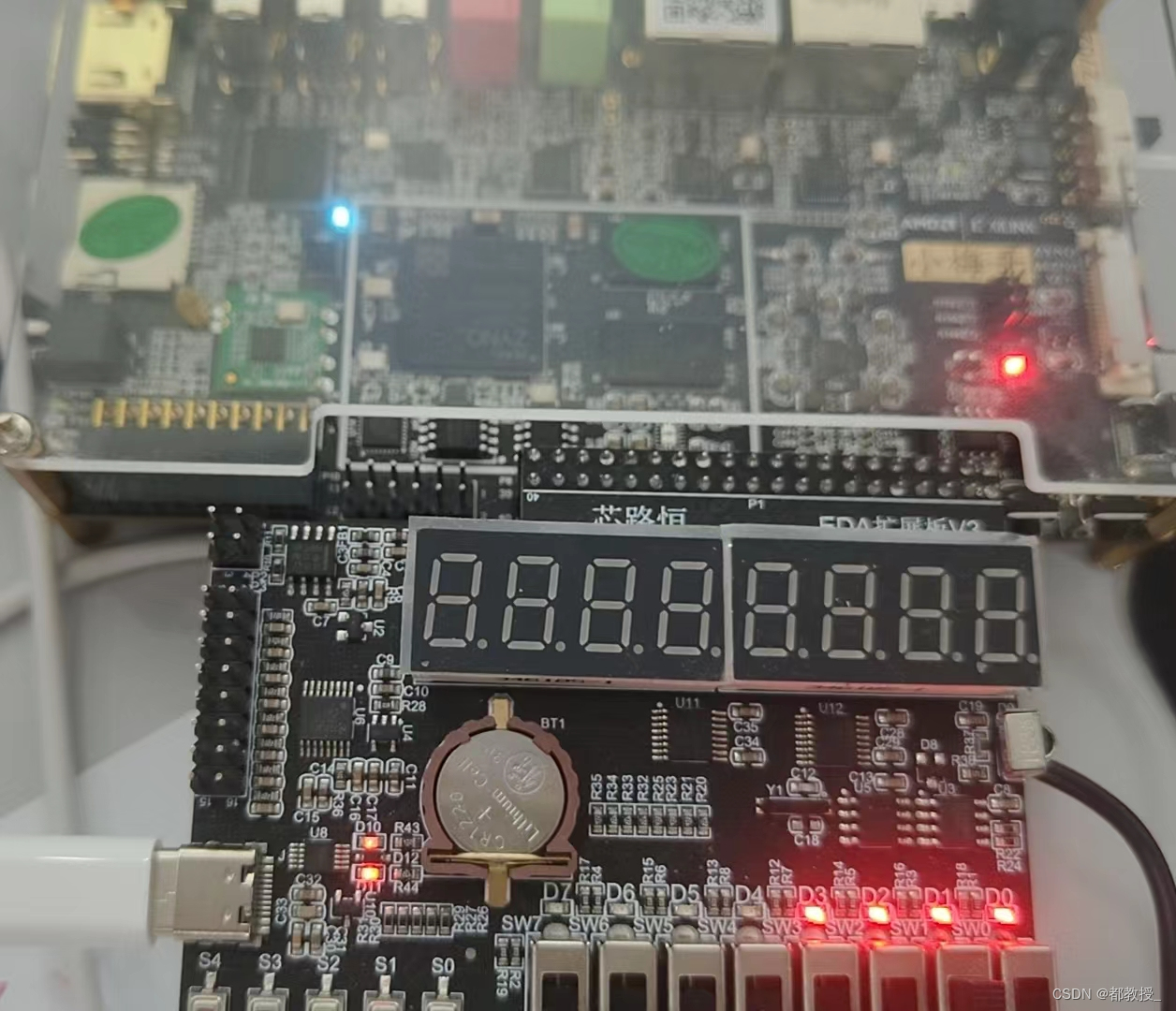

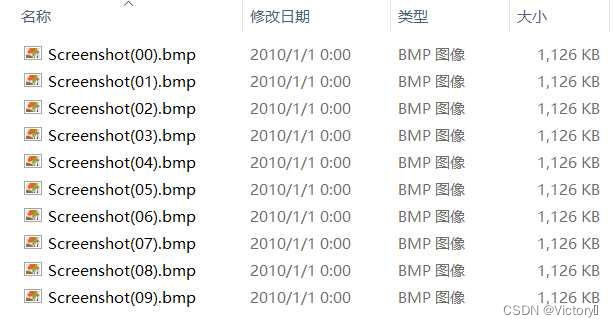

声明:案例和代码来自小梅哥课程,本人仅对知识点做做笔记,如有学习需要请支持官方正版。 文章目录 该系列目录设计目标设计思路RTL及Testbench代码RTL代码Testbench代码 仿真结果上板视频 该系列目录 Verilog线性序列机点灯案例(一)(小梅哥课程) Verilog线性序列机点灯案例(二)(小梅哥课程) 设计目标 使用8个拨码开关控制一个LED灯,每

小梅哥Xilinx FPGA学习笔记18——专用时钟电路 PLL与时钟向导 IP

目录 一:IP核简介(具体可参考野火FPGA文档) 二: 章节导读 三:PLL电路原理 3.1 PLL基本实现框图 3.2 PLL倍频实现 3.3 PLL分频实现 四: 基于 PLL 的多时钟 LED 驱动设计 4.1 配置 Clocking Wizard 核 4.2 led 闪烁控制 4.2.1 LED闪烁代码设计 4.3 顶层模块代码设计 4.4 仿真测试文件 4.5

小梅哥Xilinx FPGA学习笔记22——ip核之FIFO

目录 一:章节说明 1.1 FIFO IP简介 1.2 FIFO Generato IP 核信号框图 1.3 实验任务 二:FIFO 写模块设计 2.1 简介 2.2 模块框图 2.3 模块端口与功能描述 2.4 写模块代码 三 FIFO 读模块设计 3.1 简介 3.2 模块框图 3.3 模块端口与功能描述 3.4 读模块代码 四: 顶层模块设计 4

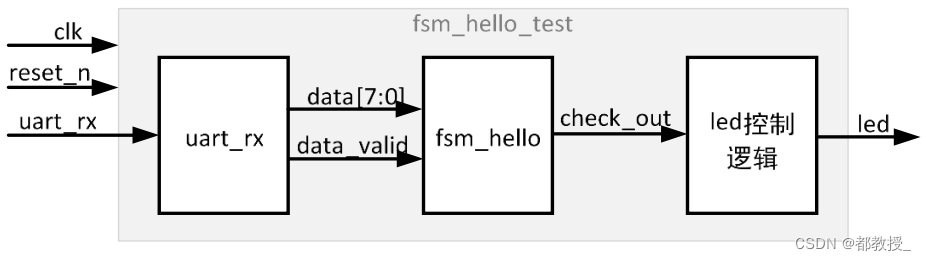

小梅哥Xilinx FPGA学习笔记16——FSM(状态机)的学习

目录 一、 状态机导读 1.1 理论学习 1.2 状态机的表示 1.3 状态机编码 1.4 状态机描述方式 二 、实战演练一(来自野火) 2.1 实验目标 2.2 模块框图 2.3 状态转移图绘制 2.4 设计文件 2.5 仿真测试文件 2.6 仿真结果 三、 实战演练二(来自野火) 3.1 实验目标 3.2 模块框图 3.3 状态转移图绘制 3.4 设计文

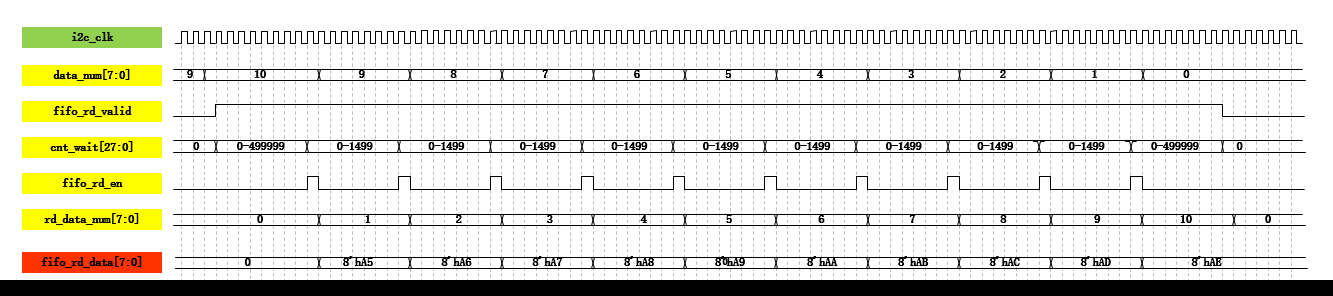

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(2)

FPGA_IIC代码-正点原子 野火 小梅哥 特权同学对比写法(2) 工程目的I2C 单字节写操作I2C 随机读操作EEPROM 字节读写整体框图模块功能简介I2C 驱动模块模块框图跨时钟域处理状态转移图 波形分析单字节写操作局部波形图(一)单字节写操作局部波形图(二)第一部分:输入信号说明 i2c_clk 信号波形图第二部分:时钟信号计数器 cnt_clk 和输出信号 i2c_clk 的设

小梅哥FPGA学习笔记——计数器IP核调用及仿真

计数器IP核调用 计数器IP核使用FPGA设计方式计数器IP核配置Ip核实现到硬件RTL结构 功能仿真IP核调用实现计数器级联 计数器IP核使用 FPGA设计方式 1、原理图输入(不推荐)系统比较大的时候修改十分困难 2、Verilog HDL设计方式 3、IP核输入方式(例如FFT的实现,包括的原理到最终实现,使用verilogHDL进行开发内容多开发周期太长,缩短开发周期)

基于小梅哥Zynq开发板的简易自制示波器(代码已开源)

简介 本程序基于Xilinx zynq 7000系列芯片,结合12位8通道ADC采样芯片ADC128S102,实现了8选1通道的简易示波器功能。代码已开源,下载链接在文章顶部。 一、硬件组成 (1)小梅哥ACZ702-7020开发板 (2)小梅哥FPGA EDA扩展卡 (3)小梅哥5寸电容触摸显示屏 二、系统结构 1.PL部分: (1)将ADC128S102芯片采集的12位ADC数据