信号线专题

Matlab编程技巧:通过脚本获取/修改Simulink信号线参数

上一篇博客《Matlab编程技巧:批量获取/修改Simulink模块参数》中,说明了如果通过matlab脚本批量获取/修改Simulink模块参数。具体方法可以参考https://blog.csdn.net/u013288925/article/details/103943921 Simulink中的信号线也是带有一些属性的,譬如名称和是否关联Simulink Signal Obj。本文介绍几个修

【Altium Designer 20 笔记】隐藏PCB上的信号线(连接线)

使用网络类隐藏特定类型的信号线 如果你想要隐藏特定类型的信号线(例如电源类),你可以首先创建一个网络类。使用快捷键DC调出对象类浏览器,在Net Classes中右击添加类,并重命名(例如为“Power”) 快捷键DC调出对象类浏览器 在创建的网络类中,添加你想要隐藏的网络。 点击面板“Panels”,勾选“PCB”选项。此时,在右侧面板中应能看到你刚刚创建的类(例如“Pow

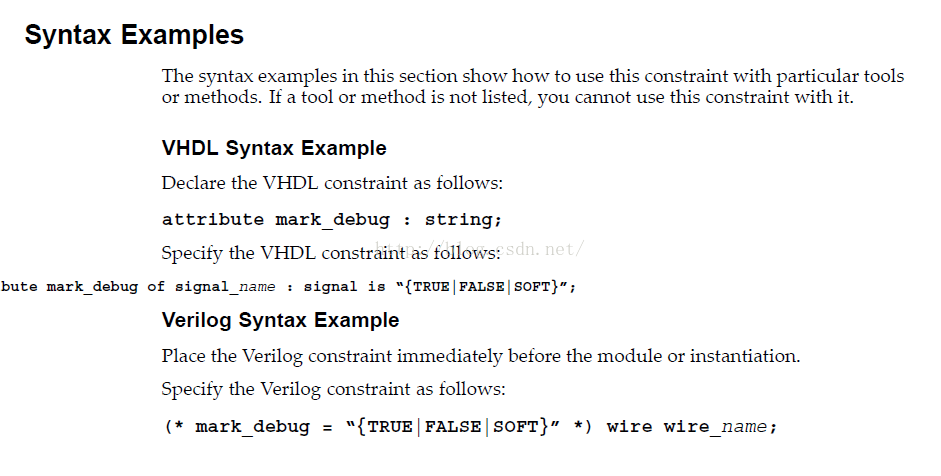

关于xilinx保留信号线不被综合的约束语句

开始在网上一直看到说使用keep语句能够保持信号线不被综合掉,能够调用到chipscope中观察,反正我试了几次是不行,于是就自己看了官网的约束文件,发现,是使用mark——debug语句,然后自己试过了,可用。把图片贴上来和大家共享。

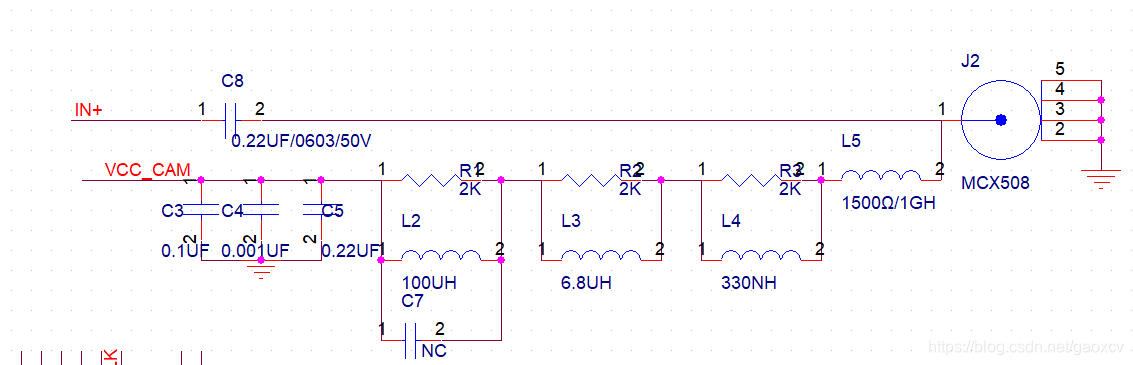

信号线传送power POWER OVER COAX(POC)

TI的方案 4g和2g https://training.ti.com/power-over-coax-poc-design?cu=1134310 https://wenku.baidu.com/view/9653522a58f5f61fb63666a2.html 美信的方案 2g 实际的实验结果,2g-4g 都可以用下面 美信的方案 加一颗 15

Cadence17.2 > Allegro > 检查PCB Layout信号线组等长

目录 第一步:选择Cmgr图标: 第二步:双击Net下面的Relative Propagation Delay 第三步:右键点击Dsn行,选择Analyze,然后就可以看到Length信息了 在使用Allegro进行PCB文件设计时,如果板子相对复杂,检查配线等长和重要信号线成为必备技能,此文章通过简单几步,教你如何快速查看单路或者单组信号线如何查看等长等信息。

信号线多长算长呢——之上升沿与时延的爱恨情仇

忆往昔岁月,看着PCB上弯弯曲曲的走线,看着书中所说的端接,想象着日后自己也可以这么牛逼,能够设计出这么复杂的电路。“过来焊板子啦”一句话又将我拉回了现实,哎,过来吸一会我们硬件攻城狮的精神鸦片——松香吧。 吸完后果然腰也疼了头也晕了连拿碗的手都开始抖了,我觉得我快要成仙了,然后带着我的一身仙气来到了老师傅面前露出我那谄媚的笑容,“老大,咱这板子上面为啥走线是弯弯