串转专题

串转并74hC595控制流水灯

#include <reg51.h> //重新定义系统数据类型 typedef unsigned int u16; typedef unsigned char u8; //宏定义数据端口 #define LEDDZ_COL_PORT P0 #define SER_AP_PORT P1 //定义数据存储端口 sbit SER=P3^4; sbit SRCLK=P3

Verilog面试题(一)——2020乐鑫科技数字IC(串转并、饮料售卖机)

文章目录 题目一:将一个串行执行的C语言算法转化为单拍完成的并行可综合verilog。思路代码知乎数字芯片实验室牛客讨论区 题目二:饮料售卖机思路E课网代码(牛客讨论区) 题目一:将一个串行执行的C语言算法转化为单拍完成的并行可综合verilog。 unsigned char cal_table_high_first(unsigned char value){unsigne

「Verilog学习笔记」数据串转并电路

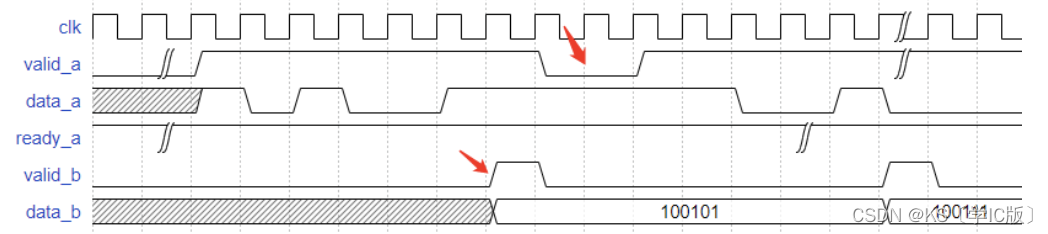

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 关于什么是Valid/Ready握手机制: 深入 AXI4 总线(一)握手机制 - 知乎 时序图含有的信息较多,观察时序图需要注意: data_b是在已接收到6个数据后下一个时钟产生输出; 本模块与上游采用valid_ready握手机制,当valid_a拉低,表示与上游握手未成功,

74HC595串转并

74HC595可以实现串转并功能,从而实现MCU 上 GPIO 的扩展。 其中,74HC595如下图所示: 它用SH_CP接口、DS接口、ST_CP接口 串行输出数据,通过Q0 - Q7 这八个接口并行输出数据。 SH_CP:是串行移位脉冲。每传送一位数据后,这个端口先设为低电平,再设为高电平, 从而形成一个上升沿。表示一个数据传送完毕。 DS:这是用来传数据的口,当为1时,为高电

11.7加减计数器,可置位~,数字钟分秒,串转并,串累加转并,24位串并128,流水乘法器,一些乘法器

信号发生器 方波,就是一段时间内都输出相同的信号 锯齿波就是递增 三角波就是先增后减 加减计数器 当mode为1则加,Mode为0则减;只要为0就输出zero 这样会出问题,因为要求是十进制,但是这里并没有考虑到9之后怎么办,所以就会使number输出超过9,应该额外要添加十进制的边缘判断,即mode为1,要加的时候也要判断一下是不是要继续加,而不是直接加