wr专题

开源框架springboot-mybatis-wr-separation实现springboot+mybatis读写分离

最近做springboot+mybatis的项目想要用到读写分离,查了一圈发现大家都是自己写的,没用通用现成的读写分离架构,因此就写了一个比较简单好用的小插件,来帮助大家简单的实现读写分离的功能,项目已开源并已经上传到maven中央仓库,欢迎提出宝贵意见,共同改进。 springboot-mybatis-wr-separation 介绍 springboot-mybatis-wr-separa

zh150 贴片, WR 弯的,有机械焊盘固定

;FPM skill by Richard L. version=0.08 fpmontreal@gmail.com ;Tree:Connector/Header ;Desc:zh150 贴片, WR 弯的,有机械焊盘固定 ;Vendor: ;Count:20 ;CVG64:bitmap field, not implemented yet. ;Datasheet: Tabs='( (2 3) (

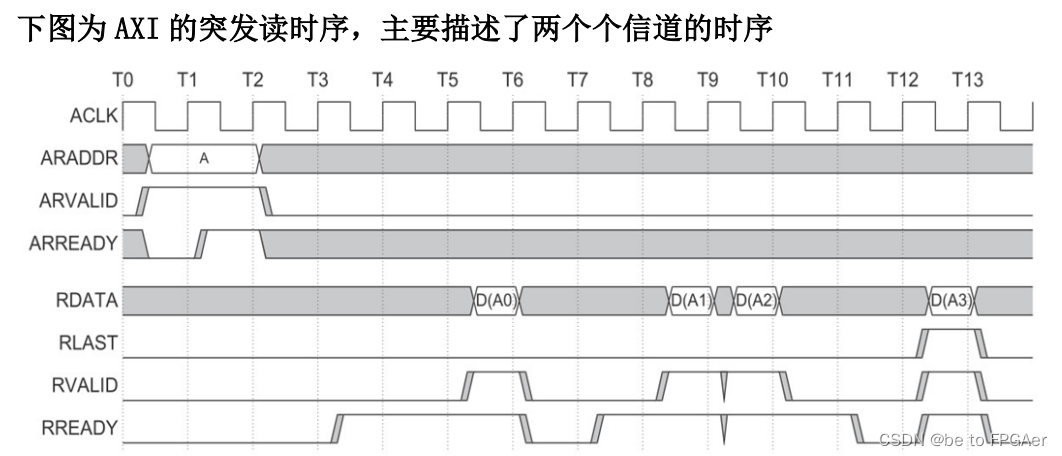

ZYNQ 调用AXI WR RD ip及其代码

首先调用ip 值得注意的是:zynq支持axi4.0 ,但是创建的ip是属于axi3.0,其区别主要是在数据位宽以及突发长度的区别。 下面附读写控制模块(稍作修改就可使用,数据位宽是64bit 突发长度是256): assign fifo_wr_data = {8'd0,pixel_rgb};assign fifo_wr_en = hv;//fifo 2 clock d

格瑞特维推出具有卓越空转承受性的PFA复合材料WR(R) 650

宾夕法尼亚州卡尔普斯维尔--(美国商业资讯)--格瑞特维(Greene Tweed)宣布推出其耐磨(WR)产品组合中的最新热塑复合材料WR® 650。 WR®650采用三维碳纤维结构加固,与领先的PFA基材料相比,具有更高的性能,同时能最大限度地提高设备的可靠性。 WR®650具有出色的空转承受性、优异的耐化学性和最高260°C (500°F)的工作温度。其较高的纤维含量使得这种材

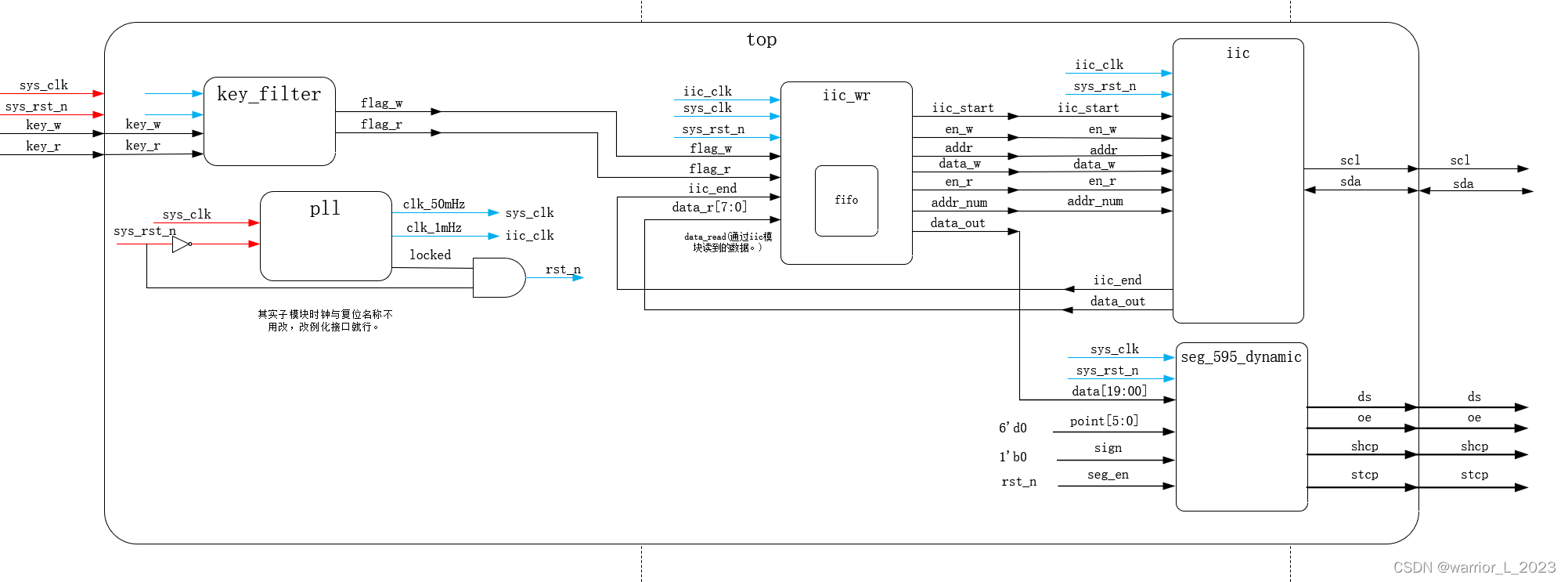

FPGA project : IIC_wr_eeprom

简介: 简单双向二线制,同步串行总线。 scl:串行时钟线,用于同步通讯数据。 sda:双向串行数据线。 物理层: 1,支持挂载多设备。 2,二线制。 3,每个设备有其单独的地址。 4,空闲时,sda会被上拉电阻拉高。 5,存在多个主机时,通过仲裁逻辑决定那个主机控制总线。 6,三个速度模式:标准模式(100kb/s);快速模式(400kb/s);高速模式(3.4Mb/s)

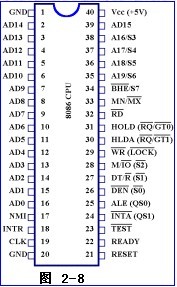

计算机原理WR是什么,8086的引线-微计算机原理-电子发烧友网站

§2.5 8086的引线 本节概述 概念1:有40个引脚,其中地址线有20根,16根分时复用的数据线,还有控制线,如图2-8所示。 某些引脚上的信号,在不同时刻具有不同的意义。例如,AD15~AD0,在某些时候表示地址A15~A0,在另一些时候表示数据D15~D0。 概念2: 8086组成系统时,根据系统规模大小,有两种组态:最小组态(或称最小模式)、最大组态(或称最大模式)。若8086与小容量