vitis2021.1专题

ZynqMP Vitis2021.1 生成hex或者bin文件

比如Cortex™-R5 处理器的Vitis工程生成hex和bin文件。 如下图片中的Command中输入下面内容: armr5-none-eabi-objcopy -O binary ${ProjName}.elf ${ProjName}.bin;armr5-none-eabi-objcopy -O ihex ${ProjName}.elf ${ProjName}.hex 但是由于vi

ZynqMP Vitis2021.1 PS UART接收中断及IDLE(超时)中断

前言: 硬件环境:Xilinx ZynqMP XCZU4EV-SFVC784-1-I 软件环境:Ubuntu20.04LTS + Vivado2021.1 + Vitis2021.1 文章目标:1、UART在正常模式下中断接收的回显例子。 2、Xilinx自带UART库代码有点累赘,在例1基础上优化。 3、在例2的基

ZynqMP Vitis2021.1 生成map文件

参考: https://support.xilinx.com/s/question/0D52E00006iHmHUSA0/map-file-in-sdk?language=en_US 右键c工程,选中c/c++ Build Settings选项。 在下图所示地方添加下面一行,其中test.map可以根据更改生成map文件的名字。 -Wl,-Map,test.map

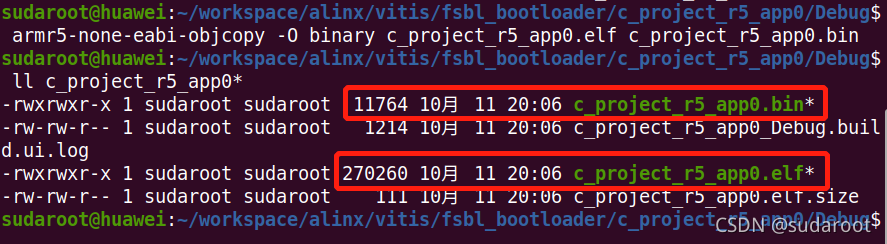

vitis2021.1 armr5-none-eabi-objcopy -O binary elf文件转bin文件变大

把编译的程序文件尾缀elf变成bin文件,编译的是xilinx 4ev R5核的裸机程序。 本来是一件很简单的事情,输入下面命令即可。 armr5-none-eabi-objcopy -O binary c_project_r5_app0.elf c_project_r5_app0.bin 但是编译出来的bin文件无法运行,排查文件大小,发现bin文件变得非常大,比elf文件还大。 很明显