verlog专题

【无标题】verlog中wire 和reg用法

wire(组合逻辑) wire用来连接模块实例化的输入和输出端口; wire用作实际模块声明中输入和输出; wire 元素必须由某些东西驱动,并且在没有被驱动的情况下,无法存储值; wire 元素不能用在 always模块中 = 或者 <= 的左边; wire元素是assign语句左侧 唯一的合法类型; wire 元素是在基于Verilog的设计中连接两片的无状态方式; wire 只能用在 组合

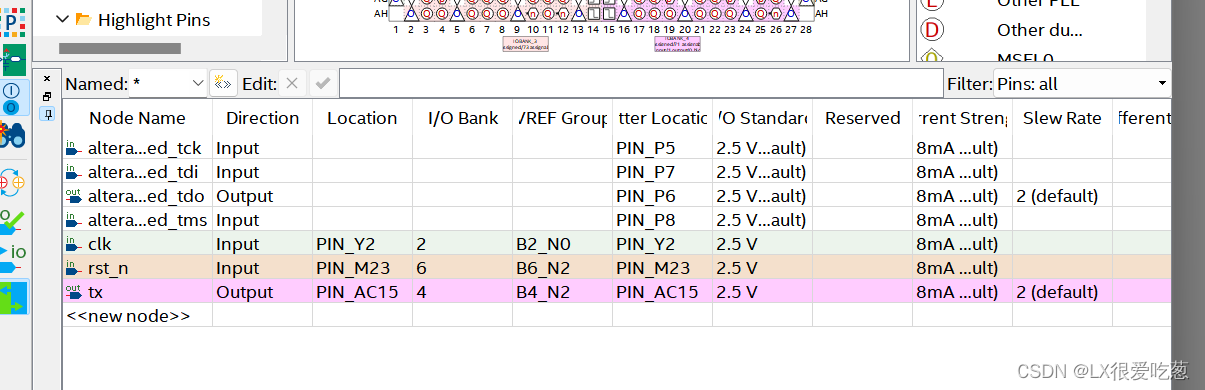

Verlog-串口发送-FPGA

Verlog-串口发送-FPGA 引言: 随着电子技术的不断进步,串口通信已成为嵌入式系统和计算机外设中一种广泛使用的异步通信方式。串口通信因其简单性、可靠性以及对硬件资源的低要求,在数据传输领域扮演着重要角色。在FPGA(现场可编程门阵列)设计中,实现串口通信功能是连接外部处理器和FPGA、实现数据交换的关键技术之一。 本实验旨在通过Verilog语言,设计并实现一个能够在FPGA上运行