tss专题

pmtest5a_b(ring0到ring3_无tss)

文本比较 已生成: 2010-4-9 10:33:29 模式: 全部 左侧文件: C:Documents and Settings66_不思进取桌面下载os6631767673chapter3chapter3epmtest5a.asm 右侧文件: C:Documents and Settings66_不思进取桌面下载os6631767673chapter3chapt

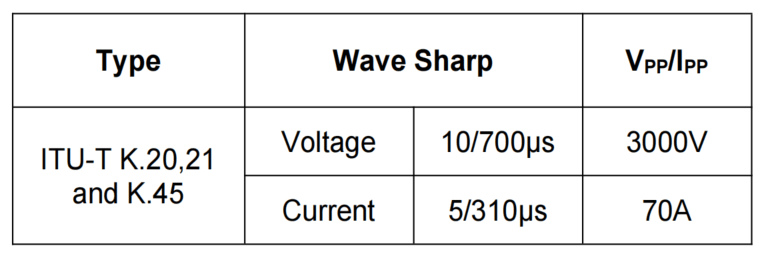

雷卯推荐电磁兼容保护器件-TSS半导体放电管

一、TSS的简介 半导体放电管, 简称TSS。TSS 是根据可控硅原理采用离子注入技术生产的一种新型保护器件,具有精确导通、快速响应(响应时间ns级)、浪涌吸收能力较强、双向对称、可靠性高等特点。 由于其浪涌通流能力较同尺寸的TVS管强,可在无源电路中代替TVS管使用。 但它的导通特性接近于短路,不能直接用于有源电路中,在这样的电路中使用时必须加限流组件,使其续流小于最小维持电流。 半导

手写简易操作系统(八)--特权级以及TSS

前情提要 我们在这里梳理一下上面几节讲的内容 首先是计算机开机,BIOS接过第一棒,将第一个扇区MBR的内容导入到内存 0x7c00 的位置。 然后就是MBR中我们自己写的内容,将Loader导入到 0x600 的地址,Loader设置了GDT,打开了保护模式,并且开启了内存分页。最后将内核载入到内存的 0xc0001500 的位置,也就是物理内存 0x1500 的位置。 这一节没有代码,

x86中的TSS与任务切换

前言 今天在学习《深入理解Linux内核》的时候,发现出现了一个新的名词TSS(Task-State Segment),这还是我第一次了解到原来x86提供了硬件级别的任务切换功能,之前以为任务切换都是操作系统实现的来着,这里也记录一下我的发现。 参考资料 Intel白皮书的Volume 3A Chapter 8: Task Management 什么是TSS TSS是一块特殊的内存区域,

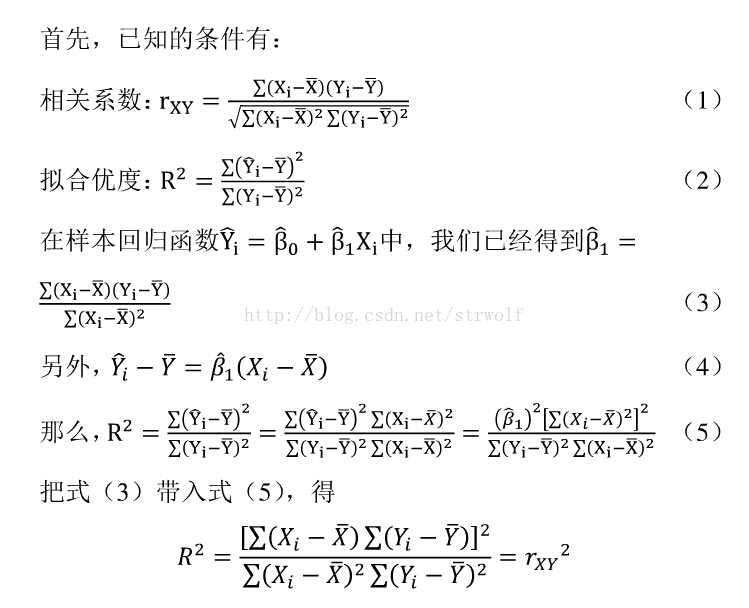

2017.05.19回顾 TSS = ESS + RSS证明

1、对风控描述文档进行了修改,交付给了相关同事 2、然后就是把Ken的接口加入到合作方决策引擎中,没什么问题,还是老套路,只是对于AS前置模型的情况进行了一些小处理 3、下午我记得还Henry微信沟通了一下,放宽了AS某个渠道的客户 4、下午还研究了手机三要素的问题,发现根本就没拉3A的手机三要素,然后又是一番沟通,过程中也了解到3A的一些库表结构 5、下午的另外一半时间都是集中在领悟线性

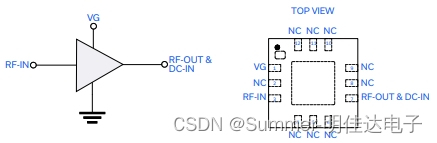

适合无线通信设备应用 TSS-53LNB+、TSS-53LNB3+、TSS-183A+、TSS-13LN+、TSS-23LN+低噪声、增益放大器【RF】

1、TSS-53LNB+ 射频放大器 IC 通用 500MHz 至5GHz,12MCLP TSS-53LNB+(符合RoHS标准)是一款先进的超平坦增益低噪声宽带放大器,采用E-PHEMT技术制造,在宽频率范围内提供极高的动态范围。它集成了开关,使用户能够在高信号条件下旁路放大器。此外,TSS-53LNB+在宽频率范围内具有良好的输入和输出回损,无需外部匹配元件。它采用12引脚3x3 mm

matlab GOCI水色数据画TSS变化过程+批量读取.he5文件

下载地址: http://kosc.kiost.ac.kr/eng/ clear all;close all;clc%% 读取经纬度file='COMS_GOCI_L2P_GA_20110524031644.LON_1.he5';LON=h5read(file,'/HDFEOS/GRIDS/Image Data/Data Fields/Longitud

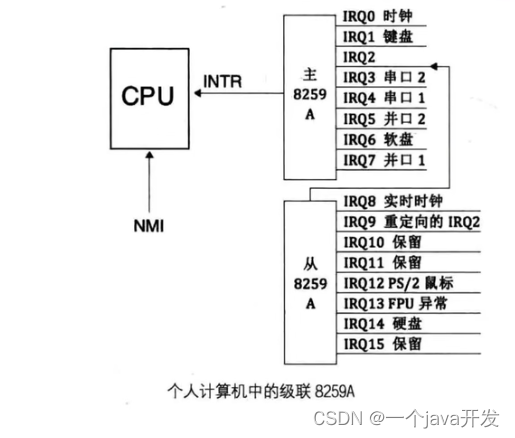

自制OS3-1到3-16==保护模式(GDT、选择子、寄存器)、多任务由来(LDT)、内核态和用户态ring0和ring3、特权级切换(TSS-CPL-DPL-RPL-门)、时钟中断、保护模式中断编程

保护模式 前面我们可以任意的访问内存,寄存器在段式内存中,其实没有界限,操作系统和用户程序实际上做不到内存的隔离。 用户程序所访问的逻辑地址,实际上就是物理地址。 用户程序可以随意修改段基址(mbr es=7c00 loader=b800) 保护模式将16位寄存器扩展到了32位 向下兼容,原先得段+偏移这种编程寻址结构,不破坏这种结构。 INTEL专门设计了一个数据结构来描述这个

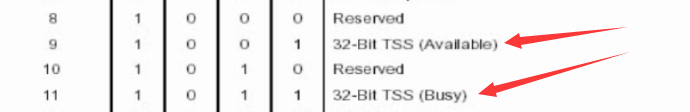

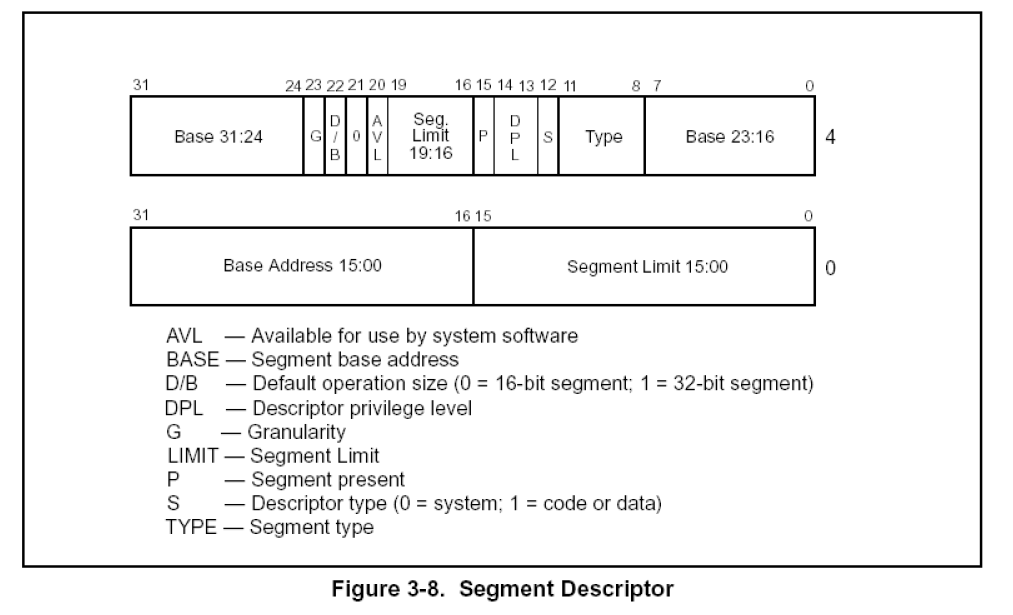

GDT、LDT,TSS、段选择子、段描述符

大家好,我叫徐锦桐,个人博客地址为www.xujintong.com。平时记录一下学习计算机过程中获取的知识,还有日常折腾的经验,欢迎大家来访。 在32位操作系统保护模式下,所有的内存访问都要通过GDT(全局描述符表)或者LDT(局部描述符表),GDT和LDT就是存储各种段描述符的一个表,而从GDT或LDT中找到进程对应的段描述符就需要段选择子了。 段描述符 段描述符就是一段内存的地址位

浪涌防护:TSS管的工作原理与应用?|深圳比创达EMC

浪涌防护:TSS管的工作原理与应用?相信不少人是有疑问的,今天深圳市比创达电子科技有限公司就跟大家解答一下! 一、TSS工作原理 TSS半导体放电管是一种电压开关型瞬态抑制二极管,即涌压抑制晶体管,或称为导体放电管、固体放电管等。也称浪涌抑制晶闸管,是一种采用半导体工艺制成的PNPN结四层结构器件, 当外加电压低于断态电压时,器件处于断开状态;当电压超过它的断态峰值电压时,半导体放电管会将瞬

tss linux进程切换,x86体系下Linux中的任务切换与TSS

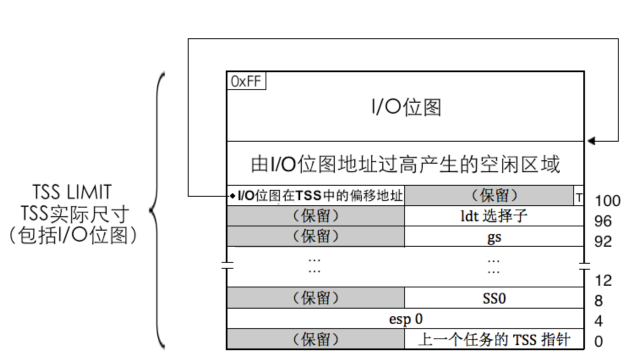

tss的作用举例:保存不同特权级别下任务所使用的寄存器,特别重要的是esp,因为比如中断后,涉及特权级切换时(一个任务切换),首先要切换栈,这个栈显然是内核栈,那么如何找到该栈的地址呢,这需要从tss段中得到,这样后续的执行才有所依托(在x86机器上,c语言的函数调用是通过栈实现的)。只要涉及地特权环到高特权环的任务切换,都需要找到高特权环对应的栈,因此需要esp2,esp1,esp0起码三个e

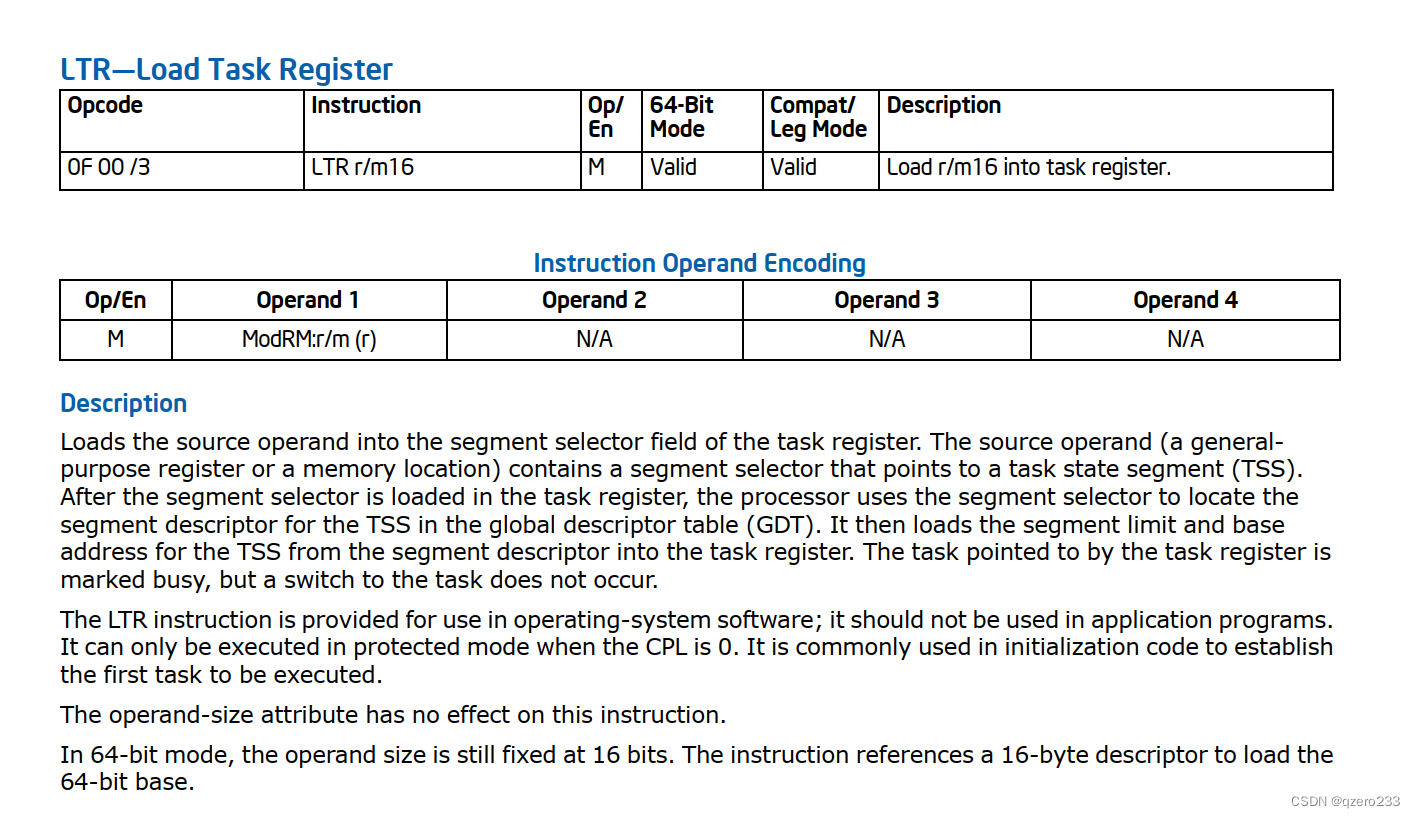

[转](15)TSS,TR寄存器,TSS描述符,任务段跳转实验

一、TSS,TR寄存器,TSS门描述符的关系 首先,通过下图,了解 TSS,TR寄存器,TSS描述符的关系: TSS(Task-state segment)是一块104字节的内存,用于存储大部分寄存器的值; TSS设计出来的目的是任务切换,或者说是一次性替换一大堆寄存器。 TR寄存器存储了TSS的地址,大小,和TSS门描述符选择子; TSS

(7) [保护模式]任务段 (TSS)

文章目录 TR寄存器TR寄存器的作用任务段描述符TSS (任务段)使用任务段修改寄存器的值jmp far 和 call far 的不同拓展 TR寄存器 说到TSS就不得不提TR寄存器了 TR段寄存器依然是指向一个段描述符,但是是一个比较特殊的描述符,我们称之为任务段描述符 TR寄存器的作用 书中表示栈的方式与OD表示的方式刚好相反 TR 寄存器中的selector查找

TSS(任务状态段) TSS描述符 任务寄存器(TR) 任务门描述符 学习总结

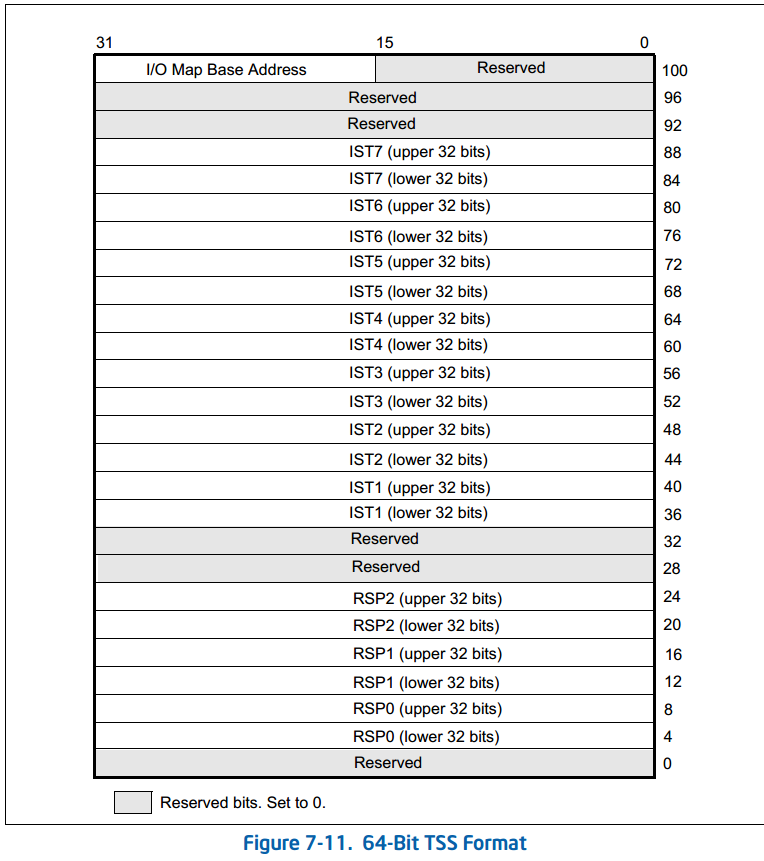

主要是TSS、TSS描述符、TR和任务门描述符学习总结 1 任务状态段(TSS) 任务状态段(Task-State Segment(TSS)),保存任务状态信息的系统段为任务状态段。图7-2描述32位CPU的TSS信息。TSS主要分为动态字段和静态字段。 在任务切换过程中当任务挂起时,处理器会更新动态字段,动态字段有: (1)通用寄存器字段—任务切换之前,EAX,ECX,EDX

TSS,TR寄存器,TSS描述符,任务段跳转实验](https://img-blog.csdnimg.cn/20201002100631684.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L0t3YW5zeQ==,size_16,color_FFFFFF,t_70#pic_center)

![(7) [保护模式]任务段 (TSS)](https://img-blog.csdnimg.cn/93a3f2f497004a99b2d7bd071919228d.png)