synopsys专题

Synopsys dc-2010-sp5-3安装过程(上)

1安装dc的目的 老板让自己调研加密电路这一块,需要使用到dc,奈何,只能自己找网上的破解的版本,找到了,安装成功。分享给大家,祝大家好运! 说明,本教程在ubuntu14.04amd64位下验证成功,安装的版本是D-2010.03-SP5-3.在以下文档中,由于笔者之前已经安装成功过一次 ,所以这里在用户目录下新建位soft1,用户在安装的时候,可以自由替换这个名称,安装过程要注意的

synopsys EDA自学指南

最好的自学资料永远是厂家的datasheet,user guide,在solvenet:https://solvnetplus.synopsys.com/s/注册账号,下载安装软件,在document中找到想要学习软件的user guide,一般都会有软件学习example lab,跟着做一遍基本就入门了。 还有一个找资料最好的地方就是软件的安装目录,以VCS为例,找到$VCS_HOME/doc

synopsys工具安装系列(一)安装installer

synopsys为eda工具安装,提供了一个安装器,名叫installer。所以,首先要先安装installer这个工具,之后才能安装其他的eda工具。 首先从官网下载该installer工具。我这里下载的是5.2版本 下载之后,有如下安装文件。 将该安装包,拷贝到linux服务器中。 首先给SynopsysInstaller_v5.2.run赋予可执行权限。 chmod a+x Syn

Synopsys IC设计以及其他开发工具需要的ubuntu简单配置

为了学习IC设计,我要用到synopsys,这套软件需要在linux环境下运行,因此我用一台电脑单独装了ubuntu22.04系统。而ubuntu的配置加上Synopsys安装过程十分曲折,因此在此简单记录一下,以便有人遇到类似问题可以借鉴解决方法。 搜狗输入法 原系统的输入法不好用,打字还得是搜狗。 参看这里https://pinyin.sogou.com/linux/help.php

如何使用Synopsys VCS在Vivado中编译库并执行仿真

本文首发于hifpga.com vivado中的仿真库和模型与ISE中的是不一样的,因此在vivado中使用VCS进行仿真的方法也与ISE中不一样。 VCS可以通过两种方法对XILINX的器件进行功能仿真和门级仿真,这两种方法是 Precompiled(预编译) Dynamic(动态调用)。 与ISE相比有以下不同: vivado现在UNISIM库同时包含功能和时序仿真模型vivado参数

数字IC学习记录之数字IC前端 synopsys工具介绍

简述 简单总结下目前IC前端设计使用的一些开发软件(Synopsys公司)。 1. scl 许可管理的 2.VCS( verilog compiled simulator ) Verilog 编译仿真器,现在公司主流的仿真器,和windows下modelsim一样的作用。 3.Verdi/dve verdi是比较强大的debug工具,两个基本波形查看工具 4.DC( Design

synopsys license破解及使用遇到的难题总结

synopsys license破解 use daemon;决定license使用的时候,是否需要lmgrd启动。 RHEL linux下安装 license生效时,不要随便调整系统时间。特别是不要把时间提前。否则license会检测到,并认为license非法。lmgrd/snpslmd,两个命令,与license有关。最好是选择一个版本(比如一个工具下的),而且是版本尽量高。lice

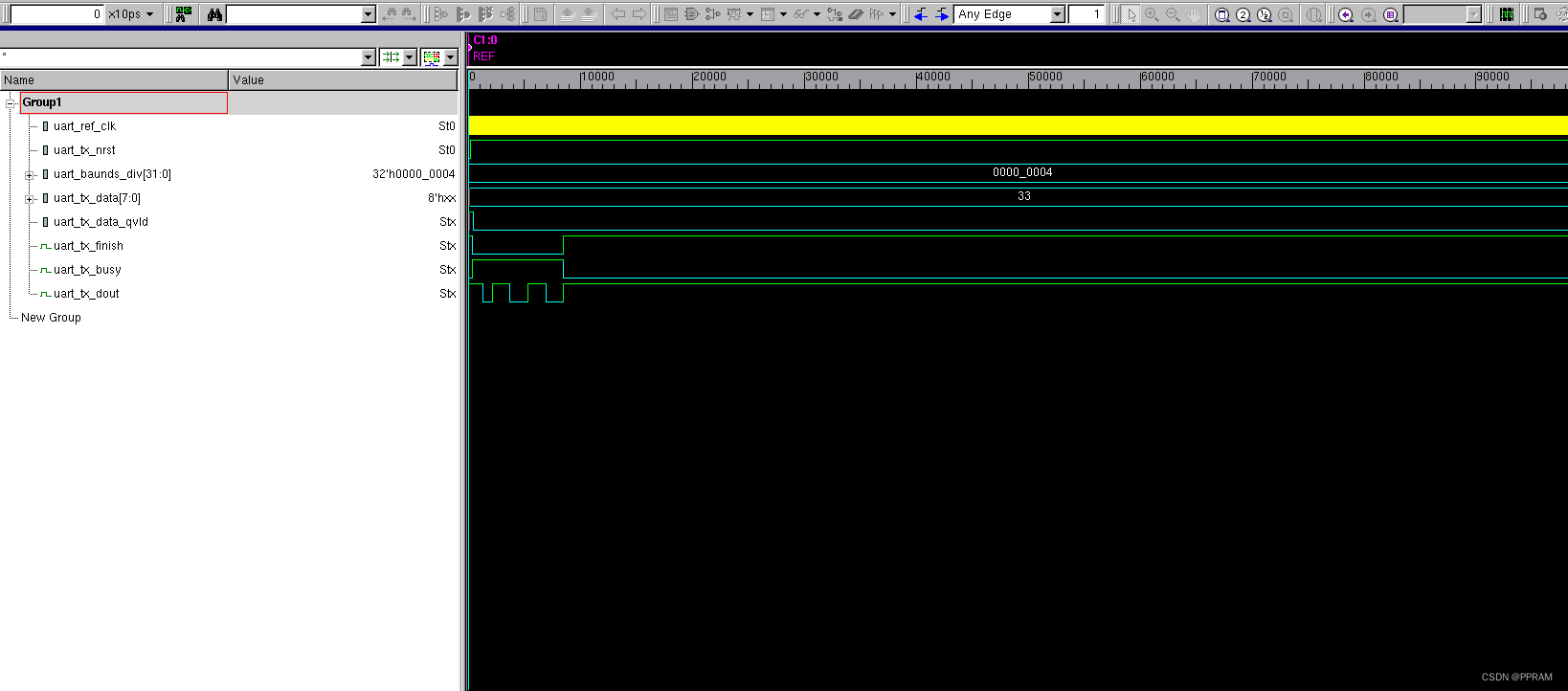

【Synopsys工具使用】VCS使用与Makefile脚本调用

文章目录 一、文件导入二、VCS仿真(使用可视化界面)三、VCS仿真(使用Maefile文件)3.1 Makefile文件编写3.2 仿真文件编写规范3.3 Makefile文件使用 一、文件导入 新建一个文件夹新建一个文件夹(图中IC_work) 创建一个目录,用来存放文件(图中test) 将要操作的文件复制到文件夹下: 此时打开终端,输入命令ls可以查看文

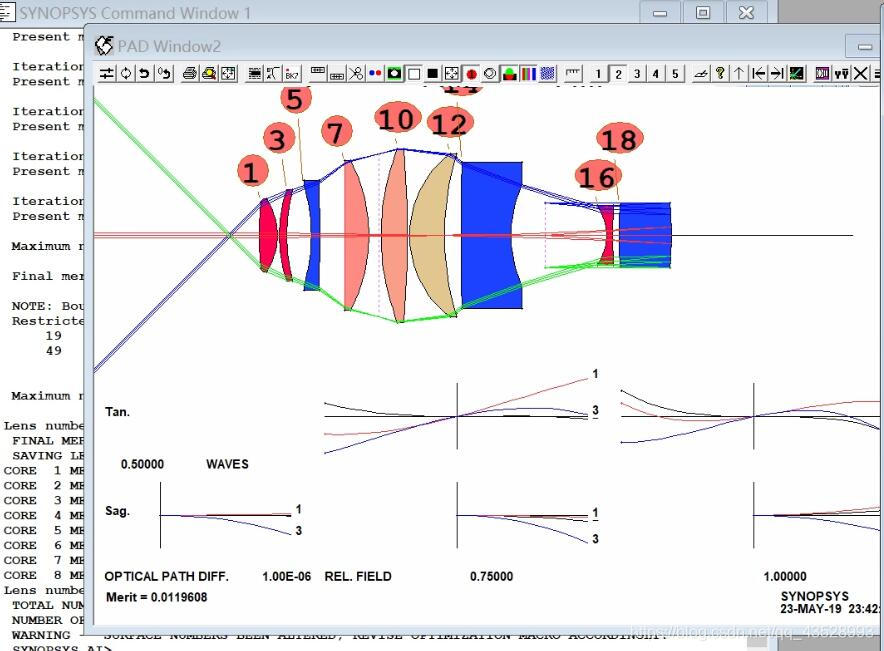

Design Compiler总结(Synopsys)

Design Compiler总结(Synopsys) 作用:RTL 优化过的netlist(logic Circuit)。synthesis flow:synthesis = translation + logic optimization + gate mappinglab流程--两种工作模式:脚本和图形化界面图形化界面操作:report分析 作用:RTL 优化过的netlis