mmcm专题

Xilinx 7系列MMCM/PLL端口简介

在FPGA设计中,MMCM和PLL的端口允许设计者进行各种配置,包括设置时钟源的选择、分频系数、相位偏移等参数。此外,这些端口还可以提供时钟信号的状态信息,如是否锁定、频率误差等,以便设计者进行监控和调试。 具体的端口包括: 1、CLKIN1 - 主参考时钟输入 可以由同一局部时钟域内的SRCC或MRCC I/O直接驱动,也可以通过CMT主干线由垂直相邻时钟区域内的SRCC或MRCC I/O驱

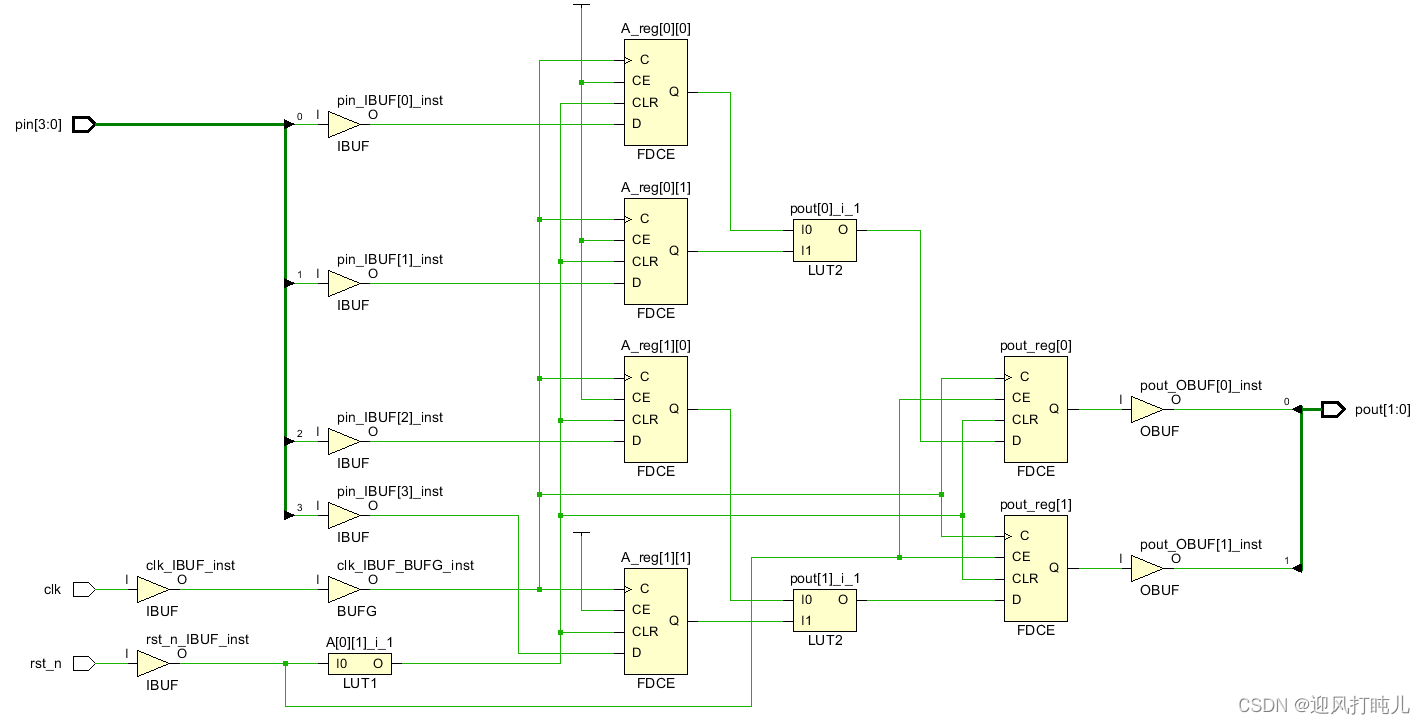

vivado里的LUT、LUTRAM、FF、BRAM、DSP、IO、BUFG、MMCM资源介绍

vivado里的LUT、LUTRAM、FF、BRAM、DSP、IO、BUFG、MMCM资源介绍 提示:以下是本篇文章正文内容,写文章实属不易,希望能帮助到各位,转载请附上链接。 vivado实现电路用到的资源类型 LUT(Look-Up Table):查找表,它接收一组输入信号,并根据预先定义的逻辑函数表(Look-Up Table)输出结果,LUT 可以实现任意逻辑函数,如与、或