m2014专题

HDLbits 刷题 -- Exams/m2014 q3

Consider the function f shown in the Karnaugh map below. Implement this function. d is don't-care, which means you may choose to output whatever value is convenient. 译:考虑下面卡诺图中显示的函数f。 实现这个函数。D是

HDLbits 刷题 --Exams/m2014 q4i

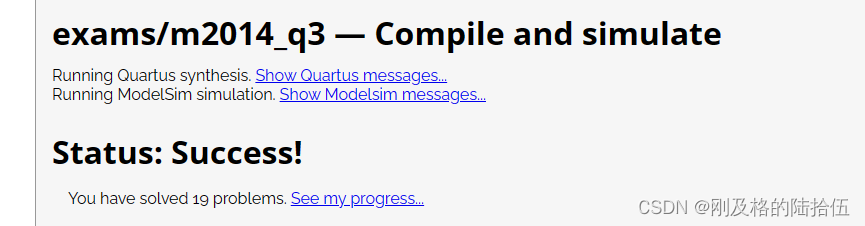

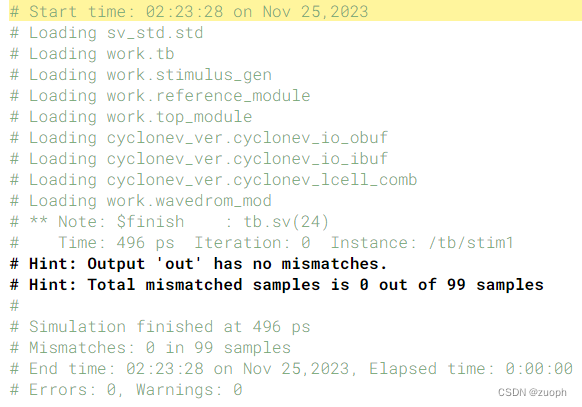

Implement the following circuit: 实现以下电路: module top_module (output out);assign out = 1'b0;endmodule 运行结果:

hdlbits系列verilog解答(exams/m2014_q4f)-47

文章目录 一、问题描述二、verilog源码三、仿真结果 一、问题描述 实现以下电路: 二、verilog源码 module top_module (input in1,input in2,output out);assign out = in1 & (~in2);endmodule 三、仿真结果 转载请注明出处!

hdlbits系列verilog解答(exams/m2014_q4g)-48

文章目录 一、问题描述二、verilog源码三、仿真结果 一、问题描述 本次我们将一次创建多个逻辑门,对两个输入a和b通过组合逻辑实现七种不同的输出: out_and: a and bout_or: a or bout_xor: a xor bout_nand: a nand bout_nor: a nor bout_xnor: a xnor bout_anotb: a

HDLbits: ece241 2013 q12 // Exams/m2014 q4k

两道题目,有一样的问题: 第一道:ece241 2013 q12 下面的代码错误,一直没看出来哪里有问题: module top_module (input clk,input enable,input S,input A, B, C,output Z ); reg [7:0] q;dff dff_1(clk,enable,S,q[0]);dff dff_2(clk,enable,q[0]