lvdsspi专题

【AD9361 数字接口CMOS LVDSSPI】C 并行数据 LVDS

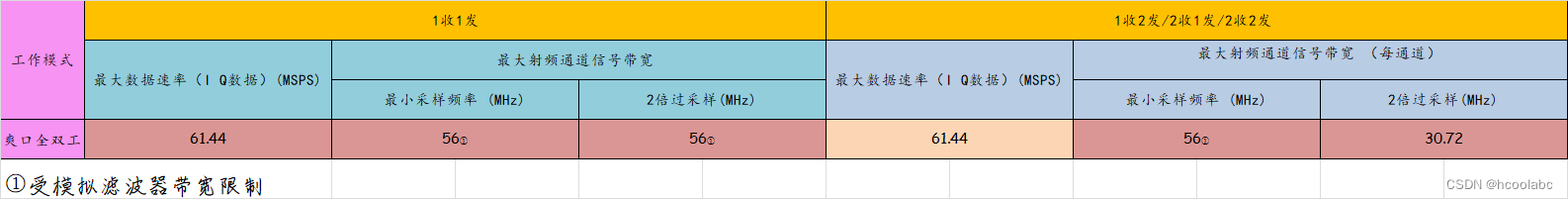

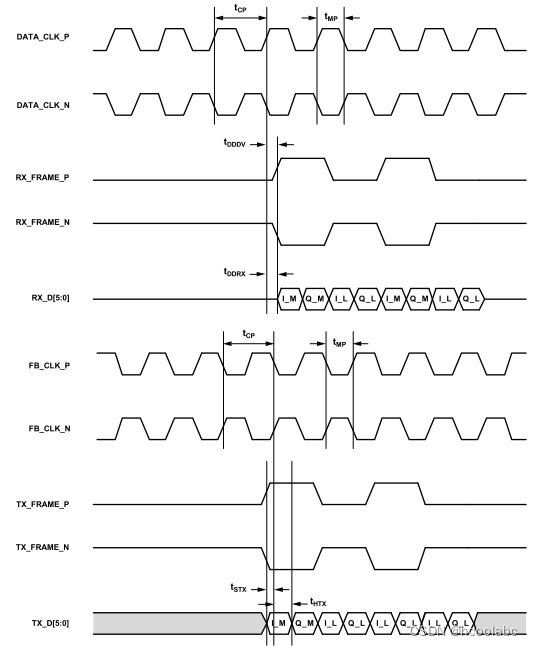

接上一部分,AD9361 数字接口CMOS &LVDS&SPI 目录 一、LVDS模式数据路径和时钟信号LVDS模式数据通路信号[1] DATA_CLK[2] FB_CLK[3] Rx_FRAME[4] Rx_D[5:0][5] Tx_FRAME[6]Tx_D[5:0][7] ENABLE[8] TXNRX系列 二、LVDS最大时钟速率和信号带宽 一、LVDS模式数据路径和时钟信号

【AD9361 数字接口CMOS LVDSSPI】C 并行数据 LVDS <续>

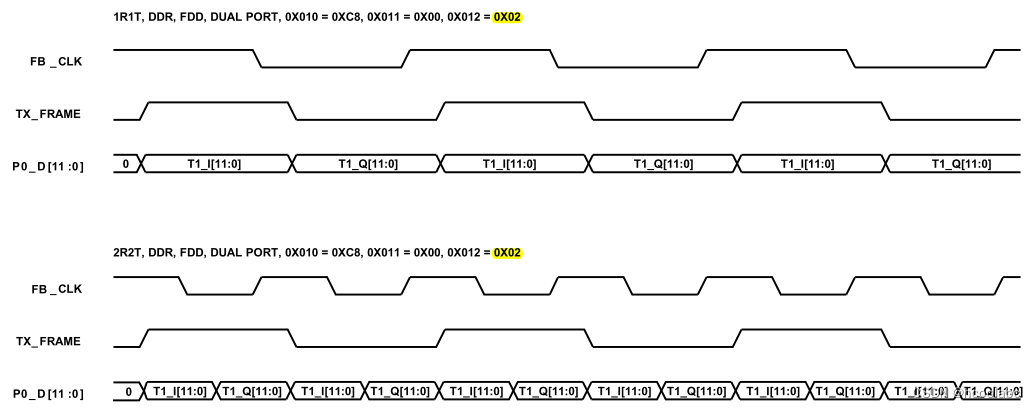

续【AD9361 数字接口CMOS &LVDS&SPI】C 并行数据之LVDS 不同于CMOS的传输方式,lvds只能工作在双端口全双工模式下。 一、 双端口全双工模式 (LVDS)代称 DFL DUAL PORT FULL DUPLEX MODE DFL 模式通过写入SPI寄存器实现。在此模式下,P0 和 P1 均作为 LVDS 信号使能,数据总线 (D[11:0]) 被拆分为单独的子总线

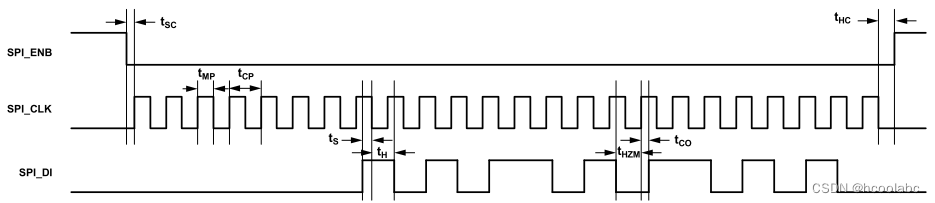

【AD9361 数字接口CMOS LVDSSPI】D 串行数据 SPI

【AD9361 数字接口CMOS &LVDS&SPI】D部分 接续 【AD9361 数字接口CMOS &LVDS&SPI】A 并行数据CMOS 串行外设接口(SPI) SPI总线为AD9361的所有数字控制提供机制。每个SPI寄存器的宽度为8位,每个寄存器包含控制位、状态监视器或其他控制器件所有功能的设置。以下介绍此接口的细节。 SPI功能层 可以通过在SPI配置寄存器中设置位值来配置SP

【AD9361 数字接口CMOS LVDSSPI】A 并行数据之CMOS

〇、综述 本章介绍并行数据端口(P0_D P1_D)和串行外设接口(SPI),用于在AD9361和BBP之间传输数据和控制/状态信息。 下图显示了这些接口,并提供了AD9361和BBP在宽带无线系统中的使用方式的高级视图。数据接口工作在两种模式之一:标准CMOS兼容模式或低压差分信号(LVDS)兼容模式。每个接口都具有以下各节中所述的独特特征。 使用 CMOS 模式时 • 保持单端CMOS

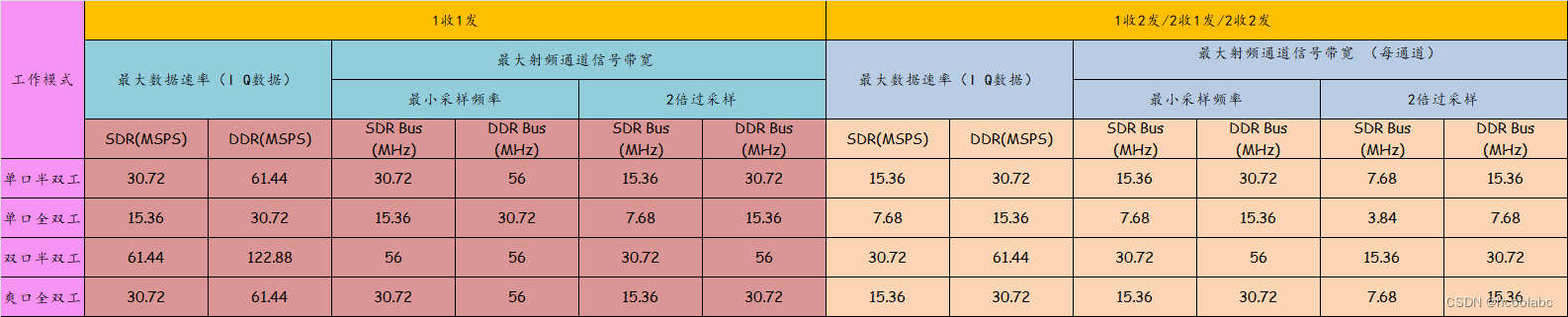

【AD9361 数字接口CMOS LVDSSPI】B 并行数据之CMOS

##接上一篇; 本节介绍 AD9361 数字接口CMOS &LVDS&SPI最后一张表中四种工作模式的具体配置及时序波形图。 目录 1、单端口半双工模式 (CMOS) *代称 SHC*换句话说,最大值是12‘b0111_1111_1111,即0x7FF,最小值的数字量是12‘b0111_1111_1111,即 0x800。这里提个问题,byte的范围是 -127~127 ? 还是 -128